Abstract

As far as ultra-dense crossbars are related to correspondingly dense wire arrays, the crossbar route to tera-scale integration depends on the availability of preparation techniques for wire arrays with density of 106 cm−1 or more. This linear density implies, for a planar arrangement, a pitch of 10 nm or less, which not only is at the limits of the current technical possibilities, but also can modify appreciably the band structure of silicon. A dramatic increase of density could only be achieved if it were possible to organize the nanowires in a three-dimensional fashion still exploiting the planar technology. In this work processes are described for the fabrication of out-of-plane, vertically arranged, polycrystalline silicon nanowires via a rigorously top-down batch process. These techniques are consistent with the production of wire arrays with linear density (projected on the surface) larger than that achievable with any other proposed top-down process. Used for the fabrication of the bottom wire arrays of crossbars, these processes should eventually allow a cross-point amount per unit area in excess of 1012 cm−2, thus providing candidate technologies for ultra tera scale integration. The technique developed for such out-of-plane crossbars can be used to implement new functions like coils, solenoids and transformers.

Similar content being viewed by others

Notes

With GSI (giga-scale integration), TSI and so on, one intends the ability to integrate 109, 1012 etc. switching elements in the same chip. Generally, the chip area of complex circuits is slightly larger than 1 cm2, so that the above numbers are also a (slight) overestimate of the amount per square centimetre. Since the interest of this work is also addressed to the preparation of complex but small circuits (e.g. with total area of 102 μm2), I instead assume that acronyms GSI, TSI etc. denote the ability to batch fabricate at the density of 109, 1012 cm−2 etc. Unless otherwise specified, ‘density’ will henceforth be the short form of ‘areal density’.

Without pretending to consider economic problems, I recall that the cost of an apparatus for deep-ultraviolet lithography is about 30 M$. The low throughput of electron-beam lithography is due to the fact that this technique defines the pattern in a serial way and the throughput varies with the feature size F roughly as F 4 [51].

This estimate follows from assuming the whole mankind as potential consumer, that the swarm is formed by 105 agents and that they have a clearance time of 1 year [67].

Actually also the CMOS technology is characterized, for the preparation of interconnects, by the repetition of the same process. However, although the complexity of an interconnection layer is presumably much lower than that of a crossbar, the CMOS technology has been involved in the reduction of the number of interconnecting layers via the use of insulators with lower dielectric constant than SiO2 and conductors with higher electrical conductivity than aluminium.

The progress of electronics is paced not only by the continuous improvements of its basic technology (lithography) that have reduced the feature size from the submillimetre length scale to the deep- submicrometre one, but also (and at the beginning mainly) by the invention of techniques for the self-alignment of one layer with respect to another. Among them the most important ones are the spacer-patterning technique (for the self-alignment of contacts with respect to the gate), local oxidation of silicon (for the self-alignment of active zones with respect to the field) and silicon-gate technology (for the self-alignment of source and drain with respect to the gate).

History is sparing of compliments to scientists, and even more to technologists: although everybody of the one hundred thousand researchers involved in silicon-device processing is familiar with the silicon-gate technology, the paper reporting its invention in 1968 [71] and the one describing its practical application one year later [72] have had, according to the Institute of Scientific Information, 112 and 42 quotations only [73].

References

G.F. Cerofolini, Appl. Phys. A 86, 23 (2007)

G.F. Cerofolini, Appl. Phys. A 86, 31 (2007)

R.P. Feynman, Eng. Sci. 23(5), 22 (1960)

E. Bussola, What is a memory, that it may comprehend itself? in Memory Mass Storage, ed. by G. Campardo, F. Tiziani, M. Iaculo (Springer, Berlin, 2011), pp. 1–58

E. Drexler, Nanosystems—Molecular Machines, Manufacturing and Computation (Wiley, New York, 1992)

J.R. Heath, P.J. Kuekes, G.S. Snider, R.S. Williams, Science 280, 1716 (1998)

M. Forshaw, R. Stadle, D. Crawley, K. Nikolić, Nanotechnology 15, S220 (2004)

G.S. Snider, R.S. Williams, Nanotechnology 18, 035204 (2007)

G.F. Cerofolini, E. Romano, Appl. Phys. A 91, 181 (2008)

G. Csaba, P. Lugli, IEEE Trans. Nanotechnol. 8, 369 (2009)

G.F. Cerofolini, D. Mascolo, Semicond. Sci. Technol. 21, 1315 (2006)

G.F. Cerofolini, V. Casuscelli, A. Cimmino, A. Di Matteo, V. Di Palma, D. Mascolo, E. Romanelli, M.V. Volpe, E. Romano, Semicond. Sci. Technol. 22, 1053 (2007)

J.C. Love, L.A. Estroff, J.K. Kriebel, R.G. Nu, G.M. Whitesides, Chem. Rev. 105, 1103 (2005)

M.A. Reed, J. Chen, A.M. Rawlett, D.W. Price, J.M. Tour, Appl. Phys. Lett. 78, 3735 (2001)

Y. Luo, C.P. Collier, J.O. Jeppesen, K.A. Nielsen, E. Delonno, G. Ho, J. Perkins, H.-R. Tseng, T. Yamamoto, J.F. Stoddart, J.R. Heath, Chem. Phys. Chem. 3, 519 (2002)

R.F. Service, Science 302, 556 (2003)

D.R. Stewart, D.A.A. Ohlberg, P. Beck, Y. Chen, R.S. Williams, J.O. Jeppesen, K.A. Nielsen, J.F. Stoddart, Nano Lett. 4, 133 (2004)

C.N. Lau, D.R. Stewart, R.S. Williams, D. Bockrath, Nano Lett. 4, 569 (2004)

N.B. Zhitenev, W. Jiang, A. Erbe, Z. Bao, E. Garfunkel, D.M. Tennant, R.A. Cirelli, Nanotechnology 17, 1272 (2006)

G.F. Cerofolini, Nanoscale Devices. Fabrication, Functionalization, and Accessibility from the Macroscopic World (Springer, Berlin, 2009)

J.E. Green, J.W. Choi, A. Boukai, Y. Bunimovich, E. Johnston-Halperin, E. Delonno, Y. Luo, B.A. Sheriff, K. Xu, Y.S. Shin, H.-R. Tseng, J.F. Stoddart, J.R. Heath, Nature 445, 414 (2007)

H.B. Akkerman, P.W.M. Blom, D.M. de Leeuw, B. de Boer, Nature 441, 69 (2006)

G.F. Cerofolini, G. Arena, M. Camalleri, C. Galati, S. Reina, L. Renna, D. Mascolo, V. Nosik, Microelectron. Eng. 81, 405 (2005)

G.F. Cerofolini, G. Arena, M. Camalleri, C. Galati, S. Reina, L. Renna, D. Mascolo, Nanotechnology 16, 1040 (2005)

G.F. Cerofolini, G. Ferla, J. Nanopart. Res. 4, 185 (2002)

G.F. Cerofolini, C. Galati, S. Reina, L. Renna, Semicond. Sci. Technol. 18, 423 (2003)

M.P. Stewart, F. Maya, D.V. Kosynkin, S.M. Dirk, J.J. Stapleton, C.L. McGuiness, D.L. Allara, J.M. Tour, J. Am. Chem. Soc. 126, 370 (2004)

G.F. Cerofolini, C. Galati, S. Reina, L. Renna, G.G. Condorelli, I.L. Fragalà, G. Giorgi, A. Sgamellotti, N. Re, Appl. Surf. Sci. 246, 52 (2005)

T. He, J. He, M. Lu, B. Chen, H. Pang, W.F. Reus, W.M. Nolte, D.P. Nackashi, P.D. Franzon, J.M. Tour, J. Am. Chem. Soc. 128, 14537 (2006)

M.Y. Bashouti, R.T. Tung, H. Haick, Small 23, 2761 (2009)

G.W. Burr, M.J. Breitwisch, M. Franceschini, D. Garetto, K. Gopalakrishnan, B. Jackson, B. Kurdi, C. Lam, L.A. Lastras, A. Padilla, B. Rajendran, S. Raoux, R.S. Shenoy, J. Vac. Sci. Technol. B 28, 223 (2010)

S.R. Ovshinsky, Phys. Rev. Lett. 21, 1450 (1968)

R.G. Neale, D.L. Nelson, G.E. Moore, Electronics 49(9), 56 (1970)

G.F. Cerofolini, L. Meda, Phys. Rev. B 36, 5131 (1987)

G.F. Cerofolini, L. Meda, C. Volpones, J. Appl. Phys. 63, 4911 (1988)

A.C. Pierre, G.M. Pajonk, Chem. Rev. 102, 4243 (2002)

G. Dearnaley, A.M. Stoneham, D.V. Morgan, Rep. Prog. Phys. 33, 1129 (1970)

L. Chua, IEEE Trans. Circuit Theory CT-18, 507 (1971)

D.B. Strukov, G.S. Snider, D.R. Stewart, S.R. Williams, Nature 453, 80 (2008)

R. Waser, M. Aono, Nat. Mater. 6, 833 (2007)

R. Waser, R. Dittmann, G. Staikov, K. Szot, Adv. Mater. 21, 2632 (2009)

G.F. Cerofolini, A. Giussani, A. Modelli, D. Mascolo, D. Ruggiero, D. Narducci, E. Romano, Appl. Surf. Sci. 254, 5781 (2008)

G.F. Cerofolini, C. Galati, L. Renna, Surf. Interface Anal. 35, 968 (2003)

G.F. Cerofolini, C. Galati, S. Lorenti, L. Renna, O. Viscuso, C. Bongiorno, V. Raineri, C. Spinella, G.G. Condorelli, I.L. Fragala, A. Terrasi, Appl. Phys. A 77, 403 (2003)

R. Beckman, E. Johnston-Halperin, Y. Luo, J.E. Green, J.R. Heath, Science 310, 465 (2005)

N.A. Melosh, A. Boukai, F. Diana, B. Gerardot, A. Badolato, J.R. Heath, Science 300, 112 (2003)

M. Roukes, Sci. Am. Rep. 17(3), 4 (2007)

Y. Huang, X. Duan, Q. Wei, C.M. Lieber, Science 291, 630 (2001)

Y. Huang, X. Duan, Y. Cui, L.J. Lauhon, K.-H. Kim, C.M. Lieber, Science 294, 1313 (2001)

Z. Zhong, D. Wang, Y. Cui, M.W. Bockrath, C.M. Lieber, Science 302, 1377 (2003)

A.E. Grigorescu, C.W. Hagen, Nanotechnology 20, 292001 (2009)

D.C. Flanders, A.E. White, J. Vac. Sci. Technol. B 19, 692 (1981)

G.A. Garfunkel, M.B. Weissman, J. Vac. Sci. Technol. B 8, 1087 (1990)

D. Wang, B.A. Sheriff, M. McAlpine, J.R. Heath, Nano Res. 1, 9 (2008)

J.R. Heath, Acc. Chem. Res. 41, 1609 (2008)

D.C. Flanders, N.N. Efremow, J. Vac. Sci. Technol. B 1, 1105 (1983)

Y.-K. Choi, J. Zhu, J. Grunes, J. Bokor, G.A. Somorjai, J. Phys. Chem. B 107, 3340 (2003)

Y.-K. Choi, J.S. Lee, J. Zhu, G.A. Somorjai, L.P. Lee, J. Bokor, J. Vac. Sci. Technol. B 21, 2951 (2003)

G.F. Cerofolini, P. Amato, E. Romano, Semicond. Sci. Technol. 23, 075020 (2008)

Y. Zhao, E. Berenschot, H. Jansen, N. Tas, J. Huskens, M. Elwenspoek, Nanotechnology 20, 315305 (2009)

M.H. Ben Jamaa, G. Cerofolini, G. De Micheli, Y. Leblebici, Complete nanowire crossbar framework optimized for the multi-spacer patterning technique, in Int. Conf. Compilers, Architecture and Synthesis for Embedded Systems—CASES 2009 (2009), pp. 11–16

M.H. Ben Jaama, G. Cerofolini, G. De Micheli, Y. Leblebici, IEEE Trans. Nanotechnol. 10, 891 (2011)

L. Chao (ed.), Intel Technol. J. 12, 77 (2008)

L.T. Canham, Appl. Phys. Lett. 57, 1046 (1990)

L.T. Canham, Nature 408, 411 (2000)

V. Schmidt, J.V. Wittemann, U. Gösele, Chem. Rev. 110, 361 (2010)

G.F. Cerofolini, P. Amato, M. Masserini, G. Mauri, Adv. Sci. Lett. 3, 345 (2010)

P. Horowitz, W. Hill, The Art of Electronics, 2nd edn. (Cambridge University Press, Cambridge, 1989)

I.S. Kim, S.L. Cho, D.H. Im, E.H. Cho, D.H. Kim, G.H. Oh, D.H. Ahn, S.O. Park, S.W. Nam, J.T. Moon, C.H. Chung, High performance PRAM cell scalable to sub-20 nm technology with below 4F 2 cell size, extendable to DRAM applications, in 2010 Symp. VLSI Technology (2010), Digest of Technical Papers, pp. 203–204

M.L. Polignano, P. Picco, G.F. Cerofolini, J. Electrochem. Soc. 127, 2734 (1980)

F. Faggin, T. Klein, Solid-State Electron. 13, 1125 (1970) extended version of work presented by F. Faggin, T. Klein, L. Vadasz, in Int. Electron Devices Meet., Washington, DC, October 1968

L.L. Vadasz, A.S. Grove, T.A. Rowe, G.E. Moore, IEEE Spectr. 6(10), 28 (1969)

http://isiwebofknowledge.com/. Accessed on 5 October 2010

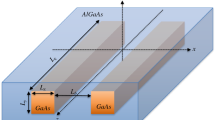

G.F. Cerofolini, M. Ferri, E. Romano, F. Suriano, G.P. Veronese, S. Solmi, D. Narducci, Semicond. Sci. Technol. 25, 095011 (2010)

M. Ferri, A. Roncaglia, S. Solmi, F. Suriano, G.F. Cerofolini, E. Romano, D. Narducci, Microelectron. Eng. 88, 877 (2011)

G.F. Cerofolini, M. Ferri, E. Romano, F. Suriano, G.P. Veronese, S. Solmi, D. Narducci, Semicond. Sci. Technol. 26, 045005 (2011)

K.K. Likharev, Electronics below 10 nm, in Nano and Giga Challenges in Microelectronics, ed. by J. Greer, A. Korkin, J. Labanowsky (Amsterdam, Elsevier, 2003), pp. 27–68

K.K. Likharev, D.B. Strukov, CMOL: Devices, circuits, and architectures, in Introducing Molecular Electronics, ed. by G. Cuniberti, G. Fagas, K. Richter (Springer, Berlin, 2005), pp. 447–477. Chap. 16

D.B. Strukov, K.K. Likharev, Nanotechnology 16, 137 (2005)

D.B. Strukov, K.K. Likharev, Nanotechnology 16, 888 (2005)

K.K. Likharev, J. Nanoelectron. Optoelectron. 3, 203 (2008)

K.K. Likharev, Sci. Adv. Mater. 3, 322 (2011)

D.B. Strukov, R.S. Williams, Proc. Natl. Acad. Sci. USA 106, 20155 (2009)

G. Cerofolini, E. Romano, D. Narducci, The litho-to-nano link, in Dekker Encyclopedia of Nanoscience and Nanotechnology, 2nd edn., ed. by J.A. Schwarz, C.I. Contescu, K. Putyera (Dekker, New York, 2009), pp. 1890–1900

M.Q. Huda, K. Sakamoto, Nucl. Instrum. Methods Phys. Res. B 216, 20 (2004)

J. Borghetti, G.S. Snider, P.J. Kuekes, J.J. Yang, D.R. Stewart, R.S. Williams, Nature 464, 873 (2010)

A. Zolfaghari, A. Chan, B. Razavi, IEEE J. Solid-State Circuits 36, 620 (2001)

L. Ciobanu, D.A. Jayawickrama, X. Zhang, A.G. Webb, J.V. Sweedler, Angew. Chem., Int. Ed. Engl. 42, 4669 (2003)

J.W. Sweedler, R.L. Magin, T.L. Pack, A.G. Webb, Microcoil based micro-NMR spectrometer and method, US Patent 6,788,061, 7 Sept. 2004

A.G. Goloshevsky, J.H. Walton, M.V. Shutov, J.S. de Ropp, S.D. Collins, M.J. McCarthy, Rev. Sci. Instrum. 76, 024101 (2005)

M. Poggio, C.L. Degen, Nanotechnology 21, 342001 (2010)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Cerofolini, G.F. Realistic limits to computation. Appl. Phys. A 106, 967–982 (2012). https://doi.org/10.1007/s00339-011-6724-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00339-011-6724-2