Abstract

This paper analyzes the operation and characterizes the performance of a three-phase three-level (3-L) Sparse Neutral Point Clamped converter (SNPCC) for industrial variable speed drives (VSDs). The operating principle of the SNPCC, which advantageously employs a lower number of power transistors than a conventional 3-L inverter, is described in detail, focusing on the AC-side differential-mode and common-mode voltage formation and on the DC-side mid-point current generation processes. The degrees of freedom in the SNPCC modulation scheme are defined and several switching sequences are investigated. Afterwards, the stresses on the active and passive components (e.g. semiconductor losses, machine phase current ripple, DC-link capacitor RMS current, etc.) are calculated by analytical and/or numerical means, enabling a straightforward performance comparison among the identified switching sequences. The most suited modulation strategy for VSD applications is then selected and a chip area sizing procedure, aimed at minimizing the total semiconductor chip size, is applied to a 800V 7.5kW three-phase system. The performance limits of the designed SNPCC are evaluated and finally compared to the ones of conventional 2-L and 3-L solutions, highlighting the promising cost/performance trade-off of the analyzed topology.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Industrial variable speed drives (VSDs) and electric vehicle traction inverters [1] are highly cost sensitive and should show high reliability, which favors low-complexity, robust and proven inverter concepts based on silicon (Si) IGBTs.

The conventional three-phase (3-\(\Phi \)) two-level (2-L) inverter topology represents the de-facto industrial standard, due to its simplicity, low number of switches (i.e. 6 transistors and 6 diodes) and well understood operation [2]. However, when higher DC-link voltages are present, e.g. 800 \(\hbox {V}\), the voltage rating of the devices must increase accordingly, leading to higher switching losses and larger overall semiconductor chip area. Three-level (3-L) inverters, such as the Neutral-Point Clamped (NPC) and T-Type topologies, represent excellent candidates for higher voltage drives, as they employ devices with reduced voltage ratings ensuring superior overall performance [3,4,5]. Moreover, taking advantage of the increased number of output voltage levels, they reduce the high-frequency harmonic current stress on the driven machine [6].

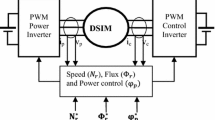

The Sparse Neutral Point Clamped converter (SNPCC) [7] illustrated in Fig. 1 has been introduced in [8] and represents a promising alternative to traditional 3-L inverters. The main advantage of the SNPCC resides in its lower number of active devices, i.e. 10 power transistors, compared to NPC and T-type 3-L converters, which both require at least 12 power transistors. On the other hand, the simpler converter structure translates in a lower number of switching states at high modulation indices [9], leading to slightly larger switching frequency output voltage harmonics. Due to its cascaded structure, composed of a 3-L switching matrix (SM) connected to a conventional 3-\(\Phi \) 2-L inverter, the SNPCC lends itself to hybrid implementations. In particular, the 3-L SM and the 2-L inverter can conveniently adopt different semiconductor technologies (e.g. MOSFETs and IGBTs), since the former stage should maximize the switching performance, whereas the latter should minimize the conduction losses. Moreover, the complete converter can be integrated in a single power module, minimizing the commutation loop of the 2-L inverter devices, which includes two of the 3-L SM switches [10].

Schematic of the Sparse Neutral Point Clamped converter (SNPCC). The cascaded structure composed of a three-level (3-L) switching matrix (SM) connected to a three-phase (3-\(\Phi \)) two-level (2-L) inverter is highlighted. The diodes are named according to the paired transistors (see \({D_\text {p,h}}\))

Schematic of the 3-L switching matrix (SM) conduction states and respective SNPCC output voltage space vectors: a zero vector states, b small vector states and c large vector states. The complete SNPCC space vector hexagon is illustrated in (d), together with a reference voltage vector \(\vec {V}^*\) and its decomposition. Sector and its subdivision in area

and its subdivision in area and area

and area are highlighted in (e) in combination with the associated zero, small and large vectors

are highlighted in (e) in combination with the associated zero, small and large vectors

The operating principle and space vector modulation of the SNPCC have been analyzed in [8, 9, 11, 12], while several control strategies for VSD applications are presented in [7, 13,14,15,16,17]. Furthermore, the design of a hybrid GaN-Si SNPCC is reported in [10]. Nevertheless, according to the authors’ best knowledge, a complete analysis of the converter component stresses and overall performance is not available in literature, especially considering the degrees of freedom associated with the converter modulation strategy. For instance, [9] identifies and compares several PWM pulse patterns with a different number of switching transitions, however only the effect on the low-frequency DC-link mid-point voltage oscillation is investigated, disregarding the induced switching frequency harmonic current stress on the driven machine and the switching losses in the semiconductor devices. Moreover, the analysis of [9] is limited to symmetric pulse patterns, hence excluding asymmetric ones, which can trade a higher sampling/control complexity for improved converter performance.

Accordingly, the main goals of this work are to provide a detailed analysis of the operation of the SNPCC, identify the most suitable symmetric and asymmetric modulation strategies for VSD application and derive the analytical and/or numerical expressions describing the stresses on the major active and passive components. These expressions quantitatively support the converter design, facilitating the sizing of DC-link capacitors, semiconductor devices and heatsink, and provide an indication of the spectrum of the converter 3-\(\Phi \) output voltage, i.e. of the high-frequency harmonic stress on the driven machine. In particular, a complete performance comparison between modulation strategies over the full converter operating region is provided, taking into account the current ripple stress on the driven machine and the semiconductor switching losses. Moreover, a conclusive semiconductor chip area investigation aims to identify the cost/performance trade-off of the SNPCC, in comparison to traditional 2-L and 3-L solutions.

This paper is structured as follows. The operating principle of the SNPCC is described in Sect. 2. The converter switching states are identified and both the AC-side differential-mode (DM) and common-mode (CM) voltage formation and the DC-side mid-point current generation processes are explained. In Sect. 3, several suitable modulation strategies are defined, according to a set of rules constraining the switching sequence. In Sect. 4, the major component stresses, such as the machine phase current ripple, the DC-link capacitor RMS current and the semiconductor losses are investigated. In Sect. 5, a chip area minimization procedure is applied to three different 800\(\hbox {V}\) 7.5\(\hbox {kW}\) 3-\(\Phi \) VSD systems, adopting a 2-L, a 3-L NPC and a 3-L SNPC converters, respectively. The performance limits of each topology are identified and compared, highlighting the promising cost/performance trade-off of the SNPCC. Finally, in Sect. 6, a brief summary of the main contributions of this work is provided. In the Appendix, further clarifications on the adopted analytical methods for the derivation of the machine phase current ripple and the converter switching losses are given.

2 Operating principle

The SNPCC is composed of a capacitively splitted DC input and a 3-L SM, i.e. a 3-L DC voltage source, feeding a 3-\(\Phi \) 2-L inverter, as illustrated in Fig. 1. The role of the 3-L SM is to control the 2-L inverter rail-to-rail voltage \(v_{\text {hl}}\) in order to provide the desired 3-\(\Phi \) output voltage in combination with the 2-L inverter. Due to the split DC-link, the 3-L SM semiconductor devices advantageously require only half the voltage rating of the 2-L inverter devices, resulting in lower on-state losses and higher switching speed.

2.1 Converter states

Because of its cascaded structure, the SNPCC offers a total of \(2^2 \! \cdot 2^3 \!= \!32\) conduction states [9]. While 18 of these combinations effectively apply a nonzero 3-\(\Phi \) line-to-line output voltage (denominated active states), the remaining 14 combinations force a short-circuit of the 3-\(\Phi \) output (denominated zero states). To avoid DC-link short circuits, only the combinations reported in Fig. 2a, b and c are allowed for the 3-L SM. Additionally, for reasons that will be clarified in Sect. 3, the 2-L inverter zero states are not considered, thus the total count of zero states reduces to 6.

The converter states can be unequivocally identified by the 5 bridge-leg switching functions

By leveraging the relation between switching functions and bridge-leg voltages, the space vector representation of Fig. 2d can be finally obtained [9]. The main role of the 3-L SM is to synthesize the amplitude of the reference voltage vector \(\vec {V}^*\), while the role of the 2-L inverter is to establish its direction. Three kinds of space vectors are identified and categorized according to their amplitude: zero vectors, small vectors with amplitude \(V_{\text {dc}}/3\) and large vectors with amplitude \(2V_{\text {dc}}/3\). The main difference between the SNPCC and standard 3-L inverters is the absence of medium vectors [18], which translates in a lower number of active states (18 against 24) and slightly higher switching frequency output voltage distortion.

For symmetry reasons, the converter operation can be completely analyzed inside a 60\(^\circ \)-wide interval of a 3-\(\Phi \) output period, i.e. a sector; sector is illustrated in Fig. 2e. Each sector can be divided in two main areas: area

is illustrated in Fig. 2e. Each sector can be divided in two main areas: area delimited by zero and small vectors, and area

delimited by zero and small vectors, and area delimited by small and large vectors. The switching functions corresponding to the space vectors of sector

delimited by small and large vectors. The switching functions corresponding to the space vectors of sector are reported in Table 1. It can be observed that small vectors are redundant, since they can all be obtained with either of the two complementary states represented in Fig. 2b, both ensuring \(\ v_\text {hl} = V_\text {dc}/2.\)

are reported in Table 1. It can be observed that small vectors are redundant, since they can all be obtained with either of the two complementary states represented in Fig. 2b, both ensuring \(\ v_\text {hl} = V_\text {dc}/2.\)

2.2 Space vectors dwell-time calculation [9]

Defining the converter modulation index \(M = 2V^*/V_{\text {dc}}\), reporting the reference space vector angle \(\vartheta \) in a \([{0}{},{60}^\circ ]\) window and leveraging simple geometrical relations, the dwell-time expressions

are obtained in sector , where

, where

and the modulation index boundary between area and area

and area is

is

The dwell-time calculation in area assumes that no small or large vector can be avoided in a switching sequence. Even though area

assumes that no small or large vector can be avoided in a switching sequence. Even though area could be divided into sub-regions to reduce the minimum number of space vector transitions in a switching period [12], this would increase the degrees of freedom in the modulation strategy definition and considerably complicate the PWM and control processes, hence it is not considered herein.

could be divided into sub-regions to reduce the minimum number of space vector transitions in a switching period [12], this would increase the degrees of freedom in the modulation strategy definition and considerably complicate the PWM and control processes, hence it is not considered herein.

2.3 DC-link mid-point current generation

In order to ensure a symmetric 3-L characteristic and a limitation of the blocking voltage stress on the 3-L SM switches to half of the total DC input voltage, the voltages \(V_\text {pm}\) and \(V_\text {mn}\) across the two series connected DC-link capacitors must be balanced [19], as described in the following.

The 2-L inverter rail current

allows to derive the 3-L SM rail currents

which are summarized in Table 1 (for sector ). Only the small vectors affect the mid-point current \(i_\text {m}\). In particular, the redundant vectors (\(V_{\text {S1,P}}/V_{\text {S1,N}}\) and \(V_{\text {S2,P}}/V_{\text {S2,N}}\)) have an equal and opposite effect on \(i_\text {m}\), allowing to balance the DC-link capacitor voltages \(V_\text {pm}\) and \(V_\text {mn}\). If both redundant small vectors are used, the mid-point current local average (i.e. mean value over a switching period) in sector

). Only the small vectors affect the mid-point current \(i_\text {m}\). In particular, the redundant vectors (\(V_{\text {S1,P}}/V_{\text {S1,N}}\) and \(V_{\text {S2,P}}/V_{\text {S2,N}}\)) have an equal and opposite effect on \(i_\text {m}\), allowing to balance the DC-link capacitor voltages \(V_\text {pm}\) and \(V_\text {mn}\). If both redundant small vectors are used, the mid-point current local average (i.e. mean value over a switching period) in sector is

is

where \(\alpha \in [0, \, 1]\) is a control parameter which defines the dwell-time of the positive small vectors, i.e. \(V_\text {S1,P}\) and \(V_\text {S2,P}\), relative to the total small vector dwell-times \(\delta _\text {S1}\) and \(\delta _\text {S2}\), respectively. In nominal operating conditions \(\alpha =0.5\) yields \(i_{\text {m,AVG}}=0\).

Bridge-leg switching functions \(s_\text {a}\), \(s_\text {b}\), \(s_\text {c}\), \(s_\text {p}\), \(s_\text {n}\) and voltage waveforms \(v_\text {hl}\), \(v_\text {am}\), \(v_\text {bm}\), \(v_\text {cm}\), \(v_\text {DM,a}\), \(v_\text {DM,b}\), \(v_\text {DM,c}\), \(v_\text {CM}\) in area (\(M \! = \! 1\)) a over a 3-\(\Phi \) output period and b over a switching period in sector

(\(M \! = \! 1\)) a over a 3-\(\Phi \) output period and b over a switching period in sector . Switching sequence U (see Sect. 3) is selected. In (a), the waveform local averages are superimposed to their instantaneous values for better understanding. The injected CM local average is the same as for standard space vector modulation

. Switching sequence U (see Sect. 3) is selected. In (a), the waveform local averages are superimposed to their instantaneous values for better understanding. The injected CM local average is the same as for standard space vector modulation

2.4 Output voltage formation

The converter 3-\(\Phi \) output voltage derives from the superposition of both the 3-L SM and the 2-L inverter switching functions. Considering a balanced mid-point voltage \(V_\text {pm}=V_\text {mn}=V_\text {dc}/2\),

is obtained. The DM component of \(v_\text {xm}\) defines the output voltage fundamental applied to the driven machine and the switching frequency voltage harmonics resulting in the phase current ripple (see Sect. 4), therefore it must be separated from the CM contribution. A straightforward approach considers the 3-L SM and 2-L inverter separately. The 3-L SM equivalent circuit is illustrated in Fig. 3a, where the virtual point \(\mathrm {m}\)’ is defined for the purpose of separating the DM and CM voltage sources into

The 2-L inverter equivalent circuit is shown in Fig. 3b, where a second virtual point is arbitrarily defined coincident with \(\mathrm {m}\)’. Both DM and CM contributions depend on \({v_\text {hl}= 2 \, v_{\text {DM,M}}}\), in particular

Finally, the total DM and CM voltages can be derived from (14)–(17), obtaining

A summary of the DM and CM output voltages in sector is provided in Table 2. The DM voltage waveform \(v_\text {DM,x}\) is composed of 5 levels in area

is provided in Table 2. The DM voltage waveform \(v_\text {DM,x}\) is composed of 5 levels in area and 6 levels in area

and 6 levels in area , while the CM waveform \(v_\text {CM}\) shows 5 levels in area

, while the CM waveform \(v_\text {CM}\) shows 5 levels in area and 4 levels in area

and 4 levels in area .

.

An example of the converter switching functions and voltage waveforms in area is provided in Fig. 4, where \(M \! = \! 1\) is considered. These waveforms are obtained by ordering the space vectors according to a generic switching sequence (i.e. sequence U, see Sect. 3) and translating them into a pulse pattern in the time domain. It can be visualized that the 2-L inverter switching functions (\(s_\text {a}\), \(s_\text {b}\) and \(s_\text {c}\)) are alternately clamped either to 0 or 1 for two-thirds of the fundamental period, as in the 1/3 Modulation [20]. This behavior derives from avoiding the 2-L inverter zero states, which allows to switch only one inverter bridge-leg in each sector. To achieve 3-\(\Phi \) sinusoidal (in local average) output voltages, the 3-L SM operates such that the local average of \(v_\text {hl}\) follows the 3-\(\Phi \) rectified line-to-line output voltage fundamentals. In other words, in each sector, the 3-L SM sets the desired voltage between the two clamped phases, leaving to the third inverter bridge-leg the regulation of the two remaining 3-\(\Phi \) line-to-line output voltages [20].

is provided in Fig. 4, where \(M \! = \! 1\) is considered. These waveforms are obtained by ordering the space vectors according to a generic switching sequence (i.e. sequence U, see Sect. 3) and translating them into a pulse pattern in the time domain. It can be visualized that the 2-L inverter switching functions (\(s_\text {a}\), \(s_\text {b}\) and \(s_\text {c}\)) are alternately clamped either to 0 or 1 for two-thirds of the fundamental period, as in the 1/3 Modulation [20]. This behavior derives from avoiding the 2-L inverter zero states, which allows to switch only one inverter bridge-leg in each sector. To achieve 3-\(\Phi \) sinusoidal (in local average) output voltages, the 3-L SM operates such that the local average of \(v_\text {hl}\) follows the 3-\(\Phi \) rectified line-to-line output voltage fundamentals. In other words, in each sector, the 3-L SM sets the desired voltage between the two clamped phases, leaving to the third inverter bridge-leg the regulation of the two remaining 3-\(\Phi \) line-to-line output voltages [20].

The local averages of \(v_\text {CM}\) and \(v_\text {xm}\) are the same as for the conventional space vector modulation, independently on the selected modulation strategy. This is because switching sequence U and all sequences described in Sect. 3 must include every available non-zero state and equally distribute the dwell-time between redundant small space vectors, thus yielding the same 3-\(\Phi \) output voltage local average as a conventional 2-L inverter. Differently from 2-L and other 3-L inverters, the dwell-time allocation of the zero states does not influence the CM voltage, since both \(V_\text {Z1}\) and \(V_\text {Z2}\) result in \(v_\text {CM}={0}\hbox {V}\).

The focus over a switching period in Fig. 4b provides insight into the selected switching sequence and allows to verify the DM and CM voltage levels listed in Table 2.

To conclude, the generated 3-\(\Phi \) sinusoidal output and mid-point current waveforms with unity power factor (\(\cos \varphi \! = \! 1\)), i.e. ohmic load behavior, are illustrated in Fig. 5. The value of the machine phase inductance (acting as filtering element) is selected to achieve a 30% maximum peak-to-peak current ripple during a 3-\(\Phi \) output period. While \(i_\text {m}\) continuously jumps between two 3-\(\Phi \) sinusoidal output currents and 0\(\hbox {A}\), its local average is 0\(\hbox {A}\) during the complete 3-\(\Phi \) output period. This behavior is maintained for all values of \(\cos \varphi \), since complementary redundant small vectors are always opportunely applied, as explained in Sect. 3.

3-\(\Phi \) sinusoidal output currents \(i_\text {a}\), \(i_\text {b}\), \(i_\text {c}\) and mid-point current \(i_\text {m}\) waveforms with unity load power factor (\(\cos \varphi \! = \! 1\)) over a 3-\(\Phi \) output period. Switching sequence U (see Sect. 3) is selected. Waveform local averages are superimposed to their instantaneous values for better understanding

3 Modulation strategies

The reference space vector \(\vec {V}^*\) (see Fig. 2d) can be synthesized in different ways, which give light to different modulation strategies. Both the switching sequence and the redundant small vector dwell-time allocation can be varied, yielding different results in terms of DM and CM voltage waveforms, semiconductor losses and mid-point current local average.

To limit the degrees of freedom in the modulation strategy definition, only switching sequences that

-

have a single switching function change per vector transition,

-

have less than 10 transitions per switching period,

-

begin and end with the same small vector in order to avoid additional transitions between area

and area

and area ,

, -

consider all redundant small vectors to have full control of the mid-point current local average (\(\alpha = 0.5\) in steady state) and

-

avoid the 2-L inverter zero states, since these would force additional switching transitions,

are considered throughout this work.

Graphical representation of the most suitable symmetric and asymmetric switching sequences starting with \(V_\text {S1,P}\): a 6-transition sequence, b 8-transition sequences and c 10-transition sequences. The switching transitions involving the 3-L SM are represented by blue arrows, while pink arrows indicate the 2-L inverter transitions. Sequence C is only admitted in area , since no large vector can generally be avoided in area

, since no large vector can generally be avoided in area . Four times the displayed sequences are possible, since each sequence can be mirrored, i.e. can start with any small vector (grid corner)

. Four times the displayed sequences are possible, since each sequence can be mirrored, i.e. can start with any small vector (grid corner)

According to these hypotheses, the converter states can be displayed in grid arrangement as in Fig. 6, with two different grids for area and area

and area , where \(V_\text {Z1}\) and \(V_\text {Z2}\) in the former are replaced by \(V_\text {L1}\) and \(V_\text {L2}\) in the latter. This representation, firstly proposed in [9], easily illustrates the admitted switching transitions for the 3-L SM (blue arrows) and the 2-L inverter (pink arrows). By means of simple geometrical considerations and aiming for the minimum number of switching events, the switching sequences which comply with the mentioned hypotheses are identified and reported in Fig. 7 and in Table 3. The equivalent switching frequencies of the 3-L SM \(f_\text {sw,M}\) and the 2-L inverter \(f_\text {sw,I}\) in Table 3 (normalized with respect to the sampling/control frequency \(f_\text {s}\)) are found by averaging the switching frequencies of the respective transistors as

, where \(V_\text {Z1}\) and \(V_\text {Z2}\) in the former are replaced by \(V_\text {L1}\) and \(V_\text {L2}\) in the latter. This representation, firstly proposed in [9], easily illustrates the admitted switching transitions for the 3-L SM (blue arrows) and the 2-L inverter (pink arrows). By means of simple geometrical considerations and aiming for the minimum number of switching events, the switching sequences which comply with the mentioned hypotheses are identified and reported in Fig. 7 and in Table 3. The equivalent switching frequencies of the 3-L SM \(f_\text {sw,M}\) and the 2-L inverter \(f_\text {sw,I}\) in Table 3 (normalized with respect to the sampling/control frequency \(f_\text {s}\)) are found by averaging the switching frequencies of the respective transistors as

where \(f_\text {sw,j}\) and \(f_\text {sw,k}\) are the switching frequencies of the j-th transistor in the 3-L SM and the k-th transistor in the 2-L inverter, respectively.

Equivalent circuit representation of all converter conduction states in area of sector

of sector , ordered according to sequence U. Since sequence U is symmetric, the space vector pattern from \(V_\text {S1,P}\) to \(V_\text {S2,P}\) is repeated in the opposite direction during the second half of the switching period

, ordered according to sequence U. Since sequence U is symmetric, the space vector pattern from \(V_\text {S1,P}\) to \(V_\text {S2,P}\) is repeated in the opposite direction during the second half of the switching period

A distinction must be made between switching sequences with symmetric and asymmetric pulse patterns. Symmetric sequences are mirrored with respect to their center, meaning that the first half of the sequence is repeated in inverse order in the second half of the switching period. This is not the case for asymmetric pulse patterns: as a consequence, there is no fixed point in time when the instantaneous current value equals its local average, thus regular sampling cannot be adopted. Nevertheless, this issue can be easily overcome by modern microcontrollers with built-in oversampling and averaging functions. Therefore, both symmetric (C, U, S, G) and asymmetric (O, 8, B, 6, A, H, 3) sequences are considered in the present analysis.

Since the switching sequence starting vector (i.e. one of the four small vectors) can determine different switching losses and affect their distribution among the semiconductor devices, all four sequence variants are investigated. In general, it can be advantageous to adopt different variants of a sequence in consecutive sectors. In order to minimize the number of switching actions at the sector transitions, only sequences starting with \(V_\text {S1,P}/V_\text {S2,P}\) or \(V_\text {S1,N}/V_\text {S2,N}\) can be alternated, i.e. mirrored. This can reduce or eliminate uncontrollable current ripple spikes at the sector transitions, typically encountered when asymmetric pulse patterns are adopted. Although this measure does not eliminate the low-frequency harmonics in the output voltage waveform, inherent to asymmetric switching sequences, the resulting current distortion can be reduced with a properly tuned converter closed-loop control, comprising a disturbance feed-forward correction. In addition, it can be demonstrated that alternating complementary switching sequences between odd and even sectors allows to obtain symmetric switching loss characteristics with respect to the load power factor for all modulation strategies (see Fig. 14). For the mentioned reasons, the mirroring of switching sequences is considered throughout this work, yielding results which are independent on the sequence starting vector and thus simplifying the analysis.

All the identified symmetric switching sequences (i.e. C, U, S, G) are also reported in [9], which additionally considers modulation strategies that do not ensure a zero mid-point current local average and that adopt the 2-L inverter zero states in area . For instance, sequence U is referred to as Maximum Neutral Point Balancing (MNPB) sequence in [9] and is tested experimentally on a SNPCC prototype in [10].

. For instance, sequence U is referred to as Maximum Neutral Point Balancing (MNPB) sequence in [9] and is tested experimentally on a SNPCC prototype in [10].

Finally, for completeness, an equivalent circuit representation of all converter conduction states in area of sector

of sector , ordered according to sequence U, is reported in Fig. 8.

, ordered according to sequence U, is reported in Fig. 8.

4 Component stresses

The voltage and/or current stresses on the active and passive components have a direct impact on the converter design. Analytical and/or numerical expressions are derived in this section for all major component stresses, in relation with the adopted modulation strategy.

Normalized output current ripple \(\Delta i_\text {x}/\Delta I_\text {n}\) over a 3-\(\Phi \) output period for \(M = 0.85\). All switching sequences are displayed except for C, since \(M > 1/\sqrt{3}\). The ripple waveforms related to sequences 8, 6 and A are not half-wave symmetric and thus include even order switching harmonics

In the following calculations, the expressions of the 3-\(\Phi \) sinusoidal output currents

where \(\varphi \) is the load power factor angle, are considered.

Figure 9 highlights the transition region between area and

and  in sector

in sector , i.e. the modulation index interval \(\nicefrac {1}{\sqrt{3}} \le M \le \nicefrac {2}{3}\) in which the reference space vector \(\vec {V}^*\) crosses both areas. Since separate analytical expressions of the component stresses are derived for area

, i.e. the modulation index interval \(\nicefrac {1}{\sqrt{3}} \le M \le \nicefrac {2}{3}\) in which the reference space vector \(\vec {V}^*\) crosses both areas. Since separate analytical expressions of the component stresses are derived for area and area

and area , a merging procedure must be performed in the transition region, in order to ensure the continuity of the results. Leveraging simple geometrical relations, the merged expression of the generic quantity X can be obtained as

, a merging procedure must be performed in the transition region, in order to ensure the continuity of the results. Leveraging simple geometrical relations, the merged expression of the generic quantity X can be obtained as

where  and

and  are the expressions in area

are the expressions in area and area

and area , respectively, and

, respectively, and

is the angle reported in Fig. 9.

4.1 Machine phase current ripple

The DM voltage-time area applied to the machine phases generates a switching frequency flux linkage ripple, which translates in a current ripple inversely proportional to the machine phase inductance L. This ripple is directly responsible for the high-frequency winding and iron losses in the machine itself [21], thus representing a first performance indicator of the adopted modulation strategy.

The current ripple of phase x is found by integrating the high-frequency component of the DM voltage \(v_{\text {DM,x,hf}}\), i.e. subtracting the local average from \(v_\text {DM}\), as

This modeling approach has been adopted and experimentally validated in [22], demonstrating a high level of accuracy.

A highlight of the output current ripple waveforms is provided in Fig. 10, assuming \(M \! = \! 0.85\). To generalize the results, the normalization factor

is introduced [23] and the current ripple waveforms are expressed in normalized form. It is worth observing that some asymmetric switching sequences (e.g. 8, 6, A) yield a current ripple envelope that lacks half-wave symmetry, thus featuring an output current spectrum with even order switching harmonics, neverthless, these harmonics do not affect the low-frequency sinusoidal output current shape.

To take into account the complete \({3{\text {-}}\Phi }\) output period, the total RMS current ripple is considered as performance index. Its value can be derived by averaging the RMS current ripple contributions of all three phases over one sector as

It is easily proven that \(\Delta I_\text {RMS}\) is independent on the starting vector of the switching sequence. Separate \(\Delta I_\text {RMS}\) analytical expressions can be derived for area and area

and area , as described in Appendix 1. Therefore, to ensure the continuity of the results over the complete modulation index M range, the merging procedure previously described is applied.

, as described in Appendix 1. Therefore, to ensure the continuity of the results over the complete modulation index M range, the merging procedure previously described is applied.

The normalized total RMS current ripples generated by the different modulation strategies are reported in Fig. 11. A best performing sequence cannot be identified over the full operating range, since \(\Delta I_\text {RMS}\) depends on M. Nevertheless, an overall satisfactory trend is offered by sequence 8, which yields the lowest \(\Delta I_\text {RMS}\) value for high modulation indices.

4.2 DC-Link capacitor RMS current

Disregarding the switching frequency current ripple, the RMS current flowing into each DC-link capacitor in balanced conditions is not affected by the modulation strategy, since it only depends on the space vector dwell-times, as discussed in the following. Leveraging the sector periodicity, the expressions for the DC-link upper-rail current \(i_\text {p}\), i.e.

are obtained, where, focusing on sector ,

,

Therefore, the same DC-link capacitor RMS current as for conventional 2-L and 3-L inverters results [24, 25], i.e.

Even though \(I_{C_\text {dc},\text {RMS}}\) is independent on the modulation strategy, the voltage ripple on \(C_\text {dc}\) generally depends on the switching sequence itself. Nevertheless, since all the strategies considered in this work force a zero mid-point current local average, no low-frequency mid-point voltage ripple is present, making a comparison between switching sequences unnecessary in these regards.

4.3 Semiconductor devices

4.3.1 Conduction losses

Silicon IGBTs and diodes are considered throughout this work. Their conduction characteristics can be approximated with a constant forward voltage drop term \(V_\text {th}\) and a differential resistance term R, as illustrated in Fig. 12a. Therefore, their conduction losses can be expressed by

where \(I_\text {AVG}\) and \(I_\text {RMS}\) are the average and RMS currents flowing through each device, respectively.

Disregarding the switching frequency current ripple, both \(I_\text {AVG}\) and \(I_\text {RMS}\) can be analytically derived for every device. This approach has been largely adopted in literature and its accuracy has been experimentally proven, e.g. in [26]. Different analytical expressions are found, depending on whether the reference voltage vector lies in area or area

or area , therefore the merging of the results is applied in the transition region. Due to the complex nature of the derived expressions, these are not reported herein, nevertheless the IGBT current stresses are illustrated in Fig. 13 in normalized form, as a function of M and \(\varphi \). The current stresses in the paired diodes are identical, but shifted by \(\varphi = \pi \).

, therefore the merging of the results is applied in the transition region. Due to the complex nature of the derived expressions, these are not reported herein, nevertheless the IGBT current stresses are illustrated in Fig. 13 in normalized form, as a function of M and \(\varphi \). The current stresses in the paired diodes are identical, but shifted by \(\varphi = \pi \).

It can be demonstrated that none of the expressions of \(I_\text {AVG}\) and \(I_\text {RMS}\) depends on the utilized switching sequence. Only if the 2-L inverter zero states were to be adopted, the conduction losses of the 3-L SM would depend on the modulation strategy, since during the 2-L inverter zero states none of the 3-L SM devices would be conducting.

Normalized \(I_\text {AVG}\) and \(I_\text {RMS}\) flowing through a, b the 2-L inverter transistors and c, d, e, f, the 3-L SM transistors, as a function of the modulation index M and the power factor angle \(\varphi \) (normalization with respect to I). The same current values apply to the respective diodes, however the results are shifted by \(\varphi = \pi \). The current stresses in the 2-L inverter devices are mostly independent on M, as for conventional 2-L inverters [24], while the current stresses in the 3-L SM devices strongly depend on both M and \(\varphi \). The maximum stress in these devices is always found for \(\varphi = 0\) or \(\varphi = \pi \), since the average and RMS values of the current flowing into the 3-L SM (i.e. \(i_\text {h}\)) are highest when the power transfer is maximized (i.e. \(\cos \varphi = \pm 1\)). Moreover, the value of M varies the conduction time intervals of the 3-L SM internal devices (\(\mathrm {T}_\text {p,h}\), \(\mathrm {T}_\text {n,l}\)) and external devices (\(\mathrm {T}_\text {p,l}\), \(\mathrm {T}_\text {n,h}\)), maximizing their current stresses for \(M = 0\) and \(M = 2/\sqrt{3}\), respectively

4.3.2 Switching losses

The converter switching losses and their distribution between the 2-L inverter and the 3-L SM strongly depend on the selected switching sequence, since transitioning from a converter state to another can result in a more or less lossy commutation depending on the switched voltage and switched current values, as shown in Appendix 2. It can be easily demonstrated that the total converter switching losses have sector periodicity. Additionally, sequences G, C, 8, 6, A and 3 show different switching performance depending on the sequence starting vector. Nevertheless, by varying the starting vector between odd and even sectors as described in Sect. 3, this difference averages out over one \({3{\text {-}}\Phi }\) output period, resulting in a symmetrical switching loss characteristic with respect to the load power factor angle \(\varphi \).

To gain a quantitative insight into the switching performance of the SNPCC, the simplified energy loss model illustrated in Fig. 12b, based on a linear dependence with respect to both switched voltage \(V_{\text {sw}}\) and current \(i_{\text {sw}}\), is adopted. Two different coefficients are identified for the turn-on (\(k_\text {on}\)) and the turn-off (\(k_\text {off}\)) transitions, leading to different loss components, i.e.

where \(k_\text {on}\) includes the diode reverse-recovery loss contribution. If both transitions occur with the same \(V_\text {sw}\) and \(i_\text {sw}\) values, the total switching losses can be summarized as

where \(k = k_\text {on} + k_\text {off}\) and its value is assumed to only depend on the semiconductor voltage rating, as explained in Sect. 5.

The main goal of the considered simplified loss model is to enable a straightforward comparison among switching sequences. Nevertheless, the adopted linear switching loss approximation is met for most commercial IGBT/diode pairs, as attested by the switching loss data provided by the main manufacturers [27, 28].

Disregarding the switching frequency current ripple and analyzing all vector transitions in each switching sequence, it is possible to express the 3-L SM and 2-L inverter switching losses analytically in closed form, as described in Appendix 2. The results of this analysis are independent on the semiconductor chip area (see Sect. 5) and are shown in normalized form in Fig. 14 as a function of \(\varphi \), considering the values of \(k_\text {on}\), \(k_\text {off}\) and k reported in Table 5. The switching loss subdivision between the 3-L SM and the 2-L inverter is derived for sequence 8 for demonstration purposes and is graphically illustrated in Fig. 21. Since separate analytical expressions are found for area and area

and area , the switching losses in the transition region can be calculated with the previously reported merging procedure. Even though no single best solution is identified, sequence O results the best candidate over the full operating range for high M values, i.e. in area

, the switching losses in the transition region can be calculated with the previously reported merging procedure. Even though no single best solution is identified, sequence O results the best candidate over the full operating range for high M values, i.e. in area , since it avoids the most lossy switching transitions between large vectors.

, since it avoids the most lossy switching transitions between large vectors.

5 Converter sizing and performance evaluation

The sizing and the performance evaluation of a 7.5\(\hbox {kW}\) \({3{\text {-}}\Phi }\) SNPCC for VSD applications are described in the following, leveraging the analysis presented in the previous sections. The converter specifications and nominal operating conditions are summarized in Table 4.

5.1 Optimal modulation strategy

As discussed in Sect. 4, the performance of the switching sequences is summarized by \(\Delta I_{\text {RMS}}\) in Fig. 11 and \(E_ {\text {sw}}\) in Fig. 14. To compare them, an appropriate switching frequency \(f_\text {sw}\) is selected for each sequence to equalize the switching losses in nominal operating condition. Since \(\Delta I_\text {RMS}\) is inversely proportional to \(f_\text {sw}\), this process allows to obtain a single normalized performance index, providing a clear relative comparison between modulation strategies.

Switching losses in a area and b area

and b area , normalized with respect to the switching losses of sequence U at \(\varphi =0\) in each area. The analytical derivation of these expressions is provided in Appendix 2. Some modulation strategies, i.e. S-C-3, B-O-8 in area

, normalized with respect to the switching losses of sequence U at \(\varphi =0\) in each area. The analytical derivation of these expressions is provided in Appendix 2. Some modulation strategies, i.e. S-C-3, B-O-8 in area and S-3, B-8 in area

and S-3, B-8 in area , yield identical switching losses and are thus superimposed. The highest switching loss values are encountered in area

, yield identical switching losses and are thus superimposed. The highest switching loss values are encountered in area , since the \({V}_{\text {Z1}} \leftrightarrow {V}_{\text {Z2}}\) lossless transitions (i.e. \(V_\text {sw} = 0\)) are replaced by \({V}_{\text {L1}} \leftrightarrow {V}_{\text {L2}}\) (i.e. \(V_\text {sw} = V_\text {dc}\)). Therefore, all sequences which include these transitions are strongly favored or penalized depending whether the SNPCC is operating in area

, since the \({V}_{\text {Z1}} \leftrightarrow {V}_{\text {Z2}}\) lossless transitions (i.e. \(V_\text {sw} = 0\)) are replaced by \({V}_{\text {L1}} \leftrightarrow {V}_{\text {L2}}\) (i.e. \(V_\text {sw} = V_\text {dc}\)). Therefore, all sequences which include these transitions are strongly favored or penalized depending whether the SNPCC is operating in area or area

or area , respectively. The switching loss maxima in correspondence of \(\varphi = \pm \pi /2\) are directly related to the 2-L inverter devices, since the two 30\(^\circ \) switching windows of each bridge-leg (see Fig. 4a) become aligned with the respective phase current positive and negative peaks, thus maximizing the averaged switched current

, respectively. The switching loss maxima in correspondence of \(\varphi = \pm \pi /2\) are directly related to the 2-L inverter devices, since the two 30\(^\circ \) switching windows of each bridge-leg (see Fig. 4a) become aligned with the respective phase current positive and negative peaks, thus maximizing the averaged switched current

a Total RMS current ripple normalized with respect to sequence U \(\Delta I_\text {RMS}/\Delta I_{\text {RMS},U}\) for nominal operation (\(M \! = \! 0.85\), \(\cos \varphi \! = \! 1\)), after adjusting the switching frequency \(f_\text {sw}\) of all modulation strategies in order to equalize the total switching losses. The adjusted switching frequency values (normalized with respect to the SM frequency in sequence U) and the switching loss subdivision between the two converter stages are reported in (b) and (c), respectively. All results are expressed in per unit (p.u.). Sequence C is not present since \(M \! > \! 1/\sqrt{3}\), while sequence 8 is the best performing (\(\star \))

This comparison is performed assuming nominal operating conditions (i.e. \(M \! = \! 0.85\), \(\cos \varphi \! = \! 1\)) and the results are illustrated in Fig. 15a, where lower index values translate into better performance. Figure 15b and c report the adjusted switching frequency values of both converter stages and the switching loss distribution between the 3-L SM and the 2-L inverter, respectively. It is shown that the relation between the switching frequency of a converter stage and its switching losses is not straightforward, as the results are also affected by the switched current and voltage values (see Appendix 2).

Overall, the best performing switching sequence in the considered working point is the asymmetric sequence 8. Even though sequence S shows similar performance, i.e. achieving the best results among symmetric sequences, it features wider variations of \(\Delta I_\text {RMS}(M)\) (see Fig. 11) and \(E_\text {sw}(\varphi )\) (see Fig. 14) with respect to sequence 8, thus leading to a larger converter oversizing if a wide range of operating points needs to be covered.

5.2 Minimum semiconductor chip area

Depending on the operating point of the SNPCC, the current flowing through the semiconductor devices can be unevenly distributed, as shown in Fig. 13. This, together with the different conduction and switching characteristics of IGBTs and diodes, can lead to the unbalanced loading of certain devices. Therefore, the required chip area for each semiconductor device is investigated herein.

The basic concept behind the described chip area minimization procedure is to adapt the chip size of each semiconductor device based on its power losses, aiming to comply with a predefined maximum operating junction temperature. For instance, devices which are subject to higher current stresses require a larger chip size to reduce both the differential electrical resistance (lower conduction losses) and the thermal resistance (improved heat dissipation). Therefore, to quantitatively determine the minimum required chip area, accurate semiconductor loss and thermal models need to be defined.

The conduction characteristics of IGBTs and diodes are approximated as in Fig. 12. Considering R inversely proportional to the chip area A leads to the instantaneous conduction losses

where i is the conducted current and \(R^*\) is the IGBT/diode specific differential resistance (actual resistance multiplied with the chip area, which results in an area-independent characteristic figure, as known from unipolar power transistors [29]). By substituting in (35) the average and RMS current values derived in Sect. 4, the average conduction losses \(P_\text {cond}\) are obtained.

The selected switching loss model is described by (33) and (34), which assumes that all losses occur inside the IGBT. The proportionality terms \(k_\text {on}\), \(k_\text {off}\) and k are considered to be independent on A, as assumed in [6] and [30]. The average switching losses of a single device can be calculated numerically by identifying all hard turn-on and turn-off transitions within a \({3{\text {-}}\Phi }\) output period \(T = 1/f\), together with the switched voltage \(V_\text {sw}\) and current \(i_\text {sw}\) values, as

where \(N_\text {on}\) and \(N_\text {off}\) are respectively the number of hard turn-on and turn-off commutations of the considered device within T. It is important to separately calculate the switching losses for each device, since asymmetrical switching sequences can lead to an uneven loss distribution between devices of the same bridge-leg.

The junction-to-heatsink thermal resistance \(R_\text {th}\) model accounting for heat-spreading proposed in [31], i.e.

is finally considered. Each semiconductor junction temperature can thus be calculated as

where \(T_\text {hs} \! = \! {80}^\circ \hbox {C}\) is the heatsink temperature and \(P_\text {tot} = P_\text {cond} + P_\text {sw}\) is the average power loss in each device.

Leveraging these chip area dependent loss and thermal models, the algorithm used for determining the minimum required chip size illustrated in Fig. 16 is adopted. The semiconductor loss parameters \(V_\text {th}\), \(R^*\) and k provided in Table 5 are obtained by statistical fitting of the conduction and switching characteristics of the latest generation \({600} /{1200}\,\hbox {V}\) Trench and Field-Stop IGBTs and fast-recovery emitter-controlled diodes from Infineon [28]. Since these parameters are temperature dependent, the maximum admitted semiconductor junction temperature \(T_\text {j,max} = {125} ^\circ \hbox {C}\) is assumed as operating temperature from the beginning of the procedure, so that no additional iterative loop is required. A starting chip area value \(A_\mathrm {0} = {4}{{\hbox {mm}}^2}\) is considered due to practical manufacturing and wire-bonding limitations. Then, the chip size dependent electrical and thermal resistances are calculated, and the average conduction and switching losses in the design operating point are derived, leveraging the current stress and switching energy expressions obtained in Sect. 4. Finally, the chip junction temperature is calculated and compared to the maximum admitted value \(T_\text {j,max}\). If the maximum temperature limit is fulfilled, the chip area value is saved and the algorithm is ended, otherwise the chip size is increased and the procedure is repeated.

The chip area minimization algorithm is run for the nominal operating point and different values of \(f_\text {sw}\), selecting the minimum required chip size for each device to operate the converter at \(M \! = \! 0.85\) and \(\cos \varphi \! = \! 1\). By summing all IGBT and diode chip sizes, the total converter chip area is obtained.

5.3 Performance comparison

Following the described chip area minimization procedure, the SNPCC is compared to the most adopted converter topologies in industrial VSDs, namely the conventional 2-L converter and the 3-L NPC converter.

a Normalized RMS phase current ripple \(\Delta I_\text {RMS}/\Delta I_\text {n}\) multiplied by \(f_\text {sw,0}/f_\text {sw}\) (i.e. \(f_\text {sw,0} = {16}\,\hbox {kHz}\) is a reference switching frequency purely defined for normalization purposes) and b total semiconductor chip area \(A_\text {S}\) as functions of the converter switching frequency \(f_\text {sw}\) for the 2-L, 3-L NPC and 3-L SNPC converters, considering \(P = {7.5}\,\hbox {kW}\), \(V_\text {dc} = {800}\,\hbox {V}\), \(M = 0.85\) and \(\cos \varphi = 1\). Conventional space vector modulation is assumed for the 2-L and 3-L NPC converters, while switching sequence 8 is considered for the SNPCC. A cross-over between the three \(A_\text {S}\) curves is observed in (b), around \(f_\text {sw} = {16}\,\hbox {kHz}\), clearly defining the topology with the lowest chip area requirement over the complete frequency range. The design point for each converter is obtained adjusting \(f_\text {sw}\) to yield the same \(\Delta I_\text {RMS}\), assuming the 2-L converter operated at 16\(\,\hbox {kHz}\) as reference design. This procedure is illustrated graphically, resulting in \(f_\text {sw} = {7}\,\hbox {kHz}\) for the 3-L NPC converter and in \(f_\text {sw} = {9}\,\hbox {kHz}\) for the 3-L SNPCC (i.e. \(f_\text {sw} = f_\text {s}\), cf. Table 3). A complete comparison of the performance results is reported in Table 6. The SNPCC total semiconductor area is divided between the 2-L inverter (\(A_\text {S,I}\)) and the 3-L SM (\(A_\text {S,M}\)), as highlighted in the pie chart

Figure 17a and b shows the trends of the total RMS current ripple \(\Delta I_\text {RMS}\) and the total semiconductor chip area \(A_\text {S}\) as functions of \(f_\text {sw}\), assuming conventional space vector modulation for the 2-L and the 3-L NPC converters, while considering switching sequence 8 for the SNPCC. The results obtained for the traditional 2-L and 3-L converter topologies are in good agreement with [6]. As a further confirmation of the adopted methodology, the minimum chip sizes obtained for all IGBTs result in device RMS current densities in the range of \({80}{-}{120}~{\mathrm{A}}/\hbox {mm}^{2}\), depending on the semiconductor breakdown voltage (i.e., 600\(\,\hbox {V}\), \({1200}\,\hbox {V}\)) and the switching frequency (i.e., which determines switching losses). This is in close agreement with the typical value of around \({100}\,{\mathrm{A}}/\hbox {mm}^{2}\) at nominal current for IGBTs of these voltage classes [32]. It is observed that the 3-L NPC yields both the minimum \(\Delta I_\text {RMS}\) and the lowest chip area increase with \(f_\text {sw}\). Nevertheless, the SNPCC requires a lower \(A_\text {S}\) at low frequencies, since it features less semiconductor devices. If a conventional 16\(\,\hbox {kHz}\) operating switching frequency is assumed for the 2-L converter, the switching frequencies of the 3-L NPC and 3-L SNPC converters can be adjusted to ensure the same \(\Delta I_\text {RMS}\) stress on the driven machine. This calculation process is graphically illustrated in Fig. 17 and the results are reported in Table 6.

The 2-L converter shows the worst overall performance, as already expected from previous analyses [3, 5, 6]. The 3-L SNPCC instead requires the lowest total semiconductor chip area and offers an efficiency comparable to the one of the 3-L NPC converter. Moreover, due to its lower number of transistors, it requires 2 less gate driver circuits, as well as 6 less diodes, further reducing the total part count and overall complexity. Therefore, the SNPCC represents a promising alternative to traditional industrial VSD solutions, particularly in those applications which require relatively low switching frequency. The results of this analysis substantiate and supplement the findings reported in [9, 10].

To further enhance the performance comparison among the 3-L SNPC switching sequences, the chip area minimization procedure illustrated in Fig. 16 is carried out for all modulation strategies, considering nominal operating conditions. The same approach described in Fig. 17 is adopted, adjusting the switching frequency of each modulation strategy to achieve the same \(\Delta I_\text {RMS}\) as the 2-L converter operated at \({16}\,\hbox {kHz}\). Once the switching frequency is selected, the minimum required chip area for each semiconductor device is identified and the converter losses are calculated. It is worth noting that this comparative evaluation is no longer independent of the converter power level and switching frequency (i.e., as opposed to the normalized comparison reported in Fig. 15), as the converter power level affects the conduction losses and the required chip size, while the selected switching frequency modifies the relative contribution of the switching losses to the total converter loss. Therefore, the results of this comparison do not have general validity but are specific for the considered converter specifications. Figure 18a, b and c shows the adjusted switching frequency \(f_\text {sw}\), the required semiconductor chip area \(A_\text {S}\), and the generated semiconductor loss \(P_\text {semi}\) for all modulation strategies, respectively. The figures also indicate the distribution between the 3-L SM and the 2-L inverter stages. The overall semiconductor efficiency \(\eta _\text {semi}\) is shown in Fig. 18d. As expected from the previous analysis (see Fig. 15), it is found that switching sequence 8 achieves the best performance in terms of converter losses and efficiency, while requiring the minimum semiconductor chip area. Again, switching sequence S achieves similar results to sequence 8 but remains less attractive, as it features larger variations in terms of \(\Delta I_\text {RMS}(M)\) (see Fig. 11) and \(E_\text {sw}(\varphi )\) (see Fig. 14).

Overview of the performance achieved by the 3-L SNPCC according to the chip area minimization procedure illustrated in Fig. 16 for different modulation strategies. \(P = {7.5}\,\hbox {kW}\), \(V_\text {dc} = {800}\,\hbox {V}\), \(M = 0.85\) and \(\cos \varphi = 1\) are considered (i.e., nominal operation). The switching frequency of each modulation strategy is adjusted to yield the same \(\Delta I_\text {RMS}\) as the 2-L converter operated at 16\(\,\hbox {kHz}\), as in Fig. 17. a Switching frequency \(f_\text {sw}\), b total semiconductor chip area \(A_\text {S}\) and c total semiconductor losses \(P_\text {semi}\), divided between the 3-L SM and the 2-L inverter stages. d overall semiconductor efficiency \(\eta _\text {semi}\). Sequence C is not present since \(M \! > \! 1/\sqrt{3}\), while sequence 8 results the best performing in terms of minimum semiconductor chip area, minimum semiconductor loss and maximum converter efficiency (\(\star \))

6 Conclusion

The SNPCC has not received much attention in literature so far, nevertheless it appears as a promising candidate for robust and cost-sensitive industrial drive applications, e.g. fans, pumps, etc., since it is able to generate a multi-level output voltage waveform adopting less active devices with respect to traditional 3-L converters.

This paper provides a complete investigation of the SNPCC operation, including a novel analysis of the DM and CM voltage formation process. Several modulation strategies are introduced according to a specific set of rules, including both symmetric and asymmetric pulse patterns. For each of these strategies, a complete analytical and/or numerical evaluation of the major component stresses is carried out, including the RMS ripple of the current supplied to the driven machine, the RMS current in the DC-link capacitors and the conduction/switching losses in the semiconductor devices. Based on the calculated stresses, the best performing modulation strategy for the application at hand is selected. Finally, considering a 7.5\(\,\hbox {kW}{\,3{\text {-}}\Phi }\) system, the minimum semiconductor chip areas required by the 2-L, 3-L NPC and 3-L SNPC converters are investigated. It is found that the SNPCC requires the least total chip area below a defined switching frequency and offers comparable efficiency as the conventional 3-L NPC converter for the same harmonic current stress on the driven machine, resulting an excellent candidate for cost-sensitive low-frequency industrial drive systems.

References

BMW i3 Teardown Analysis Study. Munro and Associates Inc., Tech. Rep. (2014)

Jahns TM, Dai H (2017) The past, present, and future of power electronics integration technology in motor drives. CPSS Trans Power Electron Appl 2(3):197–216. https://doi.org/10.24295/CPSSTPEA.2017.00019

Teichmann R, Bernet S (2005) A comparison of three-level converters versus two-level converters for low-voltage drives, traction, and utility applications. IEEE Trans Ind Appl 41(3):855–865. https://doi.org/10.1109/TIA.2005.847285

Guacci M, Azurza Anderson J, Pally KL, Bortis D, Kolar JW, Kasper MJ, Sanchez J, Deboy G (2020) Experimental characterization of silicon and gallium nitride 200 V power semiconductors for modular/multi-level converters using advanced measurement techniques. IEEE J Emerg Selected Topics Power Electron 8(3):2238–2254. https://doi.org/10.1109/JESTPE.2019.2944268

Cittanti D, Guacci M, Mirić S, Bojoi R, Kolar JW (2020) Comparative evaluation of 800V DC-link three-phase two/three-level sic inverter concepts for next-generation variable speed drives. In: Proc. of the International Conference on Electrical Machines and Systems (ICEMS), Hamamatsu, Japan, pp 1699–1704. https://doi.org/10.23919/ICEMS50442.2020.9291123

Schweizer M, Friedli T, Kolar JW (2013) Comparative evaluation of advanced three-phase three-level inverter/converter topologies against two-level systems. IEEE Trans Ind Electron 60(12):5515–5527. https://doi.org/10.1109/TIE.2012.2233698

Mohan D, Zhang X, Foo G (2015) Direct torque control of sparse three level inverter fed low voltage IPMSM drive. In: Proceedings of the IEEE International Electric Machines & Drives Conference (IEMDC), Coeur d’Alene, ID, USA, pp 929–935. https://doi.org/10.1109/IEMDC.2015.7409172

Rojas R, Ohnishi T, Suzuki T (1993) Simple structure and control method for a neutral-point-clamped PWM inverter. In: Proceedings of the Power Conversion Conference (PCC), Yokohama, Japan, pp 26–31. https://doi.org/10.1109/PCCON.1993.264252

Lange A, Piepenbreier B (2017) space vector modulation for three-level simplified neutral point clamped (3L-SNPC) inverter. In: Proceedings of the IEEE 18th Workshop on Control and Modeling for Power Electronics (COMPEL), Stanford, CA, USA. https://doi.org/10.1109/COMPEL.2017.8013399

Lange A, Lautner J, Piepenbreier B (2018) High efficiency three-level simplified neutral point clamped (3L-SNPC) inverter with GaN-Si hybrid structure. In: Proceedings of the International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management (PCIM), Nuremberg, Germany

Klumpner C, Lee M, Wheeler P (2006) A new three-level sparse indirect matrix converter. In: Proceedings of the 32nd Annual Conference of the IEEE Industrial Electronics Society (IECON), Paris, France, pp 1902–1907. https://doi.org/10.1109/IECON.2006.347958

Lee MY, Wheeler P, Klumpner C (2010) Space-vector modulated multilevel matrix converter. IEEE Trans Ind Electron 57(10):3385–3394. https://doi.org/10.1109/TIE.2009.2038940

Ngo T, Foo G, Baguley C, Mohan D, Xinan Z (2016) A novel direct torque control strategy for interior permanent magnet synchronous motors driven by a three-level simplified neutral point clamped inverter. In: Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA. https://doi.org/10.1109/ECCE.2016.7854729

Ngo T, Foo G, Baguley C (2016) A predictive torque control strategy for interior permanent magnet synchronous motors driven by a three-level simplified neutral point clamped inverter. In: Proceedings of the 42nd Annual Conference of the IEEE Industrial Electronics Society (IECON), Florence, Italy, pp 2648–2653. https://doi.org/10.1109/IECON.2016.7793544

Wang F, Li Z, Liu Z (2020) Model predictive control methods for three-level sparse neutral point clamped inverter. IEEE J Emerg Select Top Power Electron 8(4):4355–4366. https://doi.org/10.1109/JESTPE.2019.2914764

Wang F, Li Z, Tong X, Chen L (2019) Modeling, analysis and evaluation of modified model predictive control method for parallel three-level simplified neutral point clamped inverters. IEEE Access 7:185349–185359. https://doi.org/10.1109/ACCESS.2019.2961054

Zhang X, Foo GHB, Jiao T, Ngo T, Lee CHT (2019) A simplified deadbeat based predictive torque control for three-level simplified neutral point clamped inverter fed IPMSM drives using SVM. IEEE Trans Energy Conv 34:1906–1916. https://doi.org/10.1109/TEC.2019.2933465

Wu B, Narimani M (2017) High-power converters and AC drives, 2nd edn. Wiley, Hoboken

Ogasawara S, Akagi H (1993) Analysis of variation of neutral point potential in neutral-point-clamped voltage source PWM inverters. In: Proceedings of the 28th IEEE Industry Applications Society Annual Meeting (IAS), Toronto, Ontario, Canada, pp 965–970. https://doi.org/10.1109/IAS.1993.299015

Antivachis M, Anderson JA, Bortis D, Kolar JW (2020) Analysis of a synergetically controlled two-stage three-phase DC/AC buck-boost converter. CPSS Trans Power Electron Appl 5(1):34–53. https://doi.org/10.24295/CPSSTPEA.2020.00004

Bradley K, Cao W, Clare J, Wheeler P (2008) Predicting inverter-induced harmonic loss by improved harmonic injection. IEEE Trans Power Electron 23(5):2619–2624. https://doi.org/10.1109/TPEL.2008.2002329

Dalessandro L, Round SD, Drofenik U, Kolar JW (2008) Discontinuous space-vector modulation for three-level PWM rectifiers. IEEE Transactions on Power Electronics 23(2):530–542. https://doi.org/10.1109/TPEL.2007.915160

Kolar JW, Ertl H, Zach FC (1990) Minimization of the harmonic RMS content of the mains current of a PWM converter system based on the solution of an extreme value problem. In: Proceedings of the 4th International Conference on Harmonics in Power Systems (ICHPS), Budapest, Hungary

Kolar JW, Ertl H, Zach FC (1989) Calculation of the passive and active component stress of three-phase PWM converter systems with high pulse rate. In: Proceedings of the 3rd European Conference on Power Electronics and Applications (EPE), vol 3, Aachen, pp 1303–1311

Kolar JW, Round SD (2006) Analytical calculation of the RMS current stress on the DC-link capacitor of voltage-PWM converter systems. IEE Proc Electr Power Appl 153(4):535–543. https://doi.org/10.1049/ip-epa:20050458

Kolar JW, Ertl H, Zach FC (1995) A comprehensive design approach for a three-phase high-frequency single-switch discontinuous-mode boost power factor corrector based on analytically derived normalized converter component ratings. IEEE Trans Ind Appl 31(3):569–582. https://doi.org/10.1109/28.382118

IXYS Power. www.ixyspower.com. Accessed: 24 Jul 2020

Infineon Technologies. www.infineon.com. Accessed 24 Jul 2020

Baliga B (1989) Power semiconductor device figure of merit for high-frequency applications. IEEE Electron Device Lett 10(10):455–457. https://doi.org/10.1109/55.43098

Huber JE, Kolar JW (2017) Optimum number of cascaded cells for high-power medium-voltage AC–DC converters. IEEE J Emerg Select Top Power Electron 5(1):213–232. https://doi.org/10.1109/JESTPE.2016.2605702

Friedli T, Kolar JW (2009) A semiconductor area based assessment of AC motor drive converter topologies. In: Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Washington, DC, USA, pp 336–342. https://doi.org/10.1109/APEC.2009.4802678

Baliga BJ (2015) The IGBT device: physics, design and applications of the insulated gate bipolar transistor, 1st edn. Elsevier, Oxford

Funding

Open access funding provided by Politecnico di Torino within the CRUI-CARE Agreement.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Appendices

Appendix 1 Analytical RMS machine current ripple

The analytical derivation of the RMS current ripple through the inductive load of a \({3{\text {-}}\Phi }\) 2-L converter is reported in [23]; a similar procedure is applied herein to the SNPCC, considering the RMS ripple of the current supplied to the driven machine. The local RMS current ripple can be obtained by integrating and averaging the ripple contributions of the three phases over a switching period \(T_\text {sw} = 1/f_\text {sw}\) as

where \(\Delta i_\alpha \) and \(\Delta i_\beta \) are the current ripple components with respect to the \(\alpha \beta \)-axes defined in space vector theory. It is worth mentioning that symmetric pulse patterns are completely identified within half a switching period, however asymmetric sequences require the total period to be fully described. Therefore, the integration interval of (39) has been defined in the most general way.

The expressions of the instantaneous \(\Delta i_\alpha \) and \(\Delta i_\beta \) can be obtained by integration of the high-frequency DM voltage component at the converter \({3{\text {-}}\Phi }\) output, resulting in a piece-wise linear function. Being N the total number of transitions in the switching sequence (i.e. 6, 8 or 10), the current ripple values at each state transition are defined as

where \(\vec {V}_{\mathrm {k},\alpha \beta }\) is the applied space vector, \(\vec {V}^*_{\alpha \beta }\) is the reference voltage vector, \(\delta _\mathrm {k} T_\text {sw}\) is the state dwell-time and L is the machine phase inductance. The main terms of (40) are illustrated in Fig. 19, considering sequence 8. In order to obtain a current ripple waveform with zero average over a switching period, the starting value \(\vec {\Delta i}_{0,\alpha \beta }\) must be equal to the ripple average changed in sign, which can be derived in a first iteration considering \(\vec {\Delta i}_{0,\alpha \beta } \! = \! 0\) as

A zero current ripple average is already ensured by symmetric pulse patterns, but it is not guaranteed for asymmetric ones.

Instantaneous waveforms considering a switching period in  (\(\vartheta = {15}^{\circ }\), cf. Fig. 2d), area

(\(\vartheta = {15}^{\circ }\), cf. Fig. 2d), area (\(M = 0.85\)) and sequence 8 (cf. Table 3). a \(\alpha \beta \) voltage waveforms and b \(\alpha \beta \) current ripple waveforms. The distinctive behavior of the current ripple for asymmetric pulse patterns is shown, i.e. the ripple value is nonzero at the beginning, middle and end of the switching period

(\(M = 0.85\)) and sequence 8 (cf. Table 3). a \(\alpha \beta \) voltage waveforms and b \(\alpha \beta \) current ripple waveforms. The distinctive behavior of the current ripple for asymmetric pulse patterns is shown, i.e. the ripple value is nonzero at the beginning, middle and end of the switching period

The RMS value of \(\vec {\Delta i}_{\alpha \beta }\) can be calculated by exploiting its piece-wise linear properties:

Finally, substituting (42) in (39), the total RMS current ripple over one \({3{\text {-}}\Phi }\) output period is obtained by averaging \(\Delta i^2_\text {RMS}\) over a single sector (i.e. 60\(^\circ \)), as

, divided between area

, divided between area and area

and area . The kind of hard commutation (turn-on or turn-off) and the involvement of the 3-L matrix (\(\mathrm {M}\)) or the 2-L inverter (\(\mathrm {I}\)) in the switching transition are indicated by the switching loss coefficient k

. The kind of hard commutation (turn-on or turn-off) and the involvement of the 3-L matrix (\(\mathrm {M}\)) or the 2-L inverter (\(\mathrm {I}\)) in the switching transition are indicated by the switching loss coefficient kThe presented procedure is here applied to sequence 8 for demonstration purposes, resulting in two different normalized expressions for area and area

and area , respectively

, respectively

where \(\Delta I_{\text {n}}\) is defined in (25).

Appendix 2 Analytical switching losses

To calculate the converter switching losses, the switched voltage \(V_\text {sw}\) and current \(i_\text {sw}\) values at each space vector transition (i.e. switching state change) must be known. It can be demonstrated that the total switching losses of both the 2-L inverter and the 3-L SM stages depend on the sequence starting vector and have sector periodicity, therefore the following analysis focuses only on sector . The current direction is of primary importance in determining whether the switching transition of a bridge-leg causes a hard turn-on or turn-off. Neglecting the switching frequency current ripple and adopting the simplified linear model reported in (33), the average converter switching energy loss can be calculated as

. The current direction is of primary importance in determining whether the switching transition of a bridge-leg causes a hard turn-on or turn-off. Neglecting the switching frequency current ripple and adopting the simplified linear model reported in (33), the average converter switching energy loss can be calculated as

where N is the number of transitions in the switching sequence (i.e. 6, 8 or 10) and \(k_\text {j}\) depends on the semiconductor technology of the device involved in the transition (i.e. different between the 2-L inverter and the 3-L SM) and on whether the transition causes a hard turn-on or turn-off (i.e. depending on the switched current direction). Since the instantaneous switched current can be either positive or negative, (46) can be expressed as

where \(I_{\text {sw,j},+}\) and \(I_{\text {sw,j},-}\) are respectively the sector-averaged positive and negative (changed in sign) switched currents involved in the j-th transition, while \(k_{\text {j},+}\) and \(k_{\text {j},-}\) are the related switching loss coefficients (i.e. indicating either a turn-on or turn-off commutation). As the switched current can assume any of the \({3{\text {-}}\Phi }\) sinusoidal output current values, 6 different \(I_\text {sw,j}\) terms are derived, i.e. the positive and negative averages of each \({3{\text {-}}\Phi }\) sinusoidal output current inside  .

.

The current averaging procedure and its results are illustrated in Fig. 20, however the analytical expressions are not reported for conciseness reasons. Moreover, Table 7 summarizes the switched current and voltage values involved in each space vector transition, together with the kind of hard commutation (i.e. turn-on or turn-off) and the semiconductor technology of the device being switched, i.e. \(k_\text {on,M}/k_\text {off,M}\) for the 3-L SM devices and \(k_\text {on,I}/k_\text {off,I}\) for the 2-L inverter devices.

Considering the switching sequence mirroring process between odd and even sectors described in Sect. 3, it is found that each converter bridge-leg transition is repeated in the same direction in the diametrically opposite sector (i.e. at \(\vartheta + {180}^\circ \)), however the switched current value is changed in sign. Therefore, simplified expressions of the 3-L SM and 2-L inverter switching losses are derived by averaging the loss contributions of both sequence combinations, obtaining

where \(N_\text {M}\) and \(N_\text {I}\) are respectively the number of switching transitions involving the 3-L SM and the 2-L inverter, while \(k_\text {M} = k_\text {on,M} + k_\text {off,M}\) and \(k_\text {I} = k_\text {on,I} + k_\text {off,I}\) are the total switching loss coefficients. Leveraging (48) and (49), together with the semiconductor device parameters reported in Table 5, it is possible to analytically derive the switching losses for all modulation strategies. The resulting expressions for sequence 8 are here reported for demonstration purposes, divided between the 3-L SM contribution

which is independent on the sector area, and the 2-L inverter contribution in area and area

and area , respectively

, respectively

The obtained expressions are characterized by a 180\(^\circ \) periodicity with respect to the power factor angle \(\varphi \) and are graphically reported in normalized form in Fig. 21.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Cittanti, D., Guacci, M., Mirić, S. et al. Analysis and performance evaluation of a three-phase sparse neutral point clamped converter for industrial variable speed drives. Electr Eng 104, 623–642 (2022). https://doi.org/10.1007/s00202-021-01290-w

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00202-021-01290-w

and area

and area ,

,

and b

and b

and area

and area in sector

in sector . The angle

. The angle

. Varying

. Varying

and (b) area

and (b) area . The loss expressions

. The loss expressions