Abstract

This paper presents a simple but accurate normalized nonlinear large-signal semiempirical MOS transistor model to be used in monolithic RF Class A-to-C PAs. MOS transistor characteristics, saved in lookup tables, are extracted for different PVT corners, allowing the study of the PA performance spread. Model accuracy is ratified by the excellent matching obtained when comparing data algebraically calculated with electrical simulations of hundreds of PAs, and with the measurement data of a fabricated 2.4 GHz PA.

Similar content being viewed by others

Notes

In our case, they are metal–metal capacitors and ideal models can be considered valid up to, at least, ten gigahertz.

If Nsamp discrete samples at instants tn = n/(f0Nsamp,), n = 0,…Nsamp − 1, are used to define a periodic function, p(t), its harmonics can be obtained by discrete-time Fourier transform: \( F_{k} = ({1 \mathord{\left/ {\vphantom {1 {N_{\text{samp}} }}} \right. \kern-0pt} {N_{\text{samp}} }})\,({\text{FFT}}{\{ }p(t_{n} ){\} })_{k} \).

References

N. Barabino, R. Fiorelli, F. Silveira, Efficiency based design flow for fully-integrated class C RF power amplifiers in nanometric CMOS, in Proceedings of 2010 IEEE International Symposium on Circuits and Systems (ISCAS) (2010), pp. 2223–2226. https://doi.org/10.1109/ISCAS.2010.5537207

C. Bernier, F. Hameau, G. Billiot, E. de Foucauld, S. Robinet, D. Lattard, J. Durupt, F. Dehmas, L. Ouvry, P. Vincent, An ultra low power SoC for 2.4 GHz IEEE802.15.4 wireless communications, in 34th European Solid-State Circuits Conference (ESSCIRC) (2008), pp. 426–429. https://doi.org/10.1109/ESSCIRC.2008.4681883

C. Bowick, RF Circuit Design (Elsevier, Burlington, 2007)

P. Choi, H.C. Park, S. Kim, S. Park, I. Nam, T.W. Kim, S. Park, S. Shin, M.S. Kim, K. Kang, Y. Ku, H. Choi, S.M. Park, K. Lee, An experimental coin-sized radio for extremely low-power WPAN (IEEE802.15.4) application at 2.4 GHz. IEEE J. Solid-State Circuits 38(12), 2258–2268 (2003). https://doi.org/10.1109/JSSC.2003.819083

S. Cripps, RF Power Amplifiers for Wireless Communications, 2nd edn. (Artech House, Norwood, 2006). ISBN: 9781596930186

P. Dal Fabbro, M. Kayal, Design of the dynamic supply CMOS RF power amplifier, in Linear CMOS RF Power Amplifiers for Wireless Applications, ed. by P. Dal Fabbro, M. Kayal (Springer, Berlin, 2010), pp. 17–38. https://doi.org/10.1007/978-90-481-9361-5

R. Fiorelli, E. Peralias, F. Silveira, LC-VCO design optimization methodology based on the gm/ID ratio for nanometer CMOS technologies. IEEE Trans. Microw. Theory Tech. 59(7), 1822–1831 (2011). https://doi.org/10.1109/TMTT.2011.2132735

R. Fiorelli, E. Peralías, Semi-empirical RF MOST model for CMOS 65 nm technologies: theory, extraction method and validation. Integr. VLSI J. 52(1), 228–236 (2016). https://doi.org/10.1016/j.vlsi.2015.07.018

R. Fiorelli, F. Silveira, E. Peralías, MOST moderate-weak-inversion region as the optimum design zone for CMOS 2.4-GHz CS-LNAs. IEEE Trans. Microw. Theory Tech. 62(3), 556–566 (2014). https://doi.org/10.1109/TMTT.2014.2303476

R. Gupta, B.M. Ballweber, D.J. Allstot, Design and optimization of CMOS RF power amplifiers. IEEE J. Solid-State Circuits 36(2), 166–175 (2001). https://doi.org/10.1109/4.902757

P.G.A. Jespers, B. Murmann, Systematic Design of Analog CMOS Circuits (Cambridge University Press, Cambridge, 2017). https://doi.org/10.1017/9781108125840

Y.J. Kim, I.-C. Hwang, D. Baek, A switchless Zigbee frontend transceiver with matching component sharing of LNA and PA. IEEE Microwave Wirel. Compon. Lett. 20(9), 516–518 (2010). https://doi.org/10.1109/LMWC.2010.2056676

W. Kluge, F. Poegel, H. Roller, M. Lange, T. Ferchland, L. Dathe, D. Eggert, A fully integrated 2.4-GHz IEEE 802.15.4-compliant transceiver for ZigBee(TM) applications. IEEE J. Solid-State Circuits 41(12), 2767–2775 (2006). https://doi.org/10.1109/JSSC.2006.884802

W. Liu, J. Chen, X. Liu, H. Wang, N. Wu, A 2.4 GHz low power CMOS transceiver for LR-WPAN applications. Sci. China Inf. Sci. 57(8), 1–13 (2014). https://doi.org/10.1007/s11432-013-4981-8

T.K. Nguyen, V. Krizhanovskii, J. Lee, S.K. Han, S.G. Lee, N.S. Kim, C.S. Pyo, A low-power RF direct-conversion receiver/transmitter for 2.4-GHz-band IEEE 802.15.4 standard in 0.18-μm CMOS technology. IEEE Trans. Microw. Theory Tech. 54(12), 4062–4071 (2006). https://doi.org/10.1109/TMTT.2006.885556

A. Raghavan, N. Srirattana, J. Laskar, Modeling and Design Techniques for RF Power Amplifiers (Wiley-IEEE Press, Hoboken, 2008). https://doi.org/10.1002/9780470228319

J. Ramos, K. Francken, G.G.E. Gielen, M.S.J. Steyaert, An efficient, fully parasitic-aware power amplifier design optimization tool. IEEE Trans. Circuits Syst. I Regul. Pap. 52(8), 1526–1534 (2005). https://doi.org/10.1109/TCSI.2005.851677

N. Saputra, J. Long, A fully-integrated, short-range, low data rate FM-UWB transmitter in 90 nm CMOS. IEEE J. Solid-State Circuits 46(7), 1627–1635 (2011). https://doi.org/10.1109/JSSC.2011.2144050

A. Shameli, P. Heydari, Ultra-low power RFIC design using moderately inverted MOSFETs: an analytical/experimental study, in IEEE Radio Frequency Integrated Circuits (RFIC) Symposium (2006), pp. 470–473. https://doi.org/10.1109/RFIC.2006.1651193

F. Silveira, D. Flandre, P.G.A. Jespers, A gm/ID based methodology for the design of CMOS analog circuits and its application to the synthesis of a silicon-on-insulator micropower OTA. IEEE J. Solid-State Circuits 31(9), 1314–1319 (1996). https://doi.org/10.1109/4.535416

H. Solar-Ruiz, Roc Berenguer Pérez, Linear CMOS RF Power Amplifiers: A Complete Design Workflow (Springer, Berlin, 2014). https://doi.org/10.1007/978-1-4614-8657-2

A. Zolfaghari, B. Razavi, A low-power 2.4-GHz transmitter/receiverCMOS IC. IEEE J. Solid-State Circuits 38(2), 176–183 (2003). https://doi.org/10.1109/JSSC.2002.807580

Acknowledgements

This work was supported in part by FEDER funds through the Andalusian Government Project P09-TIC-5386, Spanish Government MAE-AECID grants; Uruguayan ANII Grant BE-POS-2010-2442 and MOSIS Research Program.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Appendix

Appendix

1.1 Appendix A: Expressions of PA Efficiencies: ηMOS and ηFMW

This section collects the set of equations necessary to size the PA MOST, as well as the design efficiencies.

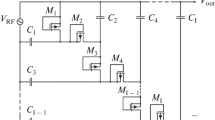

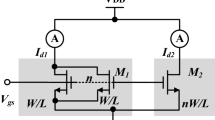

It is assumed that gate and drain voltage waveforms (8) and (11) are known, and therefore, normalized memoryless drain current has been estimated by (2). Impedance condition (9) is fulfilled when the load seen at M1 drain at f0 is a resistance RFNW; then, MOST inverts the gate waveform provoking the anti-phase of the first harmonic of drain voltage signal, ϕD1 ≈ ϕG + π, and the power PFNW entering the FNW shown in Fig. 6b at f0 is:

where definitions of (10) and (11) have been used.

The output power Po at f0 can be seen as the remaining power delivered to the load after a fraction of PFNW and Ploss is lost in the parasitic resistance Rind(f0) of the picked inductor:

Solving for RFNW,

Now, the first harmonic of drain current irD is determined as

The MOST width W can now be derived considering the normalization ratio between I1 and \( \widehat{I}_{1} \):

Now, the value of MOST output capacitance, CoMOS, is estimated from LUT ΛCoMOS: \( C_{\text{oMOS}} \approx W \cdot \hat{C}_{\text{oMOS}} (V_{\text{G}}^{\text{DC}} ,V_{\text{G}}^{\text{RF}} ) \).

The total average power consumed by the PA, PDC, is a function of \( \hat{I}_{\text{DC}} \), W and the supply voltage VDD as follows:

and the PA efficiency results as

where PFNW is the power injected into FNW, defined in (13).

MOST efficiency, ηMOS, results from (13), (15) and (18):

and the output network efficiency, ηFNW, from (15):

Note that, from (19), (20) and (21), the PA efficiency, η, is independent of the MOST size.

1.2 Appendix B: Expressions of Filtering Network Capacitances: Cop and Cos

This section assumes the rest of components in PA, MOST and inductor, are already known. Here, we will consider a more general case where the PA has a non-resistive load, \( Z_{L} = R_{L} + jX_{L} \). One of the requirements to achieve high-efficiency values at the working frequency f0 is to enforce that ZinFNW(f0) = RFNW, where this value must result from the parallel between two resistance values, the real part of inductor, Rind(f0), and a pure-resistive effective load, RL,eff(f0). This is, \( R_{\text{FNW}} = R_{\text{ind}} (f_{0} )||R_{{L,{\text{eff}}}} (f_{0} ) \).

The pure-resistive effective load is the transformation of load impedance, ZL, by the L–C network of FNW at f0 (see Fig. 6b). Since we have already sized the MOST and inductor, we have the impedance of L–C components to the left of Cos:

with \( R_{{L,{\text{eff}}}}^{ - 1} = R_{\text{FNW}}^{ - 1} - R_{\text{ind}}^{ - 1} (f_{0} ) \).

Then, the capacitors, Cop and Cos, are the elements that transform that impedance, Zm0, in the conjugate of the load impedance. When \( {\text{real}}(Z_{m0} ) > R_{L} \), a capacitive output network is not always possible, then the best procedure is to reject the present design and find another inductor with lower inductance until it verifies that \( {\text{real}}(Z_{m0} ) \le R_{L} \), and then a solution exists for the output capacitors. If it is defined that \( Z_{m0} = R_{m0} + jX_{m0} \), derived values for these components are:

1.3 Appendix C: Drain Voltage and Power of Output Signal

If it is assumed the normalized memoryless drain current is estimated as it was explained in Sect. 2.1, and all PA elements are sized according to previous appendices, an approximation to actual PA output and drain signals, vo(t), vD(t), are, respectively, determined by the FNW transimpedance and impedance functions, TR (s) and ZinFNW (s). This way, harmonics of these signals are:

where current harmonics are obtained by de-normalization

and network functions are:

with Yo the parallel complex admittance that gathers inductor Lo and CoMOS.

Power of output harmonics is:

and finally, the power gain is

Rights and permissions

About this article

Cite this article

Fiorelli, R., Barabino, N., Silveira, F. et al. Normalized Nonlinear Semiempirical MOST Model Used in Monolithic RF Class A-to-C PAs. Circuits Syst Signal Process 39, 2796–2821 (2020). https://doi.org/10.1007/s00034-019-01296-7

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-019-01296-7