Abstract

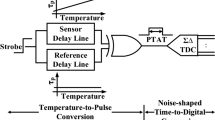

This paper presents a new time-mode duty-cycle-modulation-based high-accuracy temperature sensor. Different from the well-known \({\varSigma }{\varDelta }\) ADC-based readout structure, this temperature sensor utilizes a temperature-dependent oscillator to convert the temperature information into temperature-related time-mode parameter values. The useful output information of the oscillator is the duty cycle, not the absolute frequency. In this way, this time-mode duty-cycle-modulation-based temperature sensor has superior performance over the conventional inverter-chain-based time domain types. With a linear formula, the duty-cycle output streams can be converted into temperature values. The design is verified in 65nm standard digital CMOS process. The verification results show that the worst temperature inaccuracy is kept within 1\(\,^{\circ }\mathrm{C}\) with a one-point calibration from \(-\)55 to 125 \(^{\circ }\mathrm{C}\). At room temperature, the average current consumption is only 0.8 \(\upmu \)A (1.1\(\,\upmu \)A in one phase and 0.5 \(\upmu \)A in the other) with 1.2 V supply voltage, and the total energy consumption for a complete measurement is only 0.384 \({\hbox {nJ}}\).

Similar content being viewed by others

References

P. Arun, D. Griffith, A. Wang, A. P. Chandrakasan, G. Burra “A 120nW 18.5 kHz RC oscillator with comparator offset cancellation for \(\pm \)0.25 % temperature stability.” in Proceedings of the IEEE ISSCC Digest of Technical Papers (2013), pp. 184-185

P.K. Chen, C.C. Chen, C.C. Tsai, W.F. Lu, A time-to-digital-converter-based CMOS smart temperature sensor. IEEE J. Solid State Circuits 40(8), 1642–1648 (2005)

P. Chen, C.C. Chen, Y.H. Peng, K.M. Wang, Y.S. Wang, A time-domain SAR smart temperature sensor with curvature compensation and a 3\(\sigma \) inaccuracy of \(-\)0.4\(^{\circ }{}\)/0.6\(^{\circ }{}\) Over a 0\(^{\circ }{}\) to 90\(^{\circ }{}\) range. IEEE J. Solid State Circuits 45(3), 600–609 (2010)

R.P. Fisk, S.M. Rezaul Hasan, A calibration-free low-cost process-compensated temperature sensor in 130 nm CMOS. IEEE Sens. J. 11(12), 3316–3329 (2011)

A. Heidary, G. J. Wang, K. Makinwa, G. Meijer “A BJT-based CMOS temperature sensor with a 3.6 \(pJ\)-resolution FoM.” in Proceedings of the IEEE ISSCC Digest of Technical Papers (2014), pp. 224–225

S. Hwang, J. Koo, K. Kim, H. Lee, C. Kim, A 0.008 mm\(^{2}\) 500 \(\mu \)W 469 kS/s frequency-to-digital converter based CMOS temperature sensor with process variation compensation. IEEE Trans. Circuits Syst. I 60, 2241–2248 (2013)

K. Kim, H. Lee, S. Jung, C. Kim “A 366 kS/s 400 \(\mu \) frequency-to-digital converter based CMOS temperature sensor utilizing multiphase clock,” in Proceedings of the IEEE Custom Integrated Circuits Conference (CICC) (2009), pp. 203–206

Y. Kim, P. Li, ‘A 0.003-\(mm^2\), 0.35-V, 82-pJ/conversion ultra-low power CMOS all digital temperature sensor for on-die thermal management. Analog Integr. Circuits and Signal Process. 75(1), 147–156 (2013)

C. Kunil, O. D. Bernal, D. Nuttman, M. Je “A precision relaxation oscillator with a self-clocked offset-cancellation scheme for implantable biomedical SOCs.” in Proceedings of the IEEE ISSCC Digest of Technical Papers (2009), pp. 402–403

M.A. Pertijs, J.H. Huijsing, Precision Temperature Sensors in CMOS Technology (Springer, Dordrecht, 2006)

K. Souri, Y.C. Chae, K. Makinwa, A CMOS temperature sensor with a voltage-calibrated inaccuracy of \(\pm \)0.15\(^{\circ }{}\) (3\(\sigma \)) from \(-\)55\(^{\circ }{}\) to 125\(^{\circ }{}\). IEEE J. Solid State Circuits 48(1), 292–301 (2013)

X. Tang, K. P. Pun, W. T. Ng “A 0.9V 5kS/s resistor-based time-domain temperature sensor in 90nm CMOS with calibrated inaccuracy of -0.6 \({\circ }{\rm C}\),” in 2013 IEEE Asian Solid-State Circuits Conference (ASSCC) (2013), pp. 169–172

E. Vittoz, J. Fellrath, CMOS analog integrated circuit based on weak inversion operation. IEEE J. Solid State Circuits 12(3), 224–231 (1977)

C.K. Wu, W. S. Chan, T.H. Lin “A 80kS/s 36\(\mu \)m CMOS”, in Proceedings Digest of Technical Papers VLSI Circuits (2011), pp. 222–223

Acknowledgments

This work was supported by VIRTUS, IC Design Centre of Excellence, Nanyang Technological University.

Author information

Authors and Affiliations

Corresponding author

Appendices

Appendix 1: Proof of Choosing NMOS Transistors for PTAT Current Generator

Although bipolar transistors have better linearity than MOS transistors in subthreshold region, there are two reasons for the utilizing of MOS transistors in this design.

The first consideration is the proper operation of the PMOS current source transistors. As the supply voltage is only 1.2V and the threshold voltages of the transistors are approximated to 0.5 V, the value of \(V_{NS}\) is around 0.5 V in room temperature. If bipolar transistors are adopted, \(V_{NS}\) becomes greater than 0.6 V in room temperature, which will drive the current source transistors into triode region. The accuracy of current mirroring will be affected.

On the other hand, the performance of parasitic bipolar transistors (PNPs) is not excellent in deep submicron processes. Based on simulations of the PNPs, the current gain \(\beta \) (current ratio of \(I_C\) over \(I_B\)) is even less than 1, which means the base current becomes comparable to the collector current.

As in most calculations, the base current is ignored based on large \(\beta \) value and the emitter current is supposed to be equal to the collector current. However, due to small \(\beta \) values, the errors of \(V_{BE}\) caused by \(\beta \)s cannot be neglected in the design.

In Eqs. (10–14), two bipolar transistors \(Q_1\) and \(Q_2\) are biased equally by \(I_{\text {PTAT}}\). Each one has a saturation current \(I_S\) and current gain \(\beta \) accordingly. The bias current is generated by \({\varDelta }V_{BE}\) crossing resistor \(R_b\). As shown in Eq. (13), the final PTAT current includes the parameter \(\beta \). Unfortunately, \(\beta _1\) and \(\beta _2\) are not equal. Therefore, significant error appears with difference of \(\beta \)s .

Additionally, the value of \(\beta \)s is not flat when the emitter currents are swept. It is better to bias the PNPs with at least 1 \(\upmu A\) currents for operation in the flat region. Such large biasing current is not reasonable in the proposed application. Therefore, NMOS transistors instead of PNPs are chosen in the design.

Appendix 2: Evaluation of the Influence of Mismatches

(1) Mismatch of Capacitors

For a10 \(\upmu \)m x10 \(\,\upmu \)m MIM capacitor, \({\varDelta }\)C/C is approximated to 0.01 % according to the tech files provided by the foundry. In the proposed design, 6pF for C1 and C2 is chosen (reasons will be calculated in the following answer) and the capacitor’s mismatch is \(100/2500\times 0.01\,\%\,=\,4\times 10^{-6}\).

Employing Eq. (5):

Considering the mismatch between \(C_1\) and \(C_3\), assume \(C_3\) = (1+\({\varDelta }\)C/C)\(C_1\), the above equation becomes:

As the values of duty cycle are within 0.4 to 0.7 in the proposed design, the same range can be applied to \(t_1/(t_1+t_3 )\). Therefore, the mismatch caused \(\upmu \) error (duty-cycle error) is less than \(0.7\times 4\times 10^{-6}\). When the duty-cycle error is converted into actual temperature error, it is less than \(2.8\times 10^{-6}\times 600 \,\) = 1.68m\(\,^{\circ }\)C, which can be ignored in the proposed application.

(2) Mismatch of Currents

Using the same analysis for the mismatch of capacitors, assume \(I_3=(1+{\varDelta }I/I_1) I_1\), Eq. (5) becomes:

With the adopted DEM technique (just 3 more pairs of switches, negligible area), the residue mismatch reduces from \(t_3/(t_1+t_3 ){\varDelta }I/I\) to \(t_3/(t_1+t_3 )({\varDelta }I/I)^2\). With a usual current mirror inaccuracy of 1 %, the residue is less than \(0.7\times (1\,\%)^2= 7\times 10^{-5}\) .

Related calculation can be found in page 60 of [10].

When it is converted into temperature error, it will be \(7\times 10^{-5}\times 600\) = 0.04\(\,^{\circ }\)C, which can be ignored in the proposed application.

Rights and permissions

About this article

Cite this article

Zhu, D., Siek, L. & Zheng, Y. High-Accuracy Time-Mode Duty-Cycle-Modulation-Based Temperature Sensor for Energy-Efficient System Applications. Circuits Syst Signal Process 35, 2317–2330 (2016). https://doi.org/10.1007/s00034-015-0156-8

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-015-0156-8