Abstract

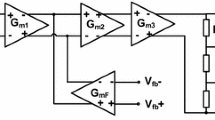

This paper proposes a new low-voltage high resolution complementary metal oxide semiconductor (CMOS) comparator circuit suitable for biosensor applications. The comparator compensates for differential input offset through single-ended sampled-data preamplification. Simulations were carried out using a 130 nm IBM CMOS (CMRF8SF) process technology. Monte Carlo simulations incorporating mismatch between devices (based on width and length of devices) indicate that the design is quite robust. The comparator has a differential input overdrive resolution of under 1 mV and a response time which is scalable. The capacity for offset compensation trades with the bandwidth of the comparator through the size of the device channel areas (Width × Length) of the transistors. The static micropower consumed by the comparator from a 0.5 V supply voltage is under 10 μW, making it extremely suitable for miniaturized implantable biosensor devices. In addition, the comparator uses a single clock scheme for the sampled-data operations, which eliminates the need for special clock generation circuitry.

Similar content being viewed by others

References

A. M. Abo, P. R. Gray, A 1.5 V 10-bit 14.3 MS/s CMOS pipeline analog-to-digital converter, IEEE J. Solid-State Circuits, vol. 34, no. 5, pp. 599–606, 1999.

A. Boni, G. Chiorboli, C. Morandi, Dynamic characterization of high-speed latching comparators, Electronic Letters, vol. 36, no. 5, pp. 402–403, 2000.

C. J. B. Fayomi, G. W. Roberts, M. Sawan, A 1-V 10-bit rail-to-rail successive approximation analog-to-digital converter in standard 0.18 μm CMOS technology, Proceedings IEEE Int. Symposium on Circuits and Systems, ISCAS’01, Sydney, Australia, pp. 460–463, 2001.

T. S. Gotarredona, B. L. Barranco, Systematic width-and-length dependent CMOS transistor mismatch characterization and simulation, Analog Integrated Circuits and Signal Processing, vol. 21, pp. 271–296, 1999.

S. Hosotani, T. Miki, A. Maeda, N. Yazawa, An 8-bit 20-MS/s CMOS A/D converter with 50 mW power consumption, IEEE J. Solid-State Circuits, vol. 25, no. 1, pp. 167–172, 1990.

Y. C. Hung, B. D. Liu, 1-V CMOS comparator for programmable analog rank order extractor, IEEE Trans. Circuits and Systems-I, vol. 50, no. 5, pp. 673–677, 2003.

Y. C. Hung, B. D. Liu, A low-voltage wide-input CMOS comparator for sensor application using back-gate technique, Biosensors & Bioelectronics, vol. 20, no. 1, pp. 53–59, 2004.

K. Kotani, T. Shibata, T. Ohmi, CMOS charge-transfer preamplifier for offset fluctuation cancellation in low power A/D converters, IEEE J. Solid-State Circuits, vol. 33, no. 5, pp. 762–769, 1998.

K. Kusumoto, A. Matsuzawa, K. Murata, A 10-b 20-MHz pipelined interpolating CMOS ADC, IEEE J. Solid-State Circuits, vol. 28, no. 12, pp. 1200–1206, 1993.

X. Li, Y. Yang, Z. Zhu, A CMOS 8-bit two-step A/D converter with low power consumption, Proceedings IEEE Int. Workshop VLSI Design and Video Technology, Suzhou, China, pp. 44–47, 2005.

M. J. M. Pelgrom, A. C. J. Duinmaijer, A. P. G. Welbers, Matching properties of MOS transistors, IEEE J. Solid-State Circuits, vol. 24, no. 5, pp. 1433–1440, 1989.

B. Razavi, B. A. Wooley, Design techniques for high-speed high-resolution comparators, IEEE J. Solid-State Circuits, vol. 27, no. 12, pp. 1916–1926, 1992.

Y. J. Ren, I. Karlsson, C. Svensson, A true single-phase-clock dynamic CMOS circuit technique, IEEE J. Solid-State Circuits, vol. 22, no. 5, pp. 899–901, 1987.

R. C. Taft, M. R. Tursi, A 100-MS/s 8-b CMOS subranging ADC with sustained parametric performance from 3.8 V down to 2.2 V, IEEE J. Solid-State Circuits, vol. 36, no. 3, pp. 331–337, 2001.

Application Note, Parameter Dependent Tolerances-Matching MOS Devices, Catena Software Ltd, January 2004.

CMRF8SF Model Reference Guide, IBM Corporation, March 2006.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Rezaul Hasan, S.M. An Offset Compensated Sampled-Data CMOS Comparator Circuit for Low-Power Implantable Biosensor Applications. Circuits Syst Signal Process 27, 351–366 (2008). https://doi.org/10.1007/s00034-008-9031-1

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-008-9031-1