Abstract

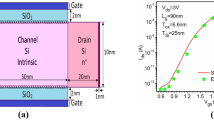

The customary MOSFETs can be supplanted by Tunnel Field Effect Transistors (TFETs), because of its capability of accomplishing sub-threshold swing (SS) under 60 mV/decade. Be that as it may, distinct requirements are to be met to ameliorate the operation of TFET with regard to greater on state current (ION) and smaller values of voltage (Vth). In this paper, the gate-all-around (GAA) TFET with hetero-junction at the source as the source is made with a low band-gap material i.e. Mg2Si is investigated and its comparative analysis has been done with the GAA-TFET with Si-source. Moreover, hetero-dielectric structure with high-k dielectric such as HfO2 has been implemented for the enhancement of the electrical performance of the device. The proposed device provides ION as 7.16 µA, SS of 7 mV/decade, Vth of 0.399 V and switching ratio of the order of 1013. The results obtained portray finer performance of Mg2Si/Si hetero-junction TFET when contrasted with ordinary Si GAA-TFET, regarding dc characteristics like ION, SS, Vth and the switching ratio ION/IOFF.

Similar content being viewed by others

Data Availability

The research data of this manuscript will not be available.

References

Mamidala JK, Vishnoi R, Pandey P (2016) Tunnel Field-effect Transistors (TFET): modelling and simulation. John Wiley & Sons, Hoboken

Ionescu AM, Riel H (2011) Tunnel field-effect transistors as energy-efficient electronic switches. Nature. https://doi.org/10.1038/nature10679

Vishnoi R, Kumar MJ (2014) Compact analytical drain current model of gate-all-around nanowire tunneling FET. IEEE Trans Electron Devices 61(7):2599–2603. https://doi.org/10.1109/TED.2014.2322762

Wong HSP (2002) Beyond the conventional transistor. IBM J Res Dev. https://doi.org/10.1147/rd.462.0133

Saurabh S, Kumar MJ (2016) Fundamentals of tunnel field-effect transistors (1st ed.). CRC Press. https://doi.org/10.1201/9781315367354

Taur Y, Ning TH (2009) Fundamentals of modern VLSI devices

Verhulst AS, Sorée B, Leonelli D, Vandenberghe WG, Groeseneken G (2010) Modeling the single-gate, double-gate, and gate-all-around tunnel field-effect transistor. J Appl Phys. https://doi.org/10.1063/1.3277044

Mamidala JK, Vishnoi R, Pandey P (2016) The tunnel FET. Tunnel Field-Effect Transistors (TFET). Wiley, Chichester, pp 39–77

Vishnoi R, Kumar MJ (2014) 2-D analytical model for the threshold voltage of a tunneling FET with localized charges. IEEE Trans Electron Devices. https://doi.org/10.1109/TED.2014.2332039

Goswami PP, Khosla R, Bhowmick B (2019) RF analysis and temperature characterization of pocket doped L-shaped gate tunnel FET. Appl Phys A Mater Sci Process 125(10):1–12. https://doi.org/10.1007/s00339-019-3032-8

Singh A, Chaudhury S, Pandey CK, Sharma SM, Sarkar CK (2019) Design and analysis of high k silicon nanotube tunnel FET device. IET Circuits Devices Syst 13(8):1305–1310. https://doi.org/10.1049/iet-cds.2019.0230

Vishnoi R, Kumar MJ (2014) A pseudo-2-D-analytical model of dual material gate all-around nanowire tunneling FET. IEEE Trans Electron Devices 61(7):2264–2270. https://doi.org/10.1109/TED.2014.2321977

Goel A, Rewari S, Verma S, Gupta RS (2019) Temperature-dependent gate-induced drain leakages assessment of dual-metal nanowire field-effect transistor - analytical model. IEEE Trans Electron Devices. https://doi.org/10.1109/TED.2019.2898444

Roy NC, Gupta A, Rai S (2015) Analytical surface potential modeling and simulation of junction-less double gate (JLDG) MOSFET for ultra low-power analog/RF circuits. Microelectron J. https://doi.org/10.1016/j.mejo.2015.07.009

Gupta V, Kumar N, Awasthi H, Rai S, Pandey AK, Gupta A (2021) Temperature-dependent analytical modeling of Graded-Channel Gate-All-Around (GC-GAA) Junctionless Field-Effect Transistors (JLFETs). J Electron Mater. https://doi.org/10.1007/s11664-021-08913-9

Gupta A et al (2021) A novel approach to investigate the impact of hetero-high-K gate stack on SiGe Junctionless Gate-All-Around (JL-GAA) MOSFET. Silicon. https://doi.org/10.1007/s12633-020-00860-0

Chander S et al (2017) Temperature analysis of Ge/Si heterojunction SOI-Tunnel FET. Superlattices Microstruct 110:162–170. https://doi.org/10.1016/j.spmi.2017.08.048

Hu J, Sato Y, Hosono T, Tatsuoka H (2009) Growth condition dependence of structural and electrical properties of Mg2Si layers grown on silicon substrates. Vacuum. https://doi.org/10.1016/j.vacuum.2009.06.055

Kim SH, Agarwal S, Jacobson ZA, Matheu P, Hu C, Liu TJK (2010) Tunnel field effect transistor with raised germanium source. IEEE Electron Device Lett. https://doi.org/10.1109/LED.2010.2061214

Gupta A, Rai MK, Pandey AK et al. (2021) A novel approach to investigate analog and digital circuit applications of silicon junctionless-double-gate (JL-DG) MOSFETs. Silicon. https://doi.org/10.1007/s12633-021-01520-7

Choi WY, Lee W (2010) Hetero-gate-dielectric tunneling field-effect transistors. IEEE Trans Electron Devices. https://doi.org/10.1109/TED.2010.2052167

Wu Y et al (2014) A novel hetero-junction Tunnel-FET using Semiconducting silicide-Silicon contact and its scalability. Microelectron Reliab. https://doi.org/10.1016/j.microrel.2014.01.023

Paras N, Chauhan SS (2019) A novel vertical tunneling based Ge-source TFET with enhanced DC and RF characteristics for prospect low power applications. Microelectron Eng. https://doi.org/10.1016/j.mee.2019.111103

Shih CH, Chien ND (2011) Sub-10-nm tunnel field-effect transistor with graded SI/GE heterojunction. IEEE Electron Device Lett. https://doi.org/10.1109/LED.2011.2164512

Gracia D, Nirmal D, Nisha Justeena A (2017) Investigation of Ge based double gate dual metal tunnel FET novel architecture using various hetero dielectric materials. Superlattices Microstruct 109:154–160. https://doi.org/10.1016/j.spmi.2017.04.045

Silvaco Inc (2016) Atlas User’s Manual. Silvaco Inc., no. 408, p 89 [Online]. Available: https://dynamic.silvaco.com/dynamicweb/jsp/downloads/DownloadManualsAction.do?req=silen-manuals&nm=atlas. Accessed 26 Aug 2016

Chen ZX et al (2009) Demonstration of tunneling FETs based on highly scalable vertical silicon nanowires. IEEE Electron Device Lett. https://doi.org/10.1109/LED.2009.2021079

Mishra V, Verma YK, Gupta SK (2020) Surface potential–based analysis of ferroelectric dual material gate all around (FE-DMGAA) TFETs. Int J Numer Model Electron Netw Devices Fields 33(4):1–11. https://doi.org/10.1002/jnm.2726

Mishra V, Verma YK, Gupta SK, Rathi V (2021) A SiGe-source doping-less double-gate tunnel FET: design and analysis based on charge plasma technique with enhanced performance. Silicon. https://doi.org/10.1007/s12633-021-01030-6

Rewari S, Nath V, Haldar S, Deswal SS, Gupta RS (2019) Hafnium oxide based cylindrical junctionless double surrounding gate (CJLDSG) MOSFET for high speed, high frequency digital and analog applications. Microsyst Technol. https://doi.org/10.1007/s00542-017-3436-3

Acknowledgements

Authors would like to thank Graphic Era (Deemed to be University) for their support and permission to communicate this research paper.

Author information

Authors and Affiliations

Contributions

All the authors have contributed in numerical calculation, framing, and writing the manuscript.

Corresponding author

Ethics declarations

This article does not contain any studies involving animals or human participants performed by any of the authors.

Conflict of Interest

The authors declare that they have no conflicts of interest.

Consent to Participate

Not applicable.

Consent for Publication

Yes.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Anamul Haque, A., Mishra, V., Verma, Y.K. et al. Investigation of Novel Low Bandgap Source Material for Hetero-dielectric GAA-TFET with Enhanced Performance. Silicon 14, 8785–8792 (2022). https://doi.org/10.1007/s12633-021-01571-w

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01571-w