Abstract

In this study, both the Au/(pure-PVA)/n-Si (MPS-1) and Au/(CdTe:PVA)/n-Si (MPS-2) type Schottky diodes (SDs) were fabricated onto the same n-Si wafer in same conditions. After that, their electrical parameters were obtained from the current–voltage (I–V) and capacitance–voltage (C–V) measurements and compared to each other to determine the effect (CdTe:PVA) interlayer on the performance of MPS type SD. The saturation current (Is), ideality factor (n), rectification ratio (RR = Ifor./Irev.), zero-bias barrier height (ΦBo), and series/shunt resistances (Rs, Rsh) were derived utilizing I–V data. The values of Io, n, and ΦBo were found as 9.13 × 10–7 A, 11.07, 0.63 eV for MPS1 and 1.54 × 10–10 A, 3.97, 0.85 eV for MPS2, respectively. The C−2–V graphs were drawn for 0.7 MHz to obtain the doping concentration of donor atoms (ND), Fermi energy (EF), BH/(ΦB(C–V)), depletion layer width (WD), and maximum electric field (Em). The Nss − (Ec − Ess) profile for two SDs was produced from the I–V data by considering the voltage dependence of n and BH. The values of surface states (Nss) were changed between 4.8 × 1013 and 1.7 × 1014 eV−1 cm−2 for MPS1 and 5 × 1012 and 1.15 × 1013 eV−1 cm−2 for MPS2, respectively. All experimental results show that the (CdTe:PVA) interlayer significantly improved the quality of the MS type SDs rather than (pure-PVA) in terms of lower values of leakage/saturation current, n, Nss, and higher RR, BH, and Rsh when compared (pure-PVA) interlayer. The (CdTe:PVA) interlayer may be used instead of the conventional interlayer in the future.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The work function of metals that are used as back and rectifier contacts, and the semiconductor, according to Schottky–Mott theory, determines the ohmic and/or rectifying behavior of metal–semiconductor (MS) and metal-interlayer-semiconductor MIS-type SDs devices [1,2,3,4,5,6,7]. For instance, to make an-ohmic contact onto an n-Si wafer, the work function of metal (Φm) must be lower than that of semiconductor (Φs), but to make a rectifier or Schottky contact, Φm must be higher than Φs. However, with p-type Si or a semiconductor, the situation is completely opposite. Today, the primary scientific/technological challenge in MIS-type SDs is increasing their performance while lowering production costs by employing various acceptable high-dielectric pure or metal/metal-oxide doped polymer layers [1, 2, 7,8,9,10,11,12,13]. A polymer interlayer is typically inexpensive, flexible, and can be easy to grow, with excellent mechanical/dynamic strength. However, it has low conductivity/dielectric values, but they may be improved by doping them with a low fraction of some metal or metal-oxide and graphene [8,9,10,11,12,13]. Apart from this, several studies have been conducted on the electrical properties of nanocomposite structures formed by doping organic or inorganic nanoparticles [14,15,16,17]. These structures can have various effects on their own properties and on the properties of semiconductor devices when used as interlayers in heterostructures [18]. Because both the Nss and Rs are more effective on both the electrical features, they must be considered in the computations. Surface states may arise during the cleaning surface of the semiconductor and fabrication process, which include some unsaturated dangling bonds, oxygen vacancies, atom-like bonds, and dislocations at the junction of interlayer/semiconductor interface in the semiconductor bandgap (Eg) [1,2,3,4,5, 19,20,21,22]. These states/traps can collect or release an increasing number of electrons, acting as recombination centers. Series resistance, on the other hand, can be generated by the semiconductor's back and rectifier contacts, its bulk resistance, and highly and non-uniformly doped donor/acceptor atoms. Shunt resistance is typically caused by leakage-current channels along the interfacial layer, shunt patches from the probe wire to the rectifier contact, and ground [3,4,5].

In our previous study [23], we aimed to produce Au/(CdTe:PVA)/n-Si (MPS) type structures instead of conventional MIS structures, and their electrical parameters were obtained depending on frequency and voltage between 1 and 700 kHz. The voltage-dependent profiles of Nss and their lifetimes (t) were also obtained from the parallel conductance method. Almost all electrical parameters were found to have strong functions of frequency and voltage. More information on the frequency and voltage-dependent basic electric parameters can be found in our previous study [23]. Herein, the influence of the interfacial polymer layer on the electrical properties of Au-PVA-nSi (MPS1) and Au-(CdTe:PVA)-nSi (MPS2) type SDs was investigated in this study. The I–V and C–V measurements were performed in a wide range of voltages to achieve this goal. When compared to pure PVA interlayer, the MPS type SD performs well with low Io or leakage current, n, surface states (Nss), and higher BH, Rsh. The BH value was determined to be 0.85 eV for MS with pure PVA and 0.59 eV for (CdTe:PVA) interlayer, indicating that this second interlayer plays a key role in modifying the BH.

2 Experimental procedures

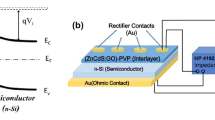

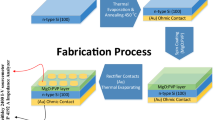

The (Cd(CH3COO)2) and (Na2TeO3) precursors have 99% purity were supplied from Merck-company to prepare CdTe-nanostructures. Firstly, 0.2 M (20-cc) of Na2TeO3 and (Cd(CH3COO)2) and 2 M of NaOH solutions were prepared separately in the deionized water (DW) then combined under-stirring and then it was irradiated by ultrasonic waves at 100 Watt during 15 min. After that, it was cleaned and filtered and finally annealed at about 40 °C for 45 h. Both the MPS1 and MPS2 type SDs were fabricated onto the same n-Si substrate with (100) float zone, 280 μm thickness, and 5 Ω cm resistivity. Secondly, the wafer was cleaned with acetone, methanol, H2O2, NH4OH, and HF solutions in an ultrasonic bath to remove the native SiO2 and dried with N2 gas. Secondly, the high purity (99.999%) metal (Al) was thermally grown onto the whole back side of the wafer at 1 μTorr and sintered at 500 °C for 5 min to obtain good ohmic contact. The (CdTe-PVA) was prepared by dispersing 10 mg of CdTe-nanostructure in 5 ml of (5% PVA) polymer, and then it was performed on the front of n-Si substrate by spin/coating technique. In the last step, Au (99.999%) contact was grown wafer to prepare MPS-1 and MPS-2 at 10–6 Torr. The I–V and C–V measurements were carried out by use of a Keithley 2400 source meter and HP4192-A impedance meter, respectively. The fabricated schematic diagram of the Au/n-Si with pure and (CdTe:PVA) interfacial layer and measurement system is given in Fig. 1.

3 Results and discussion

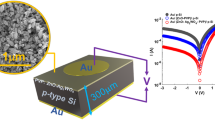

The initial analysis findings were acquired for the produced CdTe powder material using X-ray diffraction (XRD) patterns with two new samples. In Fig. 2a, the XRD representation of CdTe powder is demonstrated. The XRD examination disclosed that the polycrystalline zinc-blende structure aligns with peak positions at 2θ = 23.80°, 39.40°, and 46.50°, corresponding to orientations (111), (220), and (311), respectively (based on JCPDS Data File: 75-2086-cubic). The XRD pattern affirms the creation of pure CdTe semiconductor crystal powder free from any impurities. The XRD model, validating the purity of crystalline CdTe materials, presents distinct and uncontaminated peaks with no shifts. In Fig. 2b, the field emission scanning electron microscopy image provides a detailed visualization of the cadmium telluride (CdTe) nanostructures. The image illustrates the arrangement of the nanostructures in a distinct sheet-like configuration. The observed polydisperse nature of the nanostructures' thickness, which ranges between 50 to 500 nm, underscores the heterogeneous nature of the CdTe nanostructures. The results of the EDX analysis are presented in Fig. 2c, indicating the outcomes obtained from the energy dispersive spectroscopy analysis. The results demonstrate that the composition of CdTe is relatively stoichiometric with a weight percentage and atomic ratio of approximately 1:1. This finding provides valuable insights into the proximity and stoichiometric composition of CdTe, as revealed by the EDX method.

3.1 The current–voltage characteristics

The ln(I)–V curves of the constructed pure-PVA and (CdTe: PVA) interlayers at room temperature are shown in Fig. 3. These charts clearly show a decent linear regime for modest bias voltage, but they start to deviate from linearity due to the presence of Rs and the interfacial-layer. When the voltage is more than 3kT/q, the essential electrical properties of these SDs can be derived from their linear region using TE theory as follows [1, 2, 4,5,6, 24,25,26,27].

The q and k constants are well known in the literature, whereas A, A*, ΦBo, and n is the SD area (= 7.8510–3 cm2), Richardson-constant (which theoretically takes 112 A/(cm K)2 for n-Si), zero bias BH, and ideality factor, respectively. Using the following relationships [1, 4,5,6], we can derive values of Io, n, and ΦBo from the slope and intercept point at zero-bias voltage by evaluating the linear regime of ln(I)–V curves based on Eq. 1 [1, 2].

Table 1 also includes the Io, n, and ΦBo values obtained for two separate samples. As shown in Table 1, the existence of Nss, tunneling via these traps and patches/lower barriers, image force lowering in BH, and generation and recombination (GR) currents can all explain the obtained greater value of n for two SDs.

The voltage-dependent resistance (Ri) profile of the MPS1/MPS2 type SDs was derived from Ohm's-Law and is shown in Fig. 4. As demonstrated in this figure, the value of Ri becomes essentially constant at adequately higher forward voltages and sufficiently lower reverse voltages, corresponds to the true values of Rs (= 4.11 kΩ) and Rsh (= 0.25 MΩ) for MPS1 and 1.17 k and 0.63 MΩ for MPS2 SD, respectively. As can be seen in Table 1, the value of Io for MPS2 SD is 1.69 × 10–4 times lower than for MPS1 SD, and the value of n is similarly 2.79 times lower than for MPS1, indicating that the MPS2 SD performs well. The higher values of Rs can be rooted in the formation of back ohmic and front-rectifier/Schottky contacts, the use of wireless to get electric contact, the bulk resistivity of the semiconductor, and some impurities or dislocations on the surface of the semiconductor. On the other hand, the obtained higher value of n both for MPS1 and MPS2 SD can be explained by the existence of the interfacial layer at Au/n-Si, Nss, and depletion layer width (WD) as seen in Eq. 2. The other reason for the higher values of n can be explained the Gaussian distribution of barrier height at MS interface and generation-recombination current [1, 5, 7]. According to Tung [6], barrier height at the M/S interface may include many patches or lower barriers at around mean BH. In this case, electrons that do not have enough energy to pass through the average barrier can be easily passed through these patches or lower barriers, leading to an increase in the current or n.

The forward bias ln (If)–Vf plots for MPS1 and MPS2 type SDs were made to examine whether the doping concentration of the interlayers impacts the charge-transport mechanisms (CTMs). As shown in Fig. 5, while this plot has one linear part with a slope of 2.43 for the MPS1 SD, it has three linear regimes with different slopes for the MPS2 SD, which are referred to as (region-I for low bias voltages), (region-II for intermediate bias voltages), and (region III for high bias voltages), respectively, due to current variations with applied bias voltage being proportional as I ∝ Vm [2, 22]. The values of these three linear sections for MPS2 SD were found to be 1.01, 10.43, and 4.07, respectively. In the CTM, however, Ohmic behavior dominates for MPS2 type SD. Trap charge limited current (TCLC) dominates both regimes 1 and 2, respectively, in region-1. In general, Ohm's law or behavior tends to be more effective when the slope is closer to unity, SCLC is effective when the slope is almost 2, and TCLC is effective when the slope is greater than 2 [22]. In other words, as the slope (m) value approaches 2, the SD approaches the "trap-filled" limit rather than the ohmic limit, and so many much-electrons may escape from the energy states, contributing to the space–charge limited current (SCLC) [2, 22, 23]. But, when the value of m exceeds two, it shows that CTM is governed by the (TCLC). Based on such a mechanism, increasing the level of injection electrons causes traps/defects to fill and the space charge to rise [22, 23].

The existence of Nss and an interlayer can alter the If–Vf characteristics. According to Card and Rhoderick [5], when the thickness of this layer is greater than 3 nm, the value of n becomes higher than unity for SDs with Nss are equilibrium by semiconductor. The distribution of Nss – (Ec − Ess) in the MS/MIS-type SDs is reckoned with voltage-dependent (n(V)) and effective BH (Φe) using the If–Vf data to determine the influence of different doping levels in interlayers. The following formulas derived by Card and Rhoderick [5, 12, 22] can be utilized to calculate voltage-dependent profiles of the n and BH.

In this equation, εs and εi are the permittivity of the semiconductor and interlayer, respectively, whereas di and WD represent the thickness of the interlayer and depletion layer [1,2,3,4]. On the bottom of the conduction band (Ec) for an n-Si, the energy level of these states (Ess) was derived using the following relationships [1, 3, 5]:

Thus, the Nss vs (Ec − Ess) curves of the MPS1 and MPS2 SDs were determined from the If-Vf data by accounting for both the voltage dependence of n and Φe(V) using Eqs. 2, 4, and 5a, 5b and is shown in Fig. 6. As shown on Fig. 6, the energy dependent-profile of Nss has a ''U'' shape because to peculiar behavior of them in the Si bandgap. Because of the passivation impact of surface states, the Nss values for MPS2 are 10 times lower than for MPS1 [10, 12, 27,28,29,30,31,32,33].

3.2 Capacitance–Voltage (C-V) characteristics

The following relationship [2] describes the relationship between reverse bias voltage (VR) and capacitance per unit area.

The terms Vo and ND in Eq. 6 represent the intercept-voltage of the C−2 vs V curve, respectively. The voltage-dependent C–V curve of the MPS1 and MPS2 type SDs are shown in Fig. 7. Behavior of the curves is similar to the MOS capacitor, has three regimes between − 5 V and 0 V (inversion), 0 V and 1.2 V (depletion), 1.2 V and 5 V (accumulation). As seen in Fig. 8, the C−2 vs V curve displays strong linear behavior in the inversion area over a large voltage range. As a result, basic electronic parameters of MPS1 and MPS2 type SDs, such as diffusion potential (VD), Fermi energy level (EF), maximum electric field (Em) at the junction, WD, and (ΦB(C–V)) were extracted from the intercepts and slopes of the C−2 vs V plots and are tabulated in Table 2. [1, 4, 10, 34,35,36,37,38,39,40,41].

As shown in Table 2, the BH obtained from the reverse bias C−2 vs V curve at 700 kHz for two types of SDs is much higher than the obtained from the ln (If) vs Vf plot because of the nature of the measuring technique and the voltage dependency of these electrical parameters [2, 5,6,7]. Furthermore, as shown in Tables 1 and 2, the value of BH for MPS2 SD is greater than that for MPS1 SD. As a result, all experimental electrical parameters collected are influenced by the applied bias voltage, interfacial layer permittivity and thickness, and series resistance. In summary, it can be said that using a (CdTe:PVA) interfacial layer improves SD performance in terms of lower n, Nss, Io, and greater BH, Rsh, and depletion layer width. As a result, it can be utilized successfully in place of conventional insulators created using established processes.

4 Conclusion

This study examines the influence of the CdTe:PVA polymer layer on the electrical properties of both the Au-PVA-nSi/(MPS1) and Au-(CdTe:PVA)-nSi/(MPS2) interfacial polymer layers built onto the n-Si wafer. To achieve this goal, I–V and C–V measurements were taken over a wide range of voltage. The I–V measurements determined basic electrical parameters such as I0, n, RR, BH, Rs, and Rsh, while the C–V measurement computed ND, BH, Wd, and Em. The I0, n, and ΦB0 values were obtained from the forward bias LnI-V plot as 9.13 × 10–7 A, 11.07, and 0.63 eV for MPS1 and 1.54 × 10–10 A, 3.97, and 0.85 eV for MPS2, respectively. Doping concentration of donor-atoms (ND), Fermi energy (EF), BH/(ΦB(C–V)), depletion layer width (Wd), and maximum electric-field (Em) were calculated from the C−2–V graphs drawn for 0.7 MHz. The Nss − (Ec − Ess) profile for two SDs was produced from the I–V data by considering the voltage dependence of n and BH. The energy levels used for MPS1 and MPS2 were changed to 4.8 × 1013–1.7 × 1014 eV−1 cm−2 and 5 × 1012–1.15 × 1013 eV−1 cm−2, respectively. However, all experiments showed that the use of a (CdTe:PVA) interlayer at the Au/n-Si interface significantly improved the quality of the Au/(pure-PVA)/n-Si SD. When compared to a pure PVA interlayer, the (CdTe:PVA) interlayer structure exhibited lower values of leakage current, ideality factor, and interface states, as well as greater RR, BH, and shunt resistance. The (CdTe:PVA) interfacial polymer layer can be used instead of standard insulators like SiO2 and SnO2 due to its low cost, simple growing and fabrication methods, high dynamic stress, and flexibility properties. The BH value was predicted to be 0.85 eV for MPS1 with pure PVA and 0.59 eV for the interfacial layer (CdTe:PVA). Therefore, the second interfacial layer is crucial in modifying the BH.

Data availability

The datasets generated and/or analyzed during the current study are available from the corresponding author on reasonable request.

References

B.L. Sharma, Metal-semiconductor Schottky Barrier Junctions and Their Applications (Plenum Press, New York, 1984)

S.M. Sze, K.K. Ng, Physics of Semiconductor Devices (Wiley, New York, 2006)

E.H. Nicollian, J.R. Brews, MOS (Metal Oxide Semiconductor) Physics and Technology (Wiley, New York, 1982)

E.H. Rhoderick, R.H. Williams, Metal-Semiconductor Contacts (Clarendon, Oxford, 1988)

H.C. Card, E.H. Rhoderick, Studies of tunnel MOS diodes I. Interface effects in Silicon Schottky diodes. J. Phys. D 4, 1589 (1971)

R.T. Tung, The physics and chemistry of the Schottky barrier height. Appl. Phys. Rev. 13, 011304 (2014). https://doi.org/10.1063/1.4858400

N.A. Al-Ahmadi, Metal oxide semiconductor-based Schottky diodes: a review of recent advances. Mater. Res. Express 7, 032001 (2020)

Ş Altındal, A. Barkhordari, Y. Azizian-Kalandaragh, B.S. Çevrimli, H.R. Mashayekhi, Dielectric properties, and negative-capacitance/dielectric in Au/n-Si structures with PVC and (PVC: Sm2O3) interlayer. Mater. Sci. Semicond. Process. 15, 106754 (2022). https://doi.org/10.1016/j.mssp.2022.106754

M. Al-Dharob, H.E. Lapa, A. Kökce, A.F. Özdemir, D.A. Aldemir, Ş Altındal, The investigation of current-conduction mechanisms (CCMs) in Au/(0.07 Zn-PVA)/n-4H-SiC (MPS) Schottky diodes (SDs) by using (IVT) measurements. Mater. Sci. Semicond. Process. 85, 98–105 (2018)

S.A. Yerişkin, M. Balbaşı, İ Orak, The effects of (graphene doped-PVA) interlayer on the determinative electrical parameters of the Au/n-Si (MS) structures at room temperature. J. Mater. Sci. 28, 14040–14048 (2017). https://doi.org/10.1007/s10854-017-7255-1

O. Çiçek, Ş Altındal, Y. Azizian-Kalandaragh, A highly sensitive temperature sensor based on Au/graphene-PVP/n-Si type Schottky diodes and the possible conduction mechanisms in the wide range temperatures. IEEE Sens. J. 15, 14081 (2020). https://doi.org/10.1109/JSEN.2020.3009108

V.R. Reddy, C.V. Prasad, Surface chemical states, electrical and carrier transport properties of Au/ZrO2/n-GaN MIS junction with a high-k ZrO2 as an insulating layer. Mater. Sci. Eng. B 231, 74–80 (2018). https://doi.org/10.1016/j.mseb.2018.10.006

G. Ersöz, İ Yücedağ, Y. Azizian-Kalandaragh, İ Orak, Ş Altındal, Investigation of electrical characteristics in Al/CdS-PVA/p-Si (MPS) structures using impedance spectroscopy method. IEEE Trans. Electron Devices 63, 2948–2955 (2016). https://doi.org/10.1109/TED.2016.2566813

M.A.A.H. Allah, H.A. Alshamsi, Green synthesis of AC/ZnO nanocomposites for adsorptive removal of organic dyes from aqueous solution. Inorg. Chem. Commun. 157, 111415 (2023)

H.A. Khayoon, M. Ismael, A. Al-Nayili, H.A. Alshamsi, Fabrication of LaFeO3-nitrogen deficient g-C3N4 composite for enhanced the photocatalytic degradation of RhB under sunlight irradiation. Inorg. Chem. Commun. 157, 111356 (2023). https://doi.org/10.1016/j.inoche.2023.111356

A.A. Kadhem, H.A. Alshamsi, Biosynthesis of Ag-ZnO/rGO nanocomposites mediated Ceratophyllum demersum L. leaf extract for photocatalytic degradation of Rhodamine B under visible light. Biomass Convers. Biorefnery (2023). https://doi.org/10.1007/s13399-023-04501-5

Ç.Ş Güçlü, E.E. Tanrıkulu, M. Ulusoy, Y. Azizian-Kalandaragh, Ş Altındal, Frequency-dependent physical parameters, the voltage-dependent profile of surface traps, and their lifetime of Au/(ZnCdS-GO:PVP)/n-Si structures by using the conductance method. J. Mater. Sci. 35, 348 (2024)

B. Akın, M. Ulusoy, S.A. Yerişkin, Investigation of the interface state characteristics of the Al/Al2O3/Ge/p-Si heterostructure over a wide frequency range by capacitance and conductance measurements. Mater. Sci. Semicond. Process. 170, 107951 (2024)

Ö. Güllü, Ş Aydoğan, A. Türüt, Fabrication and electrical characteristics of Schottky diode based on organic material. Microelectron. Eng. 85, 1647–1651 (2008). https://doi.org/10.1016/j.mee.2008.04.003

N. Sghaier, M. Trabelsi, N. Yacoubi, J.M. Bluet, A. Souifi, G. Guillot, C. Gaquière, J.C. DeJaeger, Traps centers and deep defects contribution in current instabilities for AlGaN/GaN HEMT’s on silicon and sapphire substrates. Microelectron. J. 37, 363–370 (2006). https://doi.org/10.1016/j.mejo.2005.05.014

J. Farazin, M.S. Asl, G. Pirgholi-Givi, S.A. Delbari, A.S. Namini, Ş Altındal, Y. Azizian-Kalandaragh, Effect of (Co–TeO2-doped polyvinylpyrrolidone) organic interlayer on the electrophysical characteristics of Al/p-Si (MS) structures. J. Mater. Sci. Mater. Electron. 32, 21909–21922 (2021). https://doi.org/10.1007/s10854-021-06544-8

A. Tataroğlu, Ş Altındal, Y. Azizian-Kalandaragh, Electrical characterization of Au/n-Si (MS) diode with and without graphene-polyvinylpyrrolidone (Gr-PVP) interface layer. J. Mater. Sci. Mater. Electron. 32, 3451–3459 (2021). https://doi.org/10.1007/s10854-020-05091-y

Ç.Ş Güçlü, Ş Altındal, E.E. Tanrıkulu, Voltage and frequency reliant interface traps and their lifetimes of the MPS structures. Physica B 677, 415703 (2024). https://doi.org/10.1016/j.physb.2024.415703

Ç.Ş Güçlü, A.F. Özdemir, A. Kökce, Ş Altındal, Frequency and voltage-dependent dielectric properties and ac electrical conductivity of (Au/Ti)/Al2O3/n-GaAs with thin Al2O3 interfacial layer at room temperature. Acta Phys. Pol. A 129, 325–330 (2016)

Ç. Ş. Güçlü, E. E. Tanrıkulu, A. Dere, Ş. Altındal, Y. Azizian‑Kalandaragh, A comparison of electrical characteristics of the Au/n‑Si Schottky diodes with (ZnCdS:GO(1:1) and (ZnCdS:GO(1:0.5) doped PVP interlayer using current–voltage (I–V) and impedance–voltage (Z–V) measurements. J. Mater. Sci. 34, 1909 (2023). https://doi.org/10.1007/s10854-023-11302-z

Ö. Berkün, M. Ulusoy, Ş Altındal, B. Avar, On frequency and voltage dependent physical characteristics and interface states characterization of the metal semiconductor (MS) structures with (Ti: DLC) interlayer. Physica B 666, 415099 (2023). https://doi.org/10.1016/j.physb.2023.415099

S.K. Cheung, N.W. Cheung, Extraction of Schottky diode parameters from forward current-voltage characteristics. Appl. Phys. Lett. 49, 85–87 (1986). https://doi.org/10.1063/1.97359

M. Sharma, S.K. Tripathi, Analysis of interface states and series resistance for Al/PVA:n-CdS nanocomposite metal–semiconductor and metal–insulator–semiconductor diode structures. Appl. Phys. A 113, 491–499 (2013). https://doi.org/10.1007/s00339-013-7552-3

S. Demirezen, Ş Altındal, Y. Azizian-Kalandaragh, A.M. Akbaş, A comparison of Au/n-Si Schottky diodes (SDs) with/without a nanographite (NG) interfacial layer by considering interlayer, surface states (Nss) and series resistance (Rs) effects. Phys. Scr. 97, 055811 (2022). https://doi.org/10.1088/1402-4896/ac645f

H.G. Çetinkaya, S. Demirezen, S.A. Yerişkin, Electrical parameters of Au/(%1Ni-PVA)/n-Si (MPS) structure: surface states and their lifetimes. Physica B 621, 413207 (2021)

Ş Altındal, Ö. Sevgili, Y. Azizian-Kalandaragh, A comparison of electrical parameters of Au/n-Si and Au/(CoSO4–PVP)/n-Si structures (SBDs) to determine the effect of (CoSO4–PVP) organic interlayer at room temperature. J. Mater. Sci. Mater. Electron. 30, 9273–9280 (2019). https://doi.org/10.1007/s10854-019-01257-5

Y. Badali, Y. Azizian-Kalandaragh, İ Uslu, Ş Altındal, Investigation of the effect of different Bi2O3-x:PVA (x = Sm, Sn, Mo) thin insulator interface-layer materials on diode parameters. J. Mater. Sci. Mater. Electron. 31, 8033–8042 (2020). https://doi.org/10.1007/s10854-020-03343-5

A. Büyükbaş-Uluşan, A. Tataroğlu, S.A. Yerişkin, Analysis of the current transport characteristics (CTCs) in the Au/n-Si Schottky diodes (SDs) with Al2O3 interfacial layer over wide temperature range. ECS J. Solid State Sci. Technol. 12, 083010 (2023)

N. Delen, S.A. Yerişkin, A. Özbay, İ Taşçıoğlu, Origin of frequency and voltage dependent negative dielectric properties in the Al/p-Si Schottky diodes with (Cd0.3Zn0.7O) interfacial layer in the wide range of frequency and voltage. Physica B 665, 415031 (2023). https://doi.org/10.1016/j.physb.2023.415031

G.H. Thomas, A.A. Kumar, V.R. Reddy, V. Janardhanam, C.J. Choi, On the current conduction mechanisms of WO3/n-Ge Schottky interfaces. Mater. Today (2023). https://doi.org/10.1016/j.matpr.2023.01.363

H. Elamen, Y. Badali, M. Ulusoy, Y. Azizian-Kalandaragh, Ş Altındal, M.T. Güneşer, The photoresponse behavior of a Schottky structure with a transition metal oxide-doped organic polymer (RuO2:PVC) interface. Polym. Bull. 81, 403–422 (2023). https://doi.org/10.1007/s00289-023-04725-5

H.U. Tecimer, M.A. Alper, H. Tecimer, S.O. Tan, Ş Altındal, Integration of Zn-doped organic polymer nanocomposites between metal semiconductor structure to reveal the electrical qualifications of the diodes. Polym. Bull. 75, 4257–4271 (2018)

M. Ulusoy, Y. Badali, G. Pirgholi-Givi, Y. Azizian-Kalandaragh, Ş Altındal, The capacitance/conductance and surface state intensity characteristics of the Schottky structures with ruthenium dioxide-doped organic polymer interface. Synth. Metals 292, 117243 (2023)

S. Demirezen, A.A. Alsaç, H.G. Çetinkaya, Ş Altındal, The investigation of current-transport mechanisms (CTMs) in the Al/(In2S3:PVA)/p-Si (MPS)-type Schottky barrier diodes (SBDs) at low and intermediate temperatures. J. Mater. Sci. Electron. 34, 1186 (2023)

S. Demirezen, A. Kaya, Ş Altındal, İ Uslu, The energy density distribution profile of interface traps and their relaxation times and capture cross sections of Au/GO-doped PrBaCoO nanoceramic/n-Si capacitors at room temperature. Polym. Bull. 74, 3765–3781 (2017). https://doi.org/10.1007/s00289-017-1925-2

H.E. Lapa, Ç.Ş Güçlü, D.A. Aldemir, A.F. Özdemir, The evaluation of the current–voltage and capacitance–voltage-frequency measurements of Yb/p-Si Schottky diodes with a high zero-bias barrier height. Appl. Phys. A 126, 1–9 (2020). https://doi.org/10.1007/s00339-020-03662-8

Acknowledgements

This present study was supported by the Scientific-Technological Research Council of (TUBITAK) with 121C396 Project-Number.

Funding

Open access funding provided by the Scientific and Technological Research Council of Türkiye (TÜBİTAK). Funding was provided by Türkiye Bilimsel ve Teknolojik Araştırma Kurumu (121C396).

Author information

Authors and Affiliations

Contributions

All authors contributed approximately the same to the preparation of the samples and them interpretation, reviewing, writing. ÇŞG: Manufacturing, investigation, measurements, calculations, writing, reviewing and editing. MU: Investigation, measurements, calculations, reviewing and editing. ŞA: Review, editing and supervising.

Corresponding author

Ethics declarations

Conflict of interest

There are no conflicts to declare.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Güçlü, Ç.Ş., Ulusoy, M. & Altındal, Ş. A comparison electrical characteristics of the Au/(pure-PVA)/n-Si and Au/(CdTe doped-PVA)/n-Si (MPS) type Schottky structures using I–V and C–V measurements. J Mater Sci: Mater Electron 35, 881 (2024). https://doi.org/10.1007/s10854-024-12650-0

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s10854-024-12650-0