Abstract

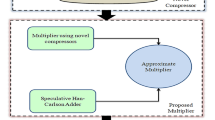

In this research paper, approximate multipliers are designed to reduce the computational time and power delay product. However, there is a high possibility to further optimize the area and power using the modified Wallace Tree Multiplier (MWTM). This research paper proposes, two modified approximate 4:2 compressors are used for partial product addition in multipliers. Using the proposed MWTM, it is observed that Normalized Error Distance (NMED), Mean Relative Error Distance (MRED) and Power Delay Product (PDP) are reduced. The proposed architectures are synthesized using 90-nm CMOS standard cells. Modified Wallace tree multipliers of various sizes (8, 16 and 32 bit) are designed and their performance is compared with the existing general multipliers. The synthesis results of 8-bit MWTM shows that on an average the delay and power are reduced in the range of 10%–55.37% and 13.03%–13.78% when compared to existing multipliers. Moreover, for 16-bit MWTM shows that on an average the delay and power are reduced in the range of 0.11%–3.12% and 0.28%–6.59%. And 32-bit MWTM shows that on an average the power is reduced in the range of about 8%–27.99%. The image processing operations image blending, image smoothening and edge detection are implemented using the proposed MWTM. The results proved the efficiency of the MWTM.

Similar content being viewed by others

Data Availability

Data sharing not applicable to this article as no datasets were generated or analysed during the current study.

References

Abid Z, El-Razouk H, El-Dib DA (2008) Low power multipliers based on new hybrid full adders. Microelectron J 39(12):1509–1515. https://doi.org/10.1016/j.mejo.2008.04.002 (ISSN 0026–2692)

Akbari O, Kamal M, Afzali-Kusha A, Pedram M (2016) RAP-CLA: A reconfigurable approximate carry look-ahead adder. IEEE Trans Circuits Syst II Express Briefs 65(8):1089–1093. https://doi.org/10.1109/TCSII.2016.2633307

Akbari O, Kamal M, Afzali-Kusha A, Pedram M, Shafique M (2018) PX-CGRA: Polymorphic approximate coarse-grained reconfigurable architecture. In: Proc. Design, Automation & Test in Europe Conference & Exhibition (DATE), pp 413–418. https://doi.org/10.23919/DATE.2018.8342045

Ansari MS, Jiang H, Cockburn BF, Han J (2018) Low-Power Approximate Multipliers Using Encoded Partial Products and Approximate Compressors. IEEE J Emerg Sel Top Circuits Syst 8(3):404–416. https://doi.org/10.1109/JETCAS.2018.2832204

Ansari MS, Mrazek V, Cockburn BF, Sekanina L, Vasicek Z, Han J (2020) Improving the Accuracy and Hardware Efficiency of Neural Networks Using Approximate Multipliers. IEEE Trans Very Large Scale Integr Syst 28(2):317–328. https://doi.org/10.1109/TVLSI.2019.2940943

Bahadori M, Kamal M, Afzali-Kusha A, Pedram M (2016) High-Speed and Energy-Efficient Carry Skip Adder Operating Under a Wide Range of Supply Voltage Levels. IEEE Trans Very Large Scale Integr Syst 24(2):421–433. https://doi.org/10.1109/TVLSI.2015.2405133

Behrooz P (2010) Computer Arithmetic: Algorithms and Hardware Designs, 2nd edn. Oxford University Press, New York

Bickerstaff KC, Schulte MJ, Swartzlander EE (1995) Parallel reduced area multipliers. J VLSI Sig Proc 9:181–191. https://doi.org/10.1007/BF02407084

Brandalero M, Beck ACS, Carro L, Shafique M (2018) Approximate On-The-Fly Coarse-Grained Reconfigurable Acceleration for General-Purpose Applications. In: Proc. 55th ACM/IEEE Design Automation Conference (DAC), pp 1–6. https://doi.org/10.1109/DAC.2018.8465930

Chen T, Du Z, Sun N, Wang J, Wu C, Chen Y, Temam O (2014) Diannao: “A small-footprint high-throughput accelerator for ubiquitous machine-learning.” ACM Sigplan Notices 49:269–284. https://doi.org/10.1145/2541940.2541967

Dadda L (1983) Some schemes for fast serial input multipliers. In: Proc. IEEE 6th Symposium on Computer Arithmetic (ARITH), pp 52–59. https://doi.org/10.1109/ARITH.1983.6158074

Garg B, Patel SK, Dutt S (2020) LoBA: A Leading One Bit Based Imprecise Multiplier for Efficient Image Processing. J Electron Test 36:429–437. https://doi.org/10.1007/s10836-020-05883-4

Garg B, Sharma GK (2017) ACM: An Energy-Efficient Accuracy Configurable Multiplier for Error-Resilient Applications. J Electron Test 33:479–489. https://doi.org/10.1007/s10836-017-5667-8

Gorantla A, Deepa P (2019) Design of approximate subtractors and dividers for error tolerant image processing applications. J Electron Test 35(6):901–907. https://doi.org/10.1007/s10836-019-05837-5

Hashemi S, Bahar RI, Reda S (2015) DRUM: A Dynamic Range Unbiased Multiplier for approximate applications. In: Proc. IEEE/ACM Int Conf Comput Aided Des., pp 418–425. https://doi.org/10.1109/ICCAD.2015.7372600

Kulkarni P, Gupta P, Ercegovac M (2011) Trading Accuracy for Power with an Underdesigned Multiplier Architecture. In: Proc. 24th Internatioal Conference on VLSI Design, pp 346–351. https://doi.org/10.1109/VLSID.2011.51

Kyaw KY, Goh WL, Yeo KS (2010) Low-power high-speed multiplier for error-tolerant application. In: Proc. IEEE Int Conf Electron Devices Solid-State Circuits (EDSSC), pp 1–4. https://doi.org/10.1109/EDSSC.2010.5713751

Jiang H, Liu C, Maheshwari N, Lombardi F, Han J (2016) A comparative evaluation of approximate multipliers. In: Proc. IEEE/ACM International Symposium on Nanoscale Architectures (NANOARCH), pp 191–196. https://doi.org/10.1145/2950067.2950068

Jiang H, Santiago FJH, Mo H, Liu L, Han J (2020) Approximate Arithmetic Circuits: A Survey, Characterization, and Recent Applications. Proc IEEE 108(12):2108–2135. https://doi.org/10.1109/JPROC.2020.3006451

Jothin R, Vasanthanayaki C (2018) High Performance Modified Static Segment Approximate Multiplier based on Significance Probability. J Electron Test 34:607–614. https://doi.org/10.1007/s10836-018-5748-3

Kulkarni P, Gupta P, Ercegovac M (2011) Trading Accuracy for Power with an Underdesigned Multiplier Architecture. In: Proc. 24th Internatioal Conference on VLSI Design, pp 346–351. https://doi.org/10.1109/VLSID.2011.51

Kuo K-C, Chou C-W (2010) Low power and high-speed multiplier design with row bypassing and parallel architecture. Microelectron J 41:639–650. https://doi.org/10.1016/j.mejo.2010.06.009

Lau M, Ling K, Chu Y-C (2009) Energy-aware probabilistic multiplier: Design and analysis. In: Proc. International Conference on Compilers, Architecture, and Synthesis for Embedded Systems (CASES '09). Association for Computing Machinery, New York, NY, USA, pp 281–290. https://doi.org/10.1145/1629395.1629434

Liu C, Han J, Lombardi F (2014) A low-power, high-performance approximate multiplier with configurable partial error recovery. In: Proc. Design Automation & Test in Europe Conference & Exhibition (DATE), pp 1–4. https://doi.org/10.7873/DATE.2014.108

Lin C, Lin I (2013) High accuracy approximate multiplier with error correction. In: Proc. IEEE 31st International Conference on Computer Design (ICCD), pp 33–38. https://doi.org/10.1109/ICCD.2013.6657022

Liu W, Lombardi F, Schulte M (2020) Approximate Computing: From Circuits to Applications. Proc IEEE 108(12):2103–2107. https://doi.org/10.1109/JPROC.2020.3033361

Mittal S (2016) A Survey of Techniques for Approximate Computing. ACM Comp Surv 48(4):62. https://doi.org/10.1145/2893356

Momeni A, Han J, Montuschi P, Lombardi F (2015) Design and Analysis of Approximate Compressors for Multiplication. IEEE Trans Comput 64(4):984–994. https://doi.org/10.1109/TC.2014.2308214

Moore GE (2006) "Cramming more components onto integrated circuits, Reprinted from Electronics, volume 38, number 8, April 19, 1965, pp.114 ff.," in IEEE Solid-State Circuits Society Newsletter, vol. 11, no. 3, pp. 33-35. https://doi.org/10.1109/N-SSC.2006.4785860

Narayanamoorthy S, Moghaddam HA, Liu Z, Park T, Kim NS (2015) Energy-efficient approximate multiplication for digital signal processing and classification applications. IEEE Trans Very Large Scale Integr Syst 23(6):1180–1184. https://doi.org/10.1109/TVLSI.2014.2333366

Raha A, Jayakumar H, Raghunathan V (2016) Input-Based Dynamic Reconfiguration of Approximate Arithmetic Units for Video Encoding. IEEE Trans Very Large Scale Integr Syst 24(3):846–857. https://doi.org/10.1109/TVLSI.2015.2424212

Rodrigues G, Lima Kastensmidt F, Bosio A (2020) Survey on Approximate Computing and Its Intrinsic Fault Tolerance. Electronics 9(4):557. https://doi.org/10.3390/electronics9040557

Shafique M, Garg S, Henkel J, Marculescu D (2014) The EDA challenges in the dark silicon era. In: Proc. 51st ACM/IEEE Design Automation Conference (DAC), pp 1–6. https://doi.org/10.1145/2593069.2593229

Shin D, Gupta SK (2010) Approximate logic synthesis for error tolerant applications. In: Proc. Design, Automation & Test in Europe Conference & Exhibition (DATE 2010), pp 957–960. https://doi.org/10.1109/DATE.2010.5456913

Strollo AGM, Napoli E, De Caro D, Petra N, Meo GD (2020) Comparison and Extension of Approximate 4–2 Compressors for Low-Power Approximate Multipliers. IEEE Trans Circuits Syst I Regul Pap 67(9):3021–3034. https://doi.org/10.1109/TCSI.2020.2988353

Venkatachalam S, Ko S (2017) Design of Power and Area Efficient Approximate Multipliers. IEEE Trans Very Large Scale Integr Syst 25(5):1782–1786. https://doi.org/10.1109/TVLSI.2016.2643639

Venkataramani S, Sabne A, Kozhikkottu V, Roy K, Raghunathan A (2012) SALSA: Systematic logic synthesis of approximate circuits. In: Proc. Design Automation Conference (DAC), pp 796–801. https://doi.org/10.1145/2228360.2228504

Wallace CS (1964) A Suggestion for a Fast Multiplier. IEEE Trans Electron Comput 13(1):14–17. https://doi.org/10.1109/PGEC.1964.263830

Zendegani R, Kamal M, Bahadori M, Afzali-Kusha A, Pedram M (2017) RoBA Multiplier: A Rounding-Based Approximate Multiplier for High-Speed yet Energy-Efficient Digital Signal Processing. IEEE Trans Very Large Scale Integr Syst 25(2):393–401. https://doi.org/10.1109/TVLSI.2016.2587696

Zhang Q, Wang T, Tian Y, Yuan F, Xu Q (2015) Approx ANN: An approximate computing framework for artificial neural network. In: Proc. Design Automation & Test in Europe Conference & Exhibition (DATE), pp 701–706

Funding

No funding was received to assist with the preparation of this manuscript.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of Interest

The authors have no conflicts of interest to declare that are relevant to the content of this article.

Competing Interests

The authors have no competing interests to declare that are relevant to the content of this article.

Additional information

Responsible Editor: S. T. Chakradhar

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Chandaka, S., Narayanam, B. Hardware Efficient Approximate Multiplier Architecture for Image Processing Applications. J Electron Test 38, 217–230 (2022). https://doi.org/10.1007/s10836-022-06000-3

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-022-06000-3