Abstract

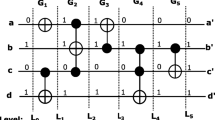

Testability dramatically enhances the operating cost in reversible logic circuits as it increases the cost metrics such as gate count, quantum cost, number of wires and garbage output. This increase also affects the utilization of resources, which further enhances overall cost of testing. This paper presents a new design for testability methodology for reversible circuits by exploring the properties of multiple controlled Toffoli and Fredkin gates, to produce online testable circuits at lower cost metrics. The method includes simplification and modification of Toffoli circuits to form parity-preserving Toffoli–Fredkin cascades. The testability in these cascades can be achieved by comparing the parity of inputs and outputs using controlled-NOT gates on an additional wire. Single-point failures in reversible logic circuits are targeted by means of detecting bit faults. In contrast to the existing work, the present model is robust, low cost and has lesser design complexity. Experiments are conducted on a set of benchmark circuits to prove the efficacy of the present work. The results show an average reduction by 15.9 % in gate cost and 11.0 % in total operating cost when compared to the most recent existing work formulated on the same platform.

Similar content being viewed by others

References

Polian, I., Fiehn, T., Becker, B., Hayes, J.P.: A family of logical fault models for reversible circuits. In: 14th Asian Test Symposium (ATS05), pp. 422–427 (2005)

Chuang, I.L., et al.: Experimental realization of Shors quantum factoring algorithm using nuclear magnetic resonance. Nature 414, 883–887 (2001)

Gaur, H.M., Singh, A.K., Ghanekar, U.: A new DFT methodology for k-CNOT reversible circuits and its implementation using quantum-dot cellular automata. Int. J. Light Electron Opt. 127(22), 10593–10601 (2016)

Takeuchi, N., Yamanashi, Y., Yoshikawa, N.: Reversible logic gate using adiabatic superconducting devices. Nature 4, (2014) Article no. 6354

Bennett, C.H.: Logical reversibility of computation. IBM J. Res. Dev. 17(66), 525–532 (1974)

Vandersypen, L.M.K., Steffen, M., Breyta, G., Yannoni, C.S., Sherwood, M.H., Chuang, I.L.: Experimental realization of Shors quantum factoring algorithm using nuclear magnetic resonance. Nature 414, 883–887 (2001)

Nielsen, M., Chuang, I.L.: Quantum Computation and Quantum Information. Cambridge University Press, Cambridge (2000)

Gaur, H.M., Singh, A.K., Ghanekar, U.: A review on online testability for reversible logic. Procedia Comput. Sci. 70, 384–391 (2015)

Vasudevan, D.P., Lala, P.K., Jia, D., Parkerson, J.P.: Reversible logic design with online testability. IEEE Trans. Instrum. Meas. 55(2), 406–414 (2006)

Thapliyal, H., Vinod, A.P.: Designing efficient online testable reversible adders with new reversible gate. In: IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1085–1088

Thapliyal, H., Ranganathan, N.: Reversible logic based concurrent error detection methodology for emerging nanocircuit. In: 10th IEEE International Conference on Nano Technology, pp. 217–222 (2004)

Farazmand, N., Zamani, M., Tahoori, M.B.: Online fault testing of reversible logic using dual rail coding. In: 16th IEEE International Symposium on On-Line Testing (IOLTS), pp. 204–205 (2010)

Mahammad, S.K.N., Veezhinathan, K.: Constructing online testable circuits using reversible logic. IEEE Trans Instrum. Meas. 59(1), 101–109 (2010)

Gaur, H.M., Singh, A.K.: Design of reversible logic circuits with high testability. IET Electron. Lett. 52(13), 1102–1104 (2016)

Nayeem, N.M., Rice, J.E.: Online testable approaches in reversible logic. J. Electron Test. 29(6), 763–778 (2013)

Sen, B., Das, J., Sikdar, B.K.: A DFT methodology targeting online testing of reversible circuit. In: IEEE International Conference of Devices, Circuits and Systems, pp. 689–693 (2012)

Mohammadi, M., Eshghi, M.: On figures of merit in reversible logic designs. J. Quant. Info Process. 8(4), 297–318 (2009)

Maslov, D., Dueck, G., Scott, N.: Reversible Logic Synthesis Benchmark, http://www.cs.uvic.ca/~dmaslov (2017)

An Online Resource for Reversible Functions and Reversible Circuits. http://www.informatik.uni-bremen.de/revkit/

Miller, D.M., Maslov, D., Dueck, G.W.: A transformation based algorithm for reversible logic synthesis. In: Proceedings of DAC, pp. 318–323 (2010)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Gaur, H.M., Singh, A.K. & Ghanekar, U. Simplification and modification of multiple controlled Toffoli circuits for testability. J Comput Electron 18, 356–363 (2019). https://doi.org/10.1007/s10825-019-01303-9

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-019-01303-9