Abstract

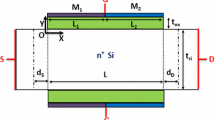

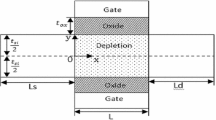

Junctionless transistors, which do not have any pn junction in the source-channel-drain path have become an attractive candidate in sub-20 nm regime. They have homogeneous and uniform doping in source-channel-drain region. Despite some similarities with conventional MOSFETs, the charge-potential relationship is quite different in a junctionless transistor, due to its different operational principle. In this report, models for potential and drain current are formulated for shorter channel symmetric double-gate junctionless transistor (DGJLT). The potential model is derived from two dimensional Poisson’s equation using “variable separation technique”. The developed model captures the physics in all regions of device operation i.e., depletion to accumulation region without any fitting parameter. The model is valid for a range of channel doping concentrations, channel thickness and channel length. Threshold voltage and drain-induced barrier lowering values are extracted from the potential model. The model is in good agreement with professional TCAD simulation results.

Similar content being viewed by others

References

Colinge, J.-P., Lee, C.-W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., Razavi, P., O’Neill, B., Blake, A., White, M., Kelleher, A.-M., McCarthy, B., Murphy, R.: Nanowire transistors without junctions. Nat. Nanotechnol. 5, 225–229 (2010)

Gnani, E., Gnudi, A., Reggiani, S., Baccarani, G.: Theory of the junctionless nanowire FET. IEEE Trans. Electron Devices 58, 2903–2910 (2011)

Duarte, J.P., Choi, S.-J., Choi, Y.-K.: A full-range drain current model for double-gate junctionless transistors. IEEE Trans. Electron Devices 58, 4219–4225 (2011)

Chen, Z., Xiao, Y., Tang, M., Xiong, Y., Huang, J., Li, J., Gu, X., Zhou, Y.: Surface-potential-based drain current model for long-channel junctionless double-gate MOSFETs. IEEE Trans. Electron Devices 59, 3292–3298 (2012)

Sallese, J.-M., Chevillon, N., Lallement, C., Iñiguez, B., Prégaldiny, F.: Charge-based modeling of junctionless double-gate field-effect transistors. IEEE Trans. Electron Devices 58, 2628–2637 (2011)

Lime, F., Santana, E., Iñiguez, B.: A simple compact model for long-channel junctionless double gate MOSFETs. Solid State Electron. 80, 28–30 (2013)

Duarte, J.P., Choi, S.-J., Choi, Y.-K.: A full-range drain current model for double-gate junctionless transistors. IEEE Trans. Electron Devices 58, 4219–4225 (2011)

Duarte, J.P., Choi, S.J., Moon, D.I., Choi, Y.K.: Simple analytical bulk current model for long-channel double-gate junctionless transistors. IEEE Trans. Electron Devices 32, 704–706 (2011)

Duarte, J.P., Kim, M.-S., Choi, S.-J., Choi, Y.-K.: A compact model of quantum electron density at the subthreshold region for double-gate junctionless transistors. IEEE Trans. Electron Devices 59, 1008–1012 (2012)

Duarte, J.P., Choi, S.-J., Moon, D.-I., Choi, Y.-K.: A nonpiecewise model for long-channel junctionless cylindrical nanowire FETs. IEEE Electron Device Lett. 33, 155–157 (2012)

Chiang, T.-K.: A quasi-two-dimensional threshold voltage model for short-channel junctionless double-gate MOSFETs. IEEE Trans. Electron Devices 59, 2284–2289 (2012)

Gnudi, A., Reggiani, S., Gnani, E., Baccarani, G.: Semianalytical model of the subthreshold current in short-channel junctionless symmetric double-gate field-effect transistors. IEEE Trans. Electron Devices 60, 1342–1348 (2013)

Trevisoli, R.D., Doria, R.T., Souza, M., Pavanello, M.A.: A physically-based threshold voltage definition, extraction and analytical model for junctionless nanowire transistors. Solid-State Electron. 90, 12–17 (2013)

Trevisoli, R.D., Doria, R.T., Pavanelloc, M.A.: Analytical model for the threshold voltage in junctionless nanowire transistors of different geometries. ECS Trans. 39, 147–154 (2011)

Trevisoli, R.D., Doria, R.T., de Souza, M., Pavanello, M.A.: Accounting for short channel effects in the drain current modeling of junctionless nanowire transistors. ECS Trans. 49, 207–214 (2012)

Gnudi, A., Reggiani, S., Gnani, E., Baccarani, G.: Analytical model for the threshold voltage variability due to random dopant fluctuations in junctionless FETs, pp. 5–7. SISPAD, Denver (2012)

Cerdeira, A., Estrada, M., Iniguez, B., Trevisoli, R.D., Doria, R.T., Souza, M., de, M., Pavanello, A.: Charge-based continuous model for long-channel symmetric double-gate junctionless transistors. Solid-State Electron 85, 59–63 (2013)

Cerdeira, A., Estrada, M., Trevisoli, R.D., Doria, R.T., de Souza, M., Pavanello, M.A.: Analytical model for potential in double-gate juntionless transistors. Symposium on Microelectronics Technology and Devices (2013)

Jin, X., Liu, X., Wu, M., Chuai, R., Lee, J.-H., Lee, J.-H.: Modelling of the nanoscale channel length effect on the subthreshold characteristcs of junctionless field-effect transistors with a symmetric double-gate structure. J. Phys. D 45, 375102–375107 (2012)

Yesayan, A., Prégaldiny, F., Sallese, J.-M.: Explicit drain current model of junctionless double-gate field-effect transistors. Solid-State Electron. 89, 134–138 (2013)

Hu, G., Xiang, P., Ding, Z., Liu, R., Wang, L., Tang, T.-A.: Analytical models for electric potential, threshold voltage, and subthreshold swing of junctionless surrounding-gate transistors. IEEE Trans. Electron Devices 61, 688–695 (2014)

Woo, J.-H., Choi, J.-M., Choi, Y.-K.: Analytical threshold voltage model of junctionless double-gate MOSFETs with localized charges. IEEE Trans. Electron Devices 60, 2951–2955 (2013)

Li, C., Zhuang, Y., Di, S., Han, R.: Subthreshold behavior models for nanoscale short-channel junctionless cylindrical surrounding-gate MOSFETs. IEEE Trans. Electron Devices 60, 3655–3662 (2013)

Trevisoli, R.D., Doria, R.T., Souza, M., Das, S., Ferain, I., Pavanello, M.A.: Surface-potential-based drain current analytical model for triple-gate junctionless nanowire transistors. IEEE Trans. Electron Devices 59, 3510–3518 (2012)

Jiang, C., Liang, R., Wang, J., Xu, J.: A two-dimensional analytical model for short channel junctionless double-gate MOSFETs. AIP Adv. 5, 057122 (2015)

Xi, L., Kwon, H., Lee, J., Lee, J.: A subthreshold current model for nanoscale short channel junctionless MOSFETs applicable to symmetric and asymmetric double-gate structure. Solid-State Electron. 82, 77–81 (2013)

Holtij, T., Schwarz, M., Kloes, A., Iñíguez, B.: Threshold voltage, and 2D potential modeling within short-channel junctionless DG MOSFETs in subthreshold region. Solid-State Electron. 90, 107–115 (2013)

Hamid, H.A.E., Guitart, J.R., Iniguez, B.: Two-dimensional analytical threshold voltage and subthreshold swing models of undoped symmetric double-gate MOSFETs. IEEE Trans. Electron Devices 54, 1402–1408 (2007)

Liang, X., Taur, Y.: 2-D analytical solution for SCEs in DG MOSFETs. IEEE Trans. Electron Devices 51, 1385–1391 (2004)

Holtij, T., Schwarz, M., Kloes A., Iniguez, B.: 2D analytical potential modeling of junctionless DG MOSFETs in subthreshold region including proposal for calculating the threshold voltage. 13th International Conference on Ultimate Integration on Silicon (ULIS), pp. 81– 84 (2012)

Atlas User’s Manual: Device Simulation Software (2008)

Acknowledgments

This work was partially supported by DST SERB, Government of India, under Grant No. SB/FTP/ETA-268/2012.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Baruah, R.K., Paily, R.P. A surface-potential based drain current model for short-channel symmetric double-gate junctionless transistor. J Comput Electron 15, 45–52 (2016). https://doi.org/10.1007/s10825-015-0723-z

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-015-0723-z