Abstract

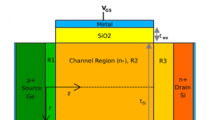

In this paper, we have developed a pseudo two-dimensional (2-D) analytical model for the surface potential of a dual-material double-gate junctionless field-effect transistor. We have incorporated the effects of depletion into the source and drain regions to model the surface potential for all three operating modes: (a) full depletion, (b) partial depletion, and (c) near flatband. The effects of the device parameters such as oxide thickness, silicon thickness, and impurity concentration on the surface potential is demonstrated through the model. The model is further extended to derive an expression for the threshold voltage which predicts the expected change with respect to variation in the device parameters. The accuracy of the proposed model is verified against 2-D numerical simulations.

Similar content being viewed by others

References

Chen, Z., Xiao, Y., Tang, M., Xiong, Y., Huang, J., Li, J., Gu, X., Zhou, Y.: Surface-potential-based drain current model for long-channel junctionless double gate MOSFETs. IEEE Trans. Electron Devices 59(12), 3292–3298 (2012)

Long, W., Ou, H., Kuo, J.M., Chin, K.K.: Dual material gate (DMG) field effect transistor. IEEE Trans. Electron Devices 46, 865–870 (1999)

Kumar, M.J., Chaudhary, A.: Two-dimensional analytical modeling of fully depleted DMG SOI MOSFET and evidence for diminished SCEs. IEEE Trans. Electron Devices 51(4), 569–574 (2004)

Kumar, M.J., Chaudhary, A.: Investigation of the novel attributes of a fully depleted dual-material gate SOI MOSFET. IEEE Trans. Electron Devices 51(9), 1463–1467 (2004)

Saxena, R.S., Kumar, M.J.: Dual material gate technique for enhanced transconductance and breakdown voltage of trench power MOSFETs. IEEE Trans. Electron Devices 56(3), 517–522 (2009)

Vishnoi, R., Kumar, M.J.: Compact analytical model of dual material gate tunneling field-effect transistor using interband tunneling and channel transport. IEEE Trans. Electron Devices 61(6), 1936–1942 (2014)

Vishnoi, R., Kumar, M.J.: A pseudo-2-D-analytical model of dual material gate all-around nanowire tunneling FET. IEEE Trans. Electron Devices 61(7), 2264–2270 (2014)

Saurabh, S., Kumar, M.J.: Investigation of the novel attributes of a dual material gate nanoscale tunnel field effect transistor. IEEE Trans. Electron Devices 58(2), 404–410 (2011)

Kumar, M.J., Reddy, G.V.: Evidence for suppressed short-channel effects in deep submicron dual-material gate (DMG) partially depleted SOI MOSFETs - A two-dimensional analytical approach. Microelectron. Engg. 75(4), 367–374 (2004)

Pandey, P., Vishnoi, R., Kumar, M.J.: A full-range dual material gate tunnel field effect transistor drain current model considering both source and drain depletion region band-to-band tunneling. J. Comput. Electron. 14(1), 280–287 (2015)

Beneventi, G.B., Gnani, E., Gnudi, A., Reggiani, S., Baccarani, G.: Dual-metal-gate InAs tunnel FET with enhanced turn-on steepness and high on-current. IEEE Trans. Electron Devices 61(3), 776–784 (2014)

Lou, H., Zhang, L., Zhu, Y., Lin, X., Yang, S., He, J.: A junctionless nanowire transistor with a dual-material gate. IEEE Trans. Electron Devices 59(7), 1829–1836 (2012)

Baruah, R.K., Paily, R.P.: A dual-material gate junctionless transistor with high- \(k\) spacer for enhanced analog performance. IEEE Trans. Electron Devices 61(1), 123–128 (2014)

Ren, C., Yu, H., Kang, J., Wang, X., Ma, H., Yeo, Y., Chan, D., Li, M., Kwong, D.: A dual-metal gate integration process for CMOS with sub- 1-nm EOT HfO2 by using HfN replacement gate. IEEE Electron Device Lett. 25(8), 580–582 (2004)

Yeo, Y., Lu, Q., Ranade, P., Takeuchi, H., Yang, K., Polishchuk, I., King, T., Hu, C., Song, S., Luan, H., Kwong, D.-L.: Dual-metal gate CMOS technology with ultrathin silicon nitride gate dielectric. IEEE Electron Device Lett. 22(5), 227–229 (2001)

ATLAS Device Simulation Software, Silvaco Int., Santa Clara, CA (2014)

Gnudi, A., Reggiani, S., Gnani, E., Baccarani, G.: Semi-analytical model of the subthreshold current in short-channel junctionless symmetric double-gate field-effect transistors. IEEE Trans. Electron Devices 60(4), 1342–1348 (2013)

Duarte, J.P., Choi, S.-J., Choi, Y.-K.: A full-range drain current model for double-gate junctionless transistors. IEEE Trans. Electron Devices 58(12), 4219–4225 (2011)

Young, K.K.: Analysis of conduction in fully depleted SOI MOSFETs. IEEE Trans. Electron Devices 36(3), 504–506 (1989)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Agrawal, A.K., Koutilya, P.N.V.R. & Jagadesh Kumar, M. A pseudo 2-D surface potential model of a dual material double gate junctionless field effect transistor. J Comput Electron 14, 686–693 (2015). https://doi.org/10.1007/s10825-015-0710-4

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-015-0710-4