Abstract

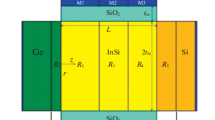

A novel 2-D analytical potential model of source and drain region along with channel for a fully depleted symmetric double gate junction less transistor is presented in this paper. The boundary conditions for channel potential along the channel length is taken considering source and drain region and boundary conditions for source and drain potential model are derived from channel longitudinal potential expression. The potential model is validated using TCAD simulations. A method for scale length determination is also presented. Scale length expression is obtained from the transverse electrostatic potential expression. Scale length variation with silicon layer thickness and gate oxide thickness is shown. The dependence of Scale length on the dielectric constant is also shown for the three dielectrics—“\(\hbox {SiO}_2 \)”, “\(\hbox {Al}_2 \hbox {O}_3 \)” and “\(\hbox {HfO}_2 \)”.

Similar content being viewed by others

References

Lee, C.-W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., Colinge, J.-P.: Junctionless multigate field effect transistor. Appl. Phys. Lett. 94, 053511 (2009)

Gnani, E., Gnudi, A., Reggiani, S., Baccarani, G.: Theory of the junctionless nanowire FET. IEEE Trans. Electron Devices 58(9), 2903 (2011)

Colinge, J.P., Lee, C.-W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., Razavi, P., O’Neill, B., Blake, A., White, M., Kelleher, A.-M., McCarthy, B., Murphy, R.: Nanowire transistors without junctions. Nat. Nanotechnol. 5(3), 225–229 (2010)

Solankia, T., Parmar, N.: A review paper: a comprehensive study of junctionless transistor. In: National Conference on Recent Trends in Engineering & Technology, 13–14 May 2011

Nazarov, A., Colinge, J.P., Balestra, F., et al.: Semiconductor-on-insulator Materials for Nanoelectronics Applications. Springer, New York (2011)

Colinge, J.P.: Junctionless transistors. In: IEEE International Meeting for Future of Electron Devices, Kansai (IMFEDK) (2012)

Gnudi, A., Susanna, R., Elena, G., Giorgio, B.: Analysis of threshold voltage variability due to random dopant fluctuations in junctionless FETs. IEEE Electron Dev. Lett. 33(3), 336–338 (2012)

Lou, H., Zhang, L., Zhu, Y., Lin, X., Yang, S., He, J., Chan, M.: A junctionless nanowire transistor with a dual-material gate. IEEE Trans. Electron Dev. 59(7), 1829–1836 (2012)

Duarte, J.P., Kim, M.-S., Choi, S.-J., Choi, Y.-K.: A compact model of quantum electron density at the subthreshold region for double-gate junctionless transistors. IEEE Trans. Electron Dev. 59(4), 1008–1012 (2012)

Gnudi, A., Reggiani, S., Gnani, E., Baccarani, G.: Semi analytical model of the subthreshold current in short-channel junctionless symmetric double-gate field-effect transistors. IEEE Trans. Electron Devices 60(4) (2013)

Cong, L., Yiqi, Z., Shaoyan, D., Ru, H.: Subthreshold behaviour models for nanoscale, short-channel junctionless cylindrical surrounding-gate MOSFETs. IEEE Trans. Electron Devices 60(11) (2013)

Holtij, T., Schwarz, M., Kloes, A., Iñíguez, B.: 13th International Conference on ULIS, 2D Analytical Potential Modelling of Junctionless DG MOSFETs in Subthreshold Region Including Proposal for Calculating the Threshold Voltage, pp. 81–84 (2012)

Chiang, T.-K.: A quasi-two-dimensional threshold voltage model for short-channel junctionless double-gate MOSFETs. IEEE Trans. Electron Devices 59(9), 2284–2289 (2012)

Chiang, T.-K.: A new quasi-2-D threshold voltage model for short channel junctionless cylindrical surrounding gate (JLCSG) MOSFETs. IEEE Trans. Electron Devices 59(11), 3127–3129 (2012)

Trevisoli, R.D., Doria, R.T., de Souza, M., Das, S., Ferain, I., Pavanello, M.A.: Surface potential based drain current analytical model for triple gate junctionless nanowire transistors. IEEE Trans. Electron Devices 59(11), 3510–3518 (2012)

Yan, R.H., Ourmazd, A., Lee, K.F.: Scaling the Si MOSFET: from bulk to SOI to bulk. IEEE Trans. Electron Devices 39(7), 1704 (1992)

Colinge, J.-P.: Multiple-gate SOI MOSFETs. Solid-State Electron. 48, 897–905 (2004)

Colinge, J.P.: The new generation of SOI MOSFETs. Rom. J. Inf. Sci. Technol. 11(1), 3–15 (2008)

Auth, C.P., Plummer, J.D.: Scaling theory for cylindrical, fully-depleted, surrounding-gate MOSFETs. IEEE Electron Device Lett. 18, 74 (1997)

Colinge, J.P., Colinge, C.A.: Physics of Semiconductor Devices, Kluwer Academic Publishers, New York, ISBN: 0-306-47622-3 (2002)

Teschl, G.: Ordinary Differential Equations and Dynamical Systems, American Mathematical Society, Providence, ISBN:978-0-8218-8328-0 (2011)

Author information

Authors and Affiliations

Corresponding author

Appendix

Appendix

This appendix shows how (5) can be obtained from (4).

At \(y=\frac{t_{Si} }{2}\), from (4),

From (15) putting \(\phi _s \) in (4),

Rights and permissions

About this article

Cite this article

Chandra Deva Sarma, K., Sharma, S. An approach for complete 2-D analytical potential modelling of fully depleted symmetric double gate junction less transistor. J Comput Electron 14, 717–725 (2015). https://doi.org/10.1007/s10825-015-0700-6

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-015-0700-6