Abstract

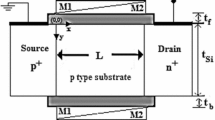

In this paper, a 2-D analytical model for electrical characteristics such as surface potential, drain current, and threshold voltage of dual metal (DM) heterogeneous gate dielectric (HGD) double-gate (DG) tunnel field-effect transistors (TFETs) with localized interface charges have been investigated. The surface potential model has been used to derive a compact model for the electric field by including the effects of the localized charges near the source/channel junction, mobile charges in channel region and the charges in the depletion regions formed at source/channel and drain/channel junctions. The band-to-band tunneling (BTBT) generation rate has been developed by considering the effect of the electric fields at both the source/channel and drain/channel junctions. The drain current has then been derived for all gate bias (i.e. ambipolar to forward gate bias) by using the tangent line approximation method. Finally, the threshold voltage model has been developed by using the concept of shortest tunneling path of DM-HGD DG-TFET under study. The impact of localized interface charges on the drain current and threshold voltage by varying the device dimensions are also investigated. The validity of our model results are verified by numerical simulation results obtained from 2-D device simulator ATLAS™ .

Similar content being viewed by others

References

Choi WY, Park BG, Lee JD, King Liu T-J (2007) Tunneling field- effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Trans Electron Devices 28(8):743–745. https://doi.org/10.1109/LED.2007.901273

Talukdar J, Rawat G, Mummaneni K (2019) A Novel Extended Source TFET with δp+− SiGe Layer. J Silicon 52. https://doi.org/10.1007/s12633-019-00321-3

Joshi T, Singh Y, Singh B (2020) Extended-source double-gate tunnel FET with improved DC and analog/RF performance. IEEE Trans Electron Devices 67(4):1873–1879. https://doi.org/10.1109/TED.2020.2973353

Kumar S, Goel E, Singh K, Singh B, Kumar M, Jit S (2016) A compact 2-D analytical model for electrical characteristics of double-gate tunnel-FETs with a SiO2/high-k stacked gate-oxide structure. IEEE Trans Electron Devices 63:3291–3299. https://doi.org/10.1109/TED.2016.2572610

Joshi T, Singh Y, Singh B (Oct. 2019) Dual-channel trench-gate tunnel FET for improved ON-current and subthreshold swing. Electron Lett 55(21):1152–1155. https://doi.org/10.1049/el.2019.2219

Joshi T, Singh B, Singh Y (2020) Controlling the ambipolar current in ultrathin SOI tunnel FETs using the back-bias effect. J Comput Electron 19:658–667. https://doi.org/10.1007/s10825-020-01484-8

Mishra A, Narang R, Saxena M, Gupta M (2016) Impact of interfacial fixed charges on the electrical characteristics of pocket-doped double-gate tunnel FET. IEEE Trans Devices Materials Reliabil 16(2):117–122. https://doi.org/10.1109/TDMR.2016.2533428

Talukdar J, Rawat G, Singh K, Mummaneni K (2020) Comparative analysis of the effects of trap charges on single- and double-gate extended-source tunnel FET with δp+ SiGe pocket layer. J Electron Mater 49:4333–4342. https://doi.org/10.1007/s11664-020-08151-5

Vishnoi R, Jagadesh Kumar M (2014) 2-D analytical model for the threshold voltage of a tunneling FET with localized charges. IEEE Trans Electron Devices 61(9):3054–3059. https://doi.org/10.1109/TED.2014.2332039

Bardon MG, Neves HP, Pures R, Van Hoof C (2010) Pseudo-two-dimensional model for double-gate-tunnel FETs considering the junctions depletion regions. IEEE Trans Electron Devices 57(4):827–834. https://doi.org/10.1109/TED.2010.2040661

Wang P, Zhuang YQ, Li C, Jiang Z, Liu YQ (2016) Drain current model for double-gate tunnel field-effect transistor with hetero-gate-dielectric and source-pocket. Microelectron Reliab 59:30–36. https://doi.org/10.1016/j.microrel.2015.09.014

Upasana R, Narang MS, Gupta M (2015) Modeling and TCAD assessment for gate material and gate dielectric engineered TFET architectures: circuit-level investigation for digital applications. IEEE Trans Electron Devices 62(10):3348–3356. https://doi.org/10.1109/TED.2015.2462743

Madan J, Gupta RS, Chaujar R (2015) Analytical drain current formulation for gate dielectric engineered dual material gate-gate all around-tunneling field effect transistor. Jpn J Appl Phys 54:094202–094209. https://doi.org/10.7567/JJAP.54.094202

Choi WY, Lee W (2010) Hetero-gate-dielectric tunneling field effect transistors. IEEE Trans Electron Devices 57(9):2317–2319. https://doi.org/10.1109/TED.2010.2052167

Mitra K, Goswami R, Bhowmick B (2016) A hetero-dielectric stack gate SOI-TFET with back gate and its application as a digital inverter. J Superlattices Microstruct 92(3):37–51. https://doi.org/10.1016/j.spmi.2016.01.040

Saurabh S, Kumar MJ (2011) Novel attributes of a dual material gate nanoscale tunnel field-effect transistor. IEEE Trans Electron Devices 58(2):404–410. https://doi.org/10.1109/TED.2010.2093142

Vishnoi R, Kumar MJ (2015) A compact analytical model for the drain current of gate-all-around nanowire tunnel FET accurate from sub-threshold to ON-state. IEEE Trans Nanotech 14(2):358–362. https://doi.org/10.1109/TNANO.2015.2395879

Kumar S, Goel E, Singh K, Singh B, Baral K, Singh PK, Jit S (2017) 2-D analytical modeling of the electrical characteristics of dual-material DG TFETs with a SiO2/HfO2 stacked gate-oxide structure. IEEE Trans Electron Devices 64:960–968. https://doi.org/10.1109/TED.2017.2656630

Wu C, Huang R, Huang Q, Wang C, Wang J, Wang Y (2014) An analytical surface potential model accounting for the dual-modulation effects in tunnel FETs. IEEE Trans Electron Devices 61(8):2690–2696. https://doi.org/10.1109/TED.2014.2329372

Jain P, Yadav C, Agarwal A, Chauhan YS (2017) Surface potential based modeling of charge, current, and capacitances in DG TFET including mobile channel charge and ambipolar behaviour. Solid State Electron 134:74–81. https://doi.org/10.1016/j.sse.2017.05.012

Zhou X (2000) Exploring the novel characteristics of hetero-material gate field-effect transistors with gate-material engineering. IEEE Trans Electron Device 47(1):113–120. https://doi.org/10.1109/16.817576

G. Lee, J.-S. Jang, and W. Y. Choi, “Dual-dielectric-constant spacer hetero-gate dielectric tunneling field-effect transistors,” Semicond Sci Technol, vol. 28, no. 5, p. 052001, 2013, doi:https://doi.org/10.1088/0268-1242/28/5/052001

Guan Y, Li Z, Zhang W, Zhang Y (2017) An accurate analytical current model of double-gate heterojunction TFET. IEEE Trans Electron Devices 64(3):938–944. https://doi.org/10.1109/TED.2017.2654248

Chander S, Baishya S (July 2015) A two-dimensional gate threshold voltage model for a heterojunction SOI-tunnel FET with oxide/source overlap. IEEE Electron Device Let 36(7):714–716. https://doi.org/10.1109/LED.2015.2432061

Boucart K, Ionescu AM (2008) A new definition of threshold voltage in tunnel FETs. Solid State Electron 52:1318–1323. https://doi.org/10.1016/j.sse.2008.04.003

Vandenberghe WG, Sorée B, Magnus W, Groeseneken G, Fischetti MV (2011) Impact of field-induced quantum confinement in tunneling field-effect devices. Appl Phys Lett 98:143503–143503. https://doi.org/10.1063/1.3573812

ATLAS (2013) 2-D Device Simulator. SILVACO Int, Santa Clara, CA, USA

Lin S, Kuo J (Dec. 2003) Modeling the fringing electric field effect on the threshold voltage of FD SOI nMOS devices with the LDD/sidewall oxide spacer structure. IEEE Trans Electron Devices 50(12):2559–2564. https://doi.org/10.1109/TED.2003.816910

Shen C, Ong S, Heng C, Samudra G, Yeo Y (2008) A Variational approach to the two-dimensional nonlinear Poisson’s equation for the modeling of tunneling transistors. IEEE Electron Devices Lett 29(11):1252–1255. https://doi.org/10.1109/LED.2008.2005517

Pan A, Chui C (2012) A quasi-analytical model for double-gate tunneling field-effect transistors. IEEE Electron Devices Lett 33(10):1468–1470. https://doi.org/10.1109/LED.2012.2208933

Kane EO (Jan. 1960) Zener tunneling in semiconductors. J Phys Chem Solids 12(2):181–188. https://doi.org/10.1016/0022-3697(60)90035-4

Zhang L, Chan M (Feb. 2014) SPICE modeling of double-gate tunnel-FETs including channel transports. IEEE Trans Electron Devices 61(2):300–307. https://doi.org/10.1109/TED.2013.2295237

Pal A, Dutta AK (2016) Analytical drain current modeling of double-gate tunnel FETs. IEEE Trans Electron Devices 63(8):3213–3221. https://doi.org/10.1109/TED.2016.2581842

Choi WY, Lee HK (2016) Demonstration of hetero-gate-dielectric tunneling field-effect transistors (HG TFETs). Nano Convergence 3(1):1–15. https://doi.org/10.1186/s40580-016-0073-y

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Kumar, S., Singh, K., Baral, K. et al. 2-D Analytical Model for Electrical Characteristics of Dual Metal Heterogeneous Gate Dielectric Double-Gate TFETs with Localized Interface Charges. Silicon 13, 2519–2527 (2021). https://doi.org/10.1007/s12633-020-00564-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-020-00564-5