Abstract

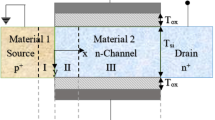

This paper deals with electrostatic behavior of triple-material gate-all-around hetero-junction tunneling field-effect transistors (TMGAA-HJTFET) device. The model is advantageous in apprehending a comparative study with the single-material gate-all-around hetero-junction tunneling field-effect transistors (SMGAA-HJTFET) in terms of surface potential, electric field, drain current, transconductance, and threshold voltage. The surface-potential distribution in partition regions along the channel is solved by using two-dimensional Poisson’s equation. By using the drift and diffusion current, drain current is derived, and IOn/IOff ratio of 1011 is gained from analytical modeling and TCAD simulation. Transconductance and threshold voltage are derived from the tunneling current. The proposed model results are validated by the ATLAS TCAD simulation tool.

Similar content being viewed by others

REFERENCES

A. C. Seabaugh and Q. Zhang, Proc. IEEE 98, 2095 (2010).

Y. C. Woo, B.-G. Park, J. D. Lee, and T.-J. King Liu, IEEE Electron Dev. Lett. 28, 743 (2007).

K. K. Bhuwalka, J. Schulze, and I. Eisele, IEEE Trans. Electron Dev. 52, 909 (2005).

G. F. Jiao, Z. X. Chen, H. Y. Yu, X. Y. Huang, D. M. Huang, N. Singh, G. Q. Lo, D.-L. Kwong, and M.-F. Li, in Proceedings of the IEEE International Electron Devices Meeting (IEDM) (2009), p. 741.

A. Pan and C. O. Chi, IEEE Electron Dev. Lett. 33, 1468 (2012).

L. Zhang, X. Lin, J. He, and M. Chan, IEEE Trans. Electron Dev. 59, 3217 (2012).

C. Usha and P. Vimala, in Proceedings of the International Conference on Innovations in Information, Embedded and Communication Systems, Coimbatore, Tamilnadu, India,2015, p. 72.

R. Vishnoi and M. J. Kumar, IEEE Trans. Electron Dev. 61, 1936 (2014).

P. Pandey, R. Vishnoi, and M. J. Kumar, J. Comput. Electron. 14, 280 (2015).

T. S. A. Samuel and S. Komalavalli, J. Nano Res. 54, 146 (2018).

Q. Shao, C. Zhao, C. Wu, J. Zhang, L. Zhang, and Z. Yu, in Proceedings of the International Conference on Electron Devices and Solid State Circuit (EDSSC),2013, p. 1.

R. Vishnoi and M. J. Kumar, IEEE Trans. Electron Dev. 61, 2599 (2014).

A. Zhan, J. Mei, L. Zhang, H. He, J. He, and M. Chan, in Proceedings of the International Conference Electron Devices, Solid State Circuit (EDSSC),2012, p. 1.

R. Vishnoi and M. J. Kumar, IEEE Trans. Electron Dev. 61, 2264 (2014).

C. Usha and P. Vimala, J. Nano Res. 55, 75 (2018).

C. Usha, P. Vimala, T. S. Arun Samuel, and M. Karthigai Pandian, J. Comput. Electron. 19, 1144 (2020).

C. Usha and P. Vimala, AEUE Int. J. Electron. Commun. (2019). https://doi.org/10.1016/j.aeue.2019.152877

S. Kumar, E. Goel, K. Singh, B. Singh, M. Kumar, and S. Jit, IEEE Trans. Electron Dev. 63, 3291 (2016).

S. M. Sze, Physics of Semiconductor Devices (Wiley, New York, 1981).

M. Garcia Bardon, H. P. Neves, and R. Puers, and C. van Hoof, IEEE Trans. Electron Dev. 57, 827 (2010).

Md. Arafat Mahmud and S. Subrina, J. Comput. Electron. 15, 525 (2016).

Y. Tsividis, Operation and Modelling of The MOS Transistor, 2nd ed. (McGraw-Hill, New York, 1989).

A. Akers, Solid State Electron. 23, 173 (1989).

ACKNOWLEDGMENTS

This work was supported by Women Scientist Scheme-A, Department of Science and Technology, New Delhi, Government of India, under the Grant SR/WOS-A/ET-5/2017.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

The authors declare that they have no conflict of interest.

Rights and permissions

About this article

Cite this article

Usha, C., Vimala, P. Analytical Drain Current Modeling and Simulation of Triple Material Gate-All-Around Heterojunction TFETs Considering Depletion Regions. Semiconductors 54, 1634–1640 (2020). https://doi.org/10.1134/S1063782620120398

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1134/S1063782620120398