Abstract

Capacitors occupy very large area on chips. To reduce the occupation area on chip for circuits employing large capacitances, capacitance multipliers are used. In this work, a new design of Voltage Differencing Transconductance Amplifier based capacitance multiplier and its CMOS implementation are proposed. The multiplication factor of the proposed circuit can be electronically tunable between 115 and 150. The design of the proposed grounded capacitor multiplier is verified with the simulations in Cadence environment with 0.18 µm TSMC technology. Also, Monte-Carlo analysis and temperature behavior are investigated under post-layout realization of the proposed multipler circuit (27.58 µm × 44.68 µm). Taken into consideration with respect to counterparts studies in the literature, proposed architecture gives promising results under different operating conditions for the low frequency applications.

Similar content being viewed by others

Data availability

Data sharing not applicable to this article as no datasets were generated or analyzed during the current study.

References

Shu, K., Sánchez-Sinencio, E., José, S.-M., & Sherif, H. K. E. (2003). A 2.4-GHz monolithic fractional-N frequency synthesizer with robust phase-switching prescaler and loop capacitance multiplier. IEEE Journal of Solid-State Circuits, 38(6), 866–874.

Tang, Y., Ismail, M., & Bibyk, S. (2003). Adaptive miller capacitor multiplier for compact on-chip PLL filter. Electronics Letters, 39(1), 43–45.

Choi, J., Park, J., Kim, W., & Laskar, J. (2009). High multiplication factor capacitor multiplier for an on-chip PLL loop filter. Electronics Letters, 45(5), 239–240.

Germanovix, W., Bonizzoni, E., & Maloberti, F. (2018). Capacitance super multiplier for sub-hertz low-pass integrated filters. IEEE Transactions on Circuits and Systems II: Express Briefs, 65(3), 301–305.

Alaybeyoglu, E. (2019). Implementation of capacitor multiplier with cell-based variable transconductance amplifier. IET Circuits, Devices and Systems, 13(3), 267–272.

Sotner, R., Jerabek, J., Polak, L., & Petrzela, J. (2020). Capacitance multiplier using small values of multiplication factors for adjustability extension and parasitic resistance cancellation technique. IEEE Access, 8, 144382–144392.

Shukla, A., & Gupta, P. (2017). Current-mode PMOS capacitance multiplier. In 2017 international conference on inventive systems and control (ICISC) (pp. 1–4). IEEE.

Biolek, D., Vavra, J., & Keskin, A. Ü. (2019). CDTA-based capacitance multipliers. Circuits, Systems, and Signal Processing, 38(4), 1466–1481.

Tanzawa, T. (2010). On two-phase switched-capacitor multipliers with minimum circuit area. IEEE Transactions on Circuits and Systems I: Regular Papers, 57(10), 2602–2608.

Alaybeyoğlu, E., & Kuntman, H. (2019). Capacitor multiplier with high multiplication factor for integrated low pass filter of biomedical applications using DTMOS technique. AEU: International Journal of Electronics and Communications, 107, 291–297.

Padilla-Cantoya, I., & Furth, P. M. (2015). Enhanced grounded capacitor multiplier and its floating implementation for analog filters. IEEE Transactions on Circuits and Systems II: Express Briefs, 62(10), 962–966.

Aguado-Ruiz, J., Lopez-Martin, J., & Ramirez-Angulo, A. J. (2012). Three novel improved CMOS C-multipliers. International Journal of Circuit Theory and Applications, 40(6), 607–616.

Al-Absi, M. A. (2018). A new CMOS tunable floating capacitance multiplier. International Journal of Electronics Letters, 6(1), 48–57.

Alaybeyoglu, E., Atasoyu, M., & Kuntman, H. (2015). Frequency agile filter structure improved by MOS-only technique. In 2015 38th international conference on telecommunications and signal processing, TSP 2015. https://doi.org/10.1109/TSP.2015.7296393

Özenli, D., Alaybeyoğlu, E., & Kuntman, H. (2021). A grounded capacitance multiplier circuit employing VDTA. In 13th international conference on electrical and electronics engineering (ELECO) (pp. 38–41). IEEE.

Satansup, J., & Tangsrirat, W. (2014). Compact VDTA-based current-mode electronically tunable universal filters using grounded capacitors. Microelectronics Journal, 45(6), 613–618.

Alaybeyoğlu, E., & Kuntman, H. (2016). CMOS implementations of VDTA based frequency agile filters for encrypted communications. Analog Integrated Circuits and Signal Processing, 89(3), 675–684.

Vista, J., & Ranjan, A. (2020). High frequency meminductor emulator employing VDTA and its application. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 39(10), 2020–2028.

Petrović, P. B. (2018). Floating incremental/decremental flux-controlled memristor emulator circuit based on single VDTA. Analog Integrated Circuits and Signal Processing, 96(3), 417–433.

Yesil, A., Babacan, Y., & Kacar, F. (2019). “Design and Experimental Evolution of Memristor with only One VDTA and One Capacitor”, IEEE Trans. Comput. Des. Integr. Circuits Syst., 38(6), 1123–1132.

Banerjee, K., Singh, D., & Paul, S. K. (2019). Single VDTA based resistorless quadrature oscillator. Analog Integr. Circuits Signal Process., 100(2), 495–500.

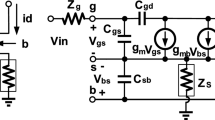

Yeşil, A., Kaçar, F., & Kuntman, H. (2011). New simple CMOS realization of voltage differencing transconductance amplifier and its RF filter application. Radioengineering, 20(3), 632–637.

Yucehan, T., & Yuce, E. (2021). A new grounded capacitance multiplier using a single ICFOA and a grounded capacitor. IEEE Transactions on Circuits and Systems II: Express Briefs, 69(3), 729–733.

Metin, B., & Cicekoglu, O. (2006). A novel floating lossy inductance realization topology with NICs using current conveyors. IEEE Transactions on Circuits and Systems II: Express Briefs, 53(6), 483–486.

Rodriguez-Villegas, E., Casson, A. J., & Corbishley, P. (2011). A subhertz nanopower low-pass filter. IEEE Transactions on Circuits and Systems II: Express Briefs, 58(6), 351–355.

Sreenivasulu, P., Hanumantha Rao, G., Rekha, S., & Bhat, M. S. (2019). A 0.3 V, 56 dB DR, 100 Hz fourth order low-pass filter for ECG acquisition system. Microelectronics Journal, 94, 104652.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Ozenli, D., Alaybeyoglu, E. & Kuntman, H. A tunable lossy grounded capacitance multiplier circuit based on VDTA for the low frequency operations. Analog Integr Circ Sig Process 113, 163–170 (2022). https://doi.org/10.1007/s10470-022-02077-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-022-02077-0