Abstract

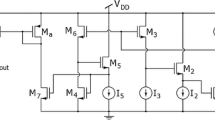

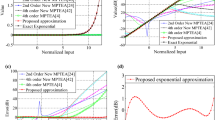

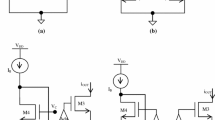

This paper presents a new current-mode squaring circuit. The design is based on MOSFETs translinear principle in strong inversion. A new compensation technique to minimize the second order effects caused by carrier mobility reduction in short channel MOSFETs is proposed. Tanner T-spice simulation tool is used to confirm the functionality of the proposed design in 0.18 µm CMOS process technology. Simulation results indicate that the maximum linearity error is 1.2 %; power consumption is 326 µW and bandwidth of 340 MHz.

Similar content being viewed by others

References

Chen, C.-Y., Huang, C.-Y., & Liu, B.-D. (1997). Current-mode defuzzifier circuit to realise the centroid strategy. IEE Proceedings-Circuits, Devices and Systems, 144(5), 265–271.

Filanovsky, I. M., & Baltes, H. P. (1992). Simple CMOS analog square-rooting and squaring circuits. IEEE Transaction on Circuits and Systems-I, 39(4), 312–315.

Gai, W., Chen, H., & Seevinck, E. (1997). Quadratic-translinear CMOS multiplier/divider circuit. IEE Electronics Letter, 33(10), 860–861.

Tanno, K., Ishizuka, O., & Tang, Z. (2000). Four-quadrant CMOS current mode multiplier in dependent of device parameters. IEEE Transaction on Circuits System II, 47, 473.

Naderi, A., Mojarrad, H., Ghasemzadeh, H., Khoei, A., & Hadidi, K. (2009). Four-quadrant CMOS analog multiplier based on new current squarer circuit with high-speed. In EUROCON 2009, EUROCON’09. IEEE, (pp. 282–287).

De La Cruz-Blas, C. A., Lopez-Martín, A., & Carlosena, A. (2003). 1.5-V MOS translinear loops with improved dynamic range and their applications to current-mode signal processing. IEEE Transaction on Circuits and Systems II: Analog and Digital Signal Processing, 50(12), 918–927.

De La Blas, C.A., Lopez, A. (Sept, 2008). A novel two quadrant MOS trans-linear Squarer-divider cell. In ICECS 2008. 15th IEEE International Conference on Electronics, Circuits and Systems, 2008 (pp. 5–8).

Mulder, J., Serdijn, W. A., Van Der Woerd, A. C., & Van Roermund, A. H. M. (1998). 3.3 V current-controlled Square-domain oscillator. Analog Integrated Circuits and Signal Processing, 16, 17–28.

Wisetphanichkij, S., Singkrajom, N., Kumngern M., & Dejhan, K. (Oct, 2005). A low-voltage CMOS current squarer circuit. In IEEE International Symposium on Communications and Information Technology, 2005 (Vol. 1, pp. 271–274).

Menekay, S., Tarcan, R. C., Kuntman H. (2008). Novel high-precision current-mode circuits based on the MOS-translinear principle. International Journal of Electronic Communication (AEU). doi:10.1016/j.aeue.2008.08.010.

Chaisayun, I., Dejhan, K., & Piangprantong, S. (2012). Versatile analog squarer and multiplier free from body effect. Analog Integrated Circuits and Signal Processing, 71(3), 539–547.

Ibaragi, E., Hyogo, A., & Seikine, K. (1998), A novel CMOS OTA free from mobility degradation effect. In IEEE Asia Pacific Conference of Circuit and Systems, 1998 (pp. 241–244).

Yang, S. H., et al. (2005). A novel CMOS operational transconductance amplifier based on a mobility compensation technique. IEEE Transaction on Circuits Systems II: Express Briefs, 52(1), 37–42.

Tanno, K., Ide, D., Nishimura, K., Tanaka, H., & Tamura, H. (2008). Highly-linear CMOS OTA with compensation of mobility reduction. In IEEE Asia Pacific Conference on Circuits and Systems, 2008 (pp. 810–813).

Sengupta, S. (2005). Adaptively biased linear transconductor. IEEE Transaction on Circuits and Systems–I: Regular Papers, 52(11), 2369–2375.

Menekay, S., Tarcan, R. C., Kuntman H. (2007). Novel high precision current-mode multiplier/divider. In International Conference on Electrical and Electronics Engineering, (ELECO-2007) (pp. 5–9).

Tarcan R. C., & Kuntman, H. (2007). CMOS high precision current-mode squarer/divider circuit. In IEEE 15th Signal Processing and Communications Applications, 2007. SIU 2007 (pp. 1–4).

Tavassoli, M., Khoei, A., Hadidi, Kh. (2011). High-precision MOS-trans-linear loop-based squarer/divider circuit free from mobility reduction. In 19th Conference on Electrical Engineering, Iran.

Chaisayun, I., Piangprantong, S., & Dejhan, K. (2012). Versatile analog squarer and multiplier free from body effect. Analog Integrated Circuits and Signal Processing, 71(3), 539–547.

Seon, J.-K. (2008). Design and application of precise analog computational circuits. Analog Integrated Circuits and Signal Processing, 54(1), 55–66.

AL-Absi, M. A., Assaban, I. (2013). A new current-mode squaring circuit with compensation for error resulting from carrier mobility reduction. In Eleco Dec, 2013 (pp. 358–361).

Acknowledgments

The authors would like to thank KFUPM and KACST for supporting this research.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

AL-Absi, M.A., As-Sabban, I.A. A CMOS current-mode squaring circuit free of error resulting from carrier mobility reduction. Analog Integr Circ Sig Process 81, 23–28 (2014). https://doi.org/10.1007/s10470-014-0319-8

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-014-0319-8