Abstract

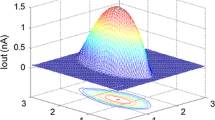

New versatile building blocks for implementing analog functional circuits such as a multiplier, a squarer, and a square rooter based on functional terms of a differential input circuit are proposed and implemented in 0.25 um CMOS process. The input range of these circuits is over ±1.0 V with a high linearity of less than 4% for 3.3 V power supply. The −3 dB bandwidth of all discussed circuits has been measured to over 200 MHz. The functional circuit size is 340 μm2, and its typical power consumption is about 90 uW.

Similar content being viewed by others

References

Bult, K., & Wallinga, H. (1987). A class of analog CMOS circuits based on the square-law characteristics of an MOS transistor in saturation. IEEE Journal of Solid-State Circuits, SC-22, 357–365.

Zarabadi, S. R., Ismail, M., & Hung, C.-C. (1998). High performance analog VLSI computational circuits. IEEE Journal of Solid-State Circuits, SC-33, 644–649.

Song, H., & Kim, C. (1990). A MOS four-quadrant analog multiplier using simple two-input squaring circuits with source followers. IEEE Journal of Solid-State Circuits, SC-25, 841–894.

Wang, Z. (1991). A CMOS four-quadrant analog multiplier with single-ended voltage output and improved temperature performance, IEEE Journal of Solid-State Circuits, SC-26, 1293–1301.

Lande, T. S., Nesheim, J. A., & Berg, Y. (1995). Auto correlation in micropower analog CMOS. Analog Integrated Circuits and Signal Processing, 1, 61–68.

Liu, S.-I., Chang, C.-C., & Hwang, Y.-S. (1996). New CMOS four-quadrant multiplier and squarer circuits. Analog Integrated Circuits and Signal Processing, 9, 257–263.

Liu, S.-I. (1995). Square-rooting and vector summation circuits using current conveyors. IEE Proceedings Circuits, Devices & Systems, 142(4), 223–226.

Torrance, R. R., Viswanathan, T. R., & Hanson, J. V. (1985). CMOS voltage to current transducers. IEEE Transactions on Circuits and Systems, CAS-32(11), 1097–1985.

Nedungadi, A., & Viswanathan, T. R. (1984). Design of linear CMOS transconductance elements. IEEE Transactions on Circuits and Systems, CAS-31, 891–894.

Seevink, E., & Wassenaar, R. F. (1987). A versatile CMOS linear tranconductor/square-law function circuit, IEEE Journal of Solid-State Circuits, SC-22(3), 366–377.

Chen, C., & Li, Z. (2006). A low-power CMOS analog multiplier. IEEE Transactions on Circuits and Systems II, 53, 100–104.

Demosthenous, A., & Panovic, M. (2005). Low-voltage MOS linear transconductor/squarer and four-quadrant multiplier for analog VLSI. IEEE Transactions on Circuits and Systems I, 52, 1721–1731.

Cruz-Blas, C. A., Lopez-Martin, A., & Carlosena, A. (2003). 1.5-V MOS translinear loops with improved dynamic range and their applications to current-mode signal processing. IEEE Transactions on Circuits and Systems II, 50, 918–927.

Gray, P. R., Hurst, P. J., Lewis, S. H., & Meyer, R. G. (2003). Analysis and design of analog integrated circuits (4th ed, p. 75). John Wiley & Sons.

Bruun, E. (1999). Analytical expressions for harmonic distortion at low frequencies due to device mismatch in CMOS current mirrors. IEEE Transactions on Circuits and Systems II, 46, 937–941.

Palmisano, G., Palumbo, G., & Pennisi, S. (1995). High linearity CMOS current output stage. Electronics Letters, 31(10), 789–790.

Balmford, R. A. H., & Redman-White W. (1993). New high-compliance CMOS current mirror with low harmonic distortion for high frequency circuits. Electronics Letters, 29(20), 1738–1739.

Pelgrom, M. J. M., Duinmaijer, A. C. J., & Welbers, A. P. G. (1989). Matching properties of MOS transistors, IEEE Journal of Solid-State Circuits, SC-24, 1433–1439.

Michael, C., & Ismail, M. (1992). Statistical modeling of device mismatch for analog MOS integrated circuits. IEEE Journal of Solid-State Circuits, SC-27, 154-166.

Han, G., & Sanchez-Sinencio, E. (1998). CMOS transconductance multipliers: A tutorial. IEEE Transactions on Circuits and Systems II, 45, 1550–1563.

Tanno, K., Ishizuka, O., & Tang, Z. (2000). Four-quadrant CMOS current-mode multiplier independent of device parameters. IEEE Transactions on Circuits and Systems II, 47, 474–477.

Chang, C. C., & Liu, S. I. (2000). Current-mode full-wave rectifier and vector summation circuit. Electronics Letters, 36(19), 1599–1600.

Acknowledgments

This work was supported by the Telemetrics Laboratory of LG Industrial Systems Co., Ltd., Korea. The author would like to thank technical staffs of LGIS for measurements and discussions, and Prof. Jean-Jacques Charlot (ENST, France) for guidance and encouragement.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Seon, JK. Design and application of precise analog computational circuits. Analog Integr Circ Sig Process 54, 55–66 (2008). https://doi.org/10.1007/s10470-007-9119-8

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-007-9119-8