Abstract

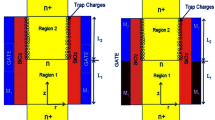

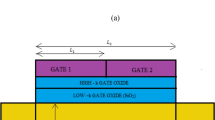

Physics-based analytical model is proposed in this paper which analyzes the effect of temperature, channel length and silicon film radius on gate-induced drain leakages (GIDL) in dual-metal junctionless accumulation nano-tube FET (DM-JAM-TFET). Formulation and analysis for electric field, Ez, surface potential and gate-induced drain leakage current, Igidl have been done with the help of appropriate boundary conditions utilized in solving two-dimensional Poisson’s equation. Also, the effect of variation in temperatures at T = 300 K and 500 K, silicon film channel length (L 30 nm and 40 nm) and radius of R = 9 nm and R = 10 nm have been studied. The simulated results seem to be in good compliance with the analytical results. To analyze the applicability of DM-JAM-TFET for RFIC applications, linearity of the aforesaid device has been deeply investigated by comparing DM-JAM-TFET with JAM-GAA and DM-JAM-GAA at channel length, L = 20 nm. The linearity metrics namely gm1, gm2, gm3, VIP2, VIP3, IMD3 and IIP3 have been significantly improved in DM-JAM-TFET making it intermodulation distortion resistant.

Similar content being viewed by others

References

Semiconductor Industry Association, The National Technology Roadmap for Semiconductor Technology Needs (Sematech, Austin, 2019)

Y. Taur, T.H. Ning, Fundamentals of Modern VLSI Devices (Cambridge University Press, Cambridge, 1998)

T. Sekigawa, Y. Hayashi, Calculated threshold-voltage characteristics of an XMOS transistor having an additional bottom gate. Solid State Electron. 27, 827–828 (1984). https://doi.org/10.1016/0038-1101(84)90036-4

R.H. Yan, A. Ourmazd, K.F. Lee, Scaling the Si MOSFET: from bulk to SOI to bulk. IEEE Trans. Electron Devices 39, 1704–1710 (1992). https://doi.org/10.1109/16.141237

D. Frank, S.E. Laux, M.V. Fischetti, Monte Carlo simulation of a 30 nm dual-gate MOSFET: How short can Si go?, in IEDM Technical Digest, (1992), pp. 553–556. https://doi.org/10.1109/iedm.1992.307422

S. Saurabh, M.J. Kumar, Fundamentals of Tunnel Field-Effect Transistors (CRC Press, Boca Raton, 2016)

S. Nandy, S. Srivastava, S. Rewari, V. Nath, R.S. Gupta, Dual metal Schottky barrier asymmetric gate stack cylindrical gate all around (DM-SB-ASMGS-CGAA) MOSFET for improved analog performance for high frequency application. Microsyst. Technol. (2019). https://doi.org/10.1007/s00542-019-04577-y

K.J. Kuhn, Considerations for ultimate CMOS scaling. IEEE Trans. Electron Devices 59(7), 1813–1828 (2012). https://doi.org/10.1109/TED.2012.2193129

M. Li, K.H. Yeo, S.D. Suk, Y.Y. Yeoh, D.-W. Kim, T.Y. Chung, K.S. Oh, W.-S. Lee, Sub-10 nm gate-all-around CMOS nanowire transistors on bulk Si substrate. in Symposium on VLSI Technology, (IEEE, 2009), pp. 94–95

A. Goel, S. Rewari, S. Verma, R.S. Gupta, Shallow extension engineered dual material surrounding gate (SEE-DM-SG) MOSFET for improved gate leakages, analysis of circuit and noise performance. AEU Int. J. Electron. Commun. 111, 152924 (2019)

S. Bangsaruntip, G.M. Cohen, A. Majumdar, Y. Zhang, S.U. Engelmann, N.C.M. Fuller, L.M. Gignac, S. Mittal, J.S. Newbury, M. Guillorn, T. Barwicz, High performance and highly uniform gate-all around silicon nanowire MOSFETs with wire size dependent scaling. in IEDM Technical Digest (2009), pp. 297–300. https://doi.org/10.1109/iedm.2009.5424364

S. Rewari, V. Nath, S. Haldar, S.S. Deswal, R.S. Gupta, Hafnium oxide based cylindrical junctionless double surrounding gate (CJLDSG) MOSFET for high speed, high frequency digital and analog applications. Microsyst. Technol. J. (2017). https://doi.org/10.1007/s00542-017-3436-3

D.I. Moon, S.J. Choi, J.P. Duarte, Y.K. Choi, Investigation of silicon nanowire gate-all-around junctionless transistors built on a bulk. IEEE Trans. Electron Devices 60(4), 1355–1360 (2013). https://doi.org/10.1109/TED.2013.2247763

A. Goel, S. Rewari, S. Verma, R.S. Gupta, High-K spacer dual-metal gate stack underlap junctionless gate all around (HK-DMGS-JGAA) MOSFET for high frequency applications. Microsyst. Technol. (2019). https://doi.org/10.1007/s00542-019-04715-6

B.V. Zeghbroeck, Principles of semiconductor devices., University of Colorado (Colarado, USA, 2011)

Y.S. Yu, A unified analytical current model for N- and P-type accumulation- mode (junctionless) surrounding-gate nanowire FETs. IEEE Trans. Electron Devices 61(8), 3007–3010 (2014). https://doi.org/10.1109/TED.2014.2329916

M.M.H. Iqbal, Y. Hong, P. Garg, F. Udrea, The nanoscale silicon accumulation-mode MOSFET a comprehensive numerical study. IEEE Trans. Electron Devices 55(11), 2946–2958 (2014). https://doi.org/10.1109/ted.2008.2005174

J.P. Colinge, C.W. Lee, N.D. Akhavan, R. Yan, I. Ferain, P. Razavi, A. Kranti, R. Yu, Junctionless transistors physics and properties, semiconductor on insulator materials for nanoelectronics applications and engineering materials (Spinger, Berlin, 2011). https://doi.org/10.1007/978-3-642-15868-1_10

J. Fan, M. Li, X. Xu, Y. Yang, H. Xuan, R. Huang, Insight into gate-induced drain leakage in silicon nanowire transistors. IEEE Trans. Electron Devices 62(1), 213–219 (2015). https://doi.org/10.1109/TED.2014.2371916

J. Hur, B.H. Lee, M.H. Kang, D.C. Ahn, T. Bang, S.B. Jeon, Y.K. Choi, Comprehensive analysis of gate-induced drain leakage in vertically stacked nanowire FETs: inversion-mode versus junctionless mode. IEEE Electron Device Lett. 37(5), 541–544 (2016). https://doi.org/10.1109/LED.2016.2540645

S. Rewari, V. Nath, S. Haldar, S.S. Deswal, R.S. Gupta, A novel design to improve band to band tunneling and to reduce gate induced drain leakages (GIDL) in cylindrical gate all around (GAA) MOSFET. Microsyst. Technol. J. (2017). https://doi.org/10.1007/s00542-017-3446-1

T. Hoffmann, G. Doornbos, I. Ferain, N. Collaert, P. Zimmerman, M. Goodwin, R. Rooyackers, A. Kottantharayil, Y. Yim, A. Dixit, K. De Meyer, GIDL (gate-induced drain leakage) and parasitic Schottky barrier leakage elimination in aggressively scaled HfO2/TiN FinFET devices. in IEDM Technical Digest, (2005), pp. 725–729. https://doi.org/10.1109/iedm.2005.1609455

S. Sahay, M.J. Kumar, Controlling L-BTBT in emerging nanotube FETs using dual-material gate. IEEE J. Electron Device Soc. 6, 611–621 (2018). https://doi.org/10.1109/JEDS.2018.2829633

B. Razavi, RF Microelectronics (Prentice-Hall, Upper Saddle River, 1998)

P. Ghosh, S. Haldar, R.S. Gupta, M. Gupta, An investigation of linearity performance and intermodulation distortion of GME CGT MOSFET for RFIC designs. IEEE Trans. Electron Devices 59(12), 3263–3268 (2012). https://doi.org/10.1109/TED.2012.2219537

T. Wang, L. Lou, C. Lee, A junctionless gate-all-around silicon nanowire FET of high linearity and its potential applications. IEEE Electron Devices Lett. 34(4), 478–480 (2013). https://doi.org/10.1109/LED.2013.2244056

R. Lin, Q. Lu, P. Ranade, T.J. King, C. Hu, An adjustable work function technology using Mo gate for CMOS devices. IEEE Electron Devices Lett. 23(1), 49–51 (2002). https://doi.org/10.1109/55.974809

ATLAS User’s Manual: 3-D Device Simulator, SILVACO International, Version5.14.0.R, 2018

H. Cheng, S. Uno, K. Nakazato, Analytic compact model of ballistic and quasi-ballistic transport for cylindrical gate-all-around MOSFET including drain-induced barrier lowering effect. J. Comput. Electron. 14(1), 321–328 (2015)

G. Timp et al., The ballistic nano-transistor. in IEDM Technical Digest, Washington, DC, USA, (1999), pp. 55–58

A. Tsormpatzoglou, D.H. Tassis, C.A. Dimitriadis, G. Ghibaudo, G. Pananakakis, R. Clerc, A compact drain current model of shortchannel cylindrical gate-all-around MOSFETs. Semicond. Sci. Technol. 24(7), 075017 (2009)

A. Goel, S. Rewari, S. Verma, R.S. Gupta, Temperature-dependent gate-induced drain leakages assessment of dual-metal nanowire field-effect transistor—analytical model. IEEE Trans. Electron Devices 66(5), 2437–2445 (2019). https://doi.org/10.1109/ted.2019.2898444

N. Gupta, J.B. Patel, A.K. Raghav, “Performance and a new 2-D analytical modeling of a dual-halo dual-dielectric triple-material surrounding-gate-all-around (DH-DD-TM-SGAA) MOSFET. J. Eng. Sci. Technol. 13(11), 3619–3631 (2018)

M. Hasanuzzaman, S.K. Islam, L.M. Tolber, Effects of temperature variation (300–600 K) in MOSFET modeling in 6H-silicon carbide. Solid State Electron. 48, 125–132 (2004)

S. Sahay, M.J. Kumar, Nanotube junctionless field effect transistor: proposal, design and investigation. IEEE Trans. Electron Devices 64(4), 1851–1856 (2017). https://doi.org/10.1109/TED.2017.2672203

Acknowledgements

Authors are grateful to the Director, Maharaja Agrasen Institute of Technology for providing necessary facilities to carry out this research work.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Appendix

Appendix

Rights and permissions

About this article

Cite this article

Goel, A., Rewari, S., Verma, S. et al. Physics-based analytic modeling and simulation of gate-induced drain leakage and linearity assessment in dual-metal junctionless accumulation nano-tube FET (DM-JAM-TFET). Appl. Phys. A 126, 346 (2020). https://doi.org/10.1007/s00339-020-03520-7

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-020-03520-7