Abstract

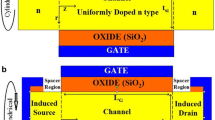

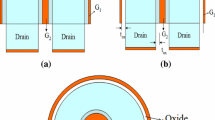

This paper proposes a physics-based 2-D analytical model for a dual- material gate stack engineered junctionless accumulation-mode cylindrical surrounding gate (DMGSE-JAM-CSG) MOSFET. Analytical modeling is performed using 2-D Poisson’s equation in cylindrical co-ordinate system based upon parabolic potential approximation. This analysis derives the expressions for center potential, electric field, subthreshold drain current, transconductance, output conductance and switching speed. It is seen that this device possesses enhanced drain current, higher transconductance and lower output conductance. The gate-induced drain leakage current for this device has also been investigated. The subthreshold slope of this device is approximately 71 mV/ decade and Ion/Ioff ratio is also high, which leads to its usage for low power and high speed switching applications. The electrical characteristics and short channel effects of this device are also examined for different gate stack materials. It is observed that the device characteristics improve when permittivity of the gate stack is increased. Further, the results acquired using analytical modeling is mapped with the simulated data results to affirm and validate the device model structure. The simulation is implemented using ATLAS-3D device simulator.

Similar content being viewed by others

References

Wong, H-S. Philip, Beyond the conventional MOSFET." In 31st European Solid-State Device Research Conference, pp. 69–72. IEEE, (2001)

H.M. Fahad, M.M. Hussain, High-performance silicon nanotube tunneling FET for ultralow-power logic applications. IEEE Trans. Electron Dev. 60(3), 1034–1039 (2013)

C. Hong, J. Zhou, J. Huang, R. Wang, W. Bai, J.B. Kuo, Y. Chen, A general and transformable model platform for emerging multi-gate MOSFETs. IEEE Electron Dev. Lett. 38(8), 1015–1018 (2017)

M. Kumar, S. Haldar, M. Gupta, R.S. Gupta, Impact of gate material engineering (GME) on analog/RF performance of nanowire Schottky-barrier gate all around (GAA) MOSFET for low power wireless applications: 3D T-CAD simulation. Microelectron. J. 45(11), 1508–1514 (2014)

R.K. Sharma, C.A. Dimitriadis, M. Bucher, A comprehensive analysis of nanoscale single-and multi-gate MOSFETs.". Microelectron. J 52, 66–72 (2016)

Colinge, Jean-Pierre, Abhinav Kranti, Ran Yan, Chi-Woo Lee, Isabelle Ferain, Ran Yu, N. Dehdashti Akhavan, and Pedram Razavi. "Junctionless nanowire transistor (JNT): Properties and design guidelines." Solid-State Electronics 65 (2011): 33–37.

Y. Pratap, R.S. Subhasis Haldar, Gupta, and Mridula Gupta, , Performance evaluation and reliability issues of junctionless CSG MOSFET for RFIC design. IEEE Trans. Dev. Mater. Reliab. 14(1), 418–425 (2014)

T. Holtij, M. Graef, F.M. Hain, A. Kloes, B. Iñíguez, Compact model for short-channel junctionless accumulation mode double gate MOSFETs. IEEE Trans. Electron Dev. 61(2), 288–299 (2013)

J.H. Choi, T.K. Kim, J.M. Moon, Y.G. Yoon, B.W. Hwang, D.H. Kim, S.-H. Lee, Origin of device performance enhancement of junctionless accumulation-mode (JAM) Bulk FinFETs with high-$\kappa $ Gate Spacers. IEEE Electron Dev. Lett. 35(12), 1182–1184 (2014)

N. Trivedi, M. Kumar, S.S. Subhasis Haldar, M.G. Deswal, R.S. Gupta, Analytical modeling of junctionless accumulation mode cylindrical surrounding gate MOSFET (JAM-CSG). Int. J. Num. Model. Electron. Netw. Dev. Fields 29(6), 1036–1043 (2016)

Zeghbroeck, B.V., Principles of semiconductor devices. (2011). http://ecee.colorado.edu/~bart/book

S. Darwin, T.S. Arun, Samuel, A holistic approach on Junctionless dual material double gate (DMDG) MOSFET with high k gate stack for low power digital applications. SILICON 12(2), 393–403 (2020)

S.I. Amin, R.K. Sarin, Charge-plasma based dual-material and gate-stacked architecture of junctionless transistor for enhanced analog performance. Superlatt. Microstruct. 88, 582–590 (2015)

E. Chebaki, F. Djeffal, H. Ferhati, T. Bentrcia, Improved analog/RF performance of double gate junctionless MOSFET using both gate material engineering and drain/source extensions. Superlatt. Microstruct. 92, 80–91 (2016)

A. Sarkar, A.K. Das, S. De, C.K. Sarkar, Effect of gate engineering in double-gate MOSFETs for analog/RF applications. Microelectron. J. 43(11), 873–882 (2012)

Gupta, Sumedha, Neeta Pandey, and R S Gupta, Investigation of dual- material double gate junctionless accumulation-mode cylindrical gate all around (DMDG-JLAM-CGAA) MOSFET with High-k gate stack for low power digital applications. In 2020 IEEE 17th India council international conference (INDICON), IEEE (2020)

ATLAS, Device Simulator (Silvaco International, Santa Clara, 2015)

M. Najmzadeh, D. Bouvet, J.-M. Wladyslaw Grabinski, Sallese, and A. M. Ionescu, , Accumulation-mode gate-all-around Si nanowire nMOSFETs with sub-5 nm cross-section and high uniaxial tensile strain. Solid-state Electron. 74, 114–120 (2012)

J. Xiao-Shi, L. Xi, K. Hyuck-In, L. Jong-Ho, A continuous current model of accumulation mode (junctionless) cylindrical surrounding-gate nanowire MOSFETs. Chin. Phys. Lett. 30(3), 038502 (2013)

N.C. Roy, A. Gupta, S. Rai, Analytical surface potential modeling and simulation of junction-less double gate (JLDG) MOSFET for ultra low-power analog/RF circuits. Microelectron. J. 46(10), 916–922 (2015)

T. Holtij, M. Schwarz, A. Kloes, B. Iniguez, Threshold voltage, and 2D potential modeling within short-channel junctionless DG MOSFETs in subthreshold region. Solid-State Electron. 90, 107–115 (2013)

R. Gautam, R.S. Manoj Saxena, Gupta, and Mridula Gupta, , Two dimensional analytical subthreshold model of nanoscale cylindrical surrounding gate MOSFET including impact of localised charges. J. Comput. Theor. Nanosci. 9(4), 602–610 (2012)

C. Jiang, R. Liang, J. Wang, Xu. Jun, A two-dimensional analytical model for short channel junctionless double-gate MOSFETs. AIP Adv. 5(5), 057122 (2015)

C. Li, Ru. Yiqi Zhuang, Han, and Gang Jin, , Subthreshold behavior models for short-channel junctionless tri-material cylindrical surrounding-gate MOSFET. Microelectron. Reliab. 54(6–7), 1274–1281 (2014)

A. Goel, S. Rewari, S. Verma, R.S. Gupta, Physics-based analytic modeling and simulation of gate-induced drain leakage and linearity assessment in dual-metal junctionless accumulation nano-tube FET (DM-JAM-TFET). Appl. Phys. A 126(5), 1–14 (2020)

A. Gnudi, S. Reggiani, E. Gnani, G. Baccarani, Analysis of threshold voltage variability due to random dopant fluctuations in junctionless FETs. IEEE Electron Dev. Lett. 33(3), 336–338 (2012)

J.P. Duarte, S.-J. Choi, Y.-K. Choi, A full-range drain current model for double-gate junctionless transistors.". IEEE Trans. Electron Dev. 58(12), 4219–4225 (2011)

A. Ahmadivand, B. Gerislioglu, Z. Ramezani, Gated graphene island-enabled tunable charge transfer plasmon terahertz metamodulator. Nanoscale 11(17), 8091–8095 (2019)

Trivedi, Nitin, Manoj Kumar, Mridula Gupta, Subhasis Haldar, S. S. Deswal, and R. S. Gupta, Investigation of analog/RF performance of High-k spacer junctionless accumulation-mode cylindrical gate all around (JLAM-CGAA) MOSFET. In 2016 IEEE Uttar Pradesh Section international conference on electrical, computer and electronics engineering (UPCON), pp. 201–205. IEEE, (2016)

Acknowledgements

Authors convey their humble gratitude toward the Director, Maharaja Agrasen Institute of Technology (MAIT), Delhi for giving the required provisions for performing this work.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Gupta, S., Pandey, N. & Gupta, R.S. Analytical modeling of dual-metal gate stack engineered junctionless accumulation-mode cylindrical surrounding gate (DMGSE-JAM-CSG) MOSFET. Appl. Phys. A 127, 520 (2021). https://doi.org/10.1007/s00339-021-04652-0

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-021-04652-0