Abstract

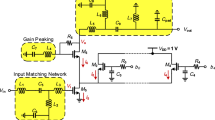

In modern millimeter and sub-millimeter communication systems, particle physics, neutrino astronomy, and for passive applications in radio astronomy or remote atmospheric sensing, the trend is to eliminate analog functional blocks, such as mixers and filters, by converting the signal into the digital domain as early as possible in the processing chain. Therefore, fast analog-to-digital converters (ADC) are needed. Track-and-hold (TAH) circuits can reduce time constraints by holding the analog input value while comparators are sampled, in order to minimize the aperture time errors. This article describes the design of a TAH using the 65 nm CMOS technology from STMicroelectronics. A fully differential architecture has been adopted. The circuit exhibits a −3 dB input bandwidth wider than 8 GHz. At 8 GHz, the maximum sampling frequency, the measured overall power consumption and gain are 178 mW and −2 dB, respectively. The TAH core dissipates around 40 mW. The measured total harmonic distortion (THD) at Nyquist sampling conditions is about −37 dB. The circuit die area is 1.1 mm².

Similar content being viewed by others

References

Baudry, A., Deschans, D., Begueret, J.B., Deval, Y., Fouillat, P., Montignac, G., Gentaz, O., & Torres, M. (2002). Designing and prototyping of 2–4 GHz bandpass SiGe digitizers and associated test equipment for the ALMA project. I, ALMA Memo No. 410. In Proceedings of the 2002 IEEE international conference on electronics. Atacama: ALMA.

Takagi, S. S., Fujii, N., Hashimoto, Y., Sakata, K., & Okada, H. (2004). 4-Gb/s track and hold circuit using parasitic capacitance canceller. In ESSCIRC proceeding of the IEEE (pp. 347–350). New York: IEEE

Shahramian, S., Voinigescu, S.P., & Carusone, A.C. (2006). A 30-GS/sec track and hold amplifier in 0.13-μm CMOS technology. In Proceedings of custom integrated circuit conference (pp. 493–496). San Jose: CICC ‘06.

Halder, S., Gustat, H., & Scheytt, C. (2006). An 8 bit 10 GS/s 2Vpp track and hold amplifier in SiGe BiCMOS technology. In ESSCIRC, proceeding of the IEEE (pp. 416–419). Athens: ESSCIRC.

Acknowledgments

The authors thank STMicroelectronics for providing their 65 nm CMOS technology and for fabricating the circuit.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Mattos, D., Hellmuth, P., Recoquillon, C. et al. Design of a 65 nm CMOS 8 GHz wideband: track-and-hold, for radio astronomy and cosmology applications. Analog Integr Circ Sig Process 73, 779–787 (2012). https://doi.org/10.1007/s10470-012-9915-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-012-9915-7