Abstract

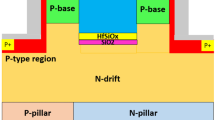

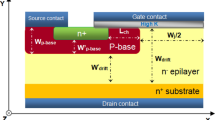

The present paper proposes a novel concept which can successfully reduce threshold voltage and increase switching speed of a conventional MOSFET. The proposed structures have been incorporated with a silicon germanium (SiGe) layer as a channel at the 22 nm technology node. Also, extensive analyses have been done to study the effects of replacing conventional polysilicon by graded dopent profile polysilicon, use of a high-k/silicon dioxide stack as a dielectric with graded dopent profile polysilicon and by using a high-k/silicon dioxide stack as a dielectric with a metal gate. Hafnium dioxide is used as a high-k material. Silvaco Athena and Atlas simulators are used for simulation as well as for finding electrical characteristics of the structures. For all the proposed structures two important parameters are studied in detail, threshold voltage and subthreshold slope. Comparing the three structures, it can be seen that using the high-k/silicon dioxide stack as a dielectric with a metal gate yields the best threshold voltage as well as good subthreshold slope which is directly related to the switching behaviour of the device. The required fabrication aspects of the modelled structures are also elaborated in detail.

Similar content being viewed by others

References

Frank MM (2011) High-k/metal gate innovations enabling continued CMOS scaling. In: 2011 Proceedings of the ESSCIRC (ESSCIRC), pp 50–58. doi:10.1109/ESSCIRC.2011.6044913

Choi C-H, Chidambaram PR, Khamankar R, Machala CF, Yu Z, Dutton RW (2002) Dopant profile and gate geometric effects on polysilicon gate depletion in scaled MOS. In: Electron devices, (IEEE Transactions), vol 49, pp 1227–1231

Marin M (2004) A new method for the channel-length extraction in mosfets with sub-2-nm gate oxide. In: Electron devices, (IEEE Transactions), vol 25, pp 202–204

Yang N (2000) A comparative study of gate direct tunneling and drain leakage currents in n-MOSFETs with sub-2 nm gate oxides. In: Electron devices, (IEEE Transactions), vol 47, pp 1636–1644

Sarkar M (2005) Impact of nonuniform graded dopant profile in polysilicon gate on gate leakage current. IEEE Trans 52:1200–1204

Emerging Research Materials (2009). In: ITRS (International Technology Roadmap for Semiconductors)

Fei M (2012) A two-dimensional threshold voltage analytical model for metal-gate/high-k/SiO2/Si stacked MOSFET. In: Chin. Physics, (IEEE Transactions), vol 21, pp 107306–17

Chau R, Brask J, Datta S (2005) Application of high- gate dielectrics and metal gate electrodes to enable silicon and non-silicon logic nanotechnology. Microelectron Eng 80(0):1–6. 14th biennial Conference on Insulating Films on Semiconductors {INFOS2005}. doi:10.1016/j.mee.2005.04.035

Bhaumik K (1996) Theory and observation of enhanced, high field hole transport in Si 1-xGex quantum well p-MOSFETs. In: Electron Devices, (IEEE Transaction), vol 43, pp 1965–1971

Riml K (2001) Strained Si NMOSFETs for high performance CMOS technology. In: VLSI Technology (IEEE), pp 59–60

Royer CL (2012) Interfaces and performance: What future for nanoscale ge and sige based cmos. Microelectron Eng 88:1541–1548

Song YJ (2004) Dc and rf characteristics of rpcvd grown modulation doped si0.8ge0.2 pmosfets. Solid State Electron 48:315–320

Thompsonl S (2002) A 90nm logic technology featuring 50 nm strained silicon channel transistors, 7 layers of Cu interconnects, low-k ILD, and 1 m2 SRAM cell. In: IEDM (IEEE), pp 61–64

Yousif M (2001) Recent critical issues in Si/Si1-xGex/Si heterostructure FET devices. In: Solid State Electronics, vol 45. Elsevier, pp 1931–1937

Bhattacharyya AB (2009) Compact MOSFET Models for VLSI Design. Wiley, New York. ISBN 9780470823422

Emerging Research Devices (2009). In: ITRS (International Technology Roadmap for Semiconductors)

Athena user’s manual (2012) SILVACO TCAD

Atlas user’s manual (2012) SILVACO TCAD

Godoy A, Gamiz F (2001) A simple subthreshold swing model for short channel {MOSFETs}. Solid-State Electron 45(3):391–397. doi:10.1016/S0038-1101(01)00060-0

Maheran AHA, Menon PS, Ahmad I, Yusoff Z (2013) Threshold voltage optimization in a 22nm High-k/Salicide PMOS device. In: 2013 IEEE Regional Symposium on Micro and Nanoelectronics (RSM), pp 126–129. doi:10.1109/RSM.2013.6706489

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Mahajan, R., Gautam, D.K. Analysis of a SiGe MOSFET at 22nm. Silicon 8, 505–511 (2016). https://doi.org/10.1007/s12633-016-9407-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-016-9407-y