Abstract

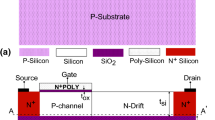

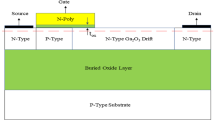

A novel structure of a silicon carbide (SiC) double-trench metal oxide semiconductor field-effect transistor (DTMOSFET) is proposed using a hafnium silicate (HfSiOx ) dielectric combined with PN pillars. Moreover, it has been characterized using Atlas TCAD Silvaco 2D simulations, and offers a very high breakdown voltage of 4879 V, which is due to the PN pillars under the N-drift layer altering the electric field distribution and HfSiOx dielectric that diminishes the impact ionization. The proposed DTMOSFET achieves a transconductance (gm) and drain current (ID) of 7 mA/mm and 780 µS/mm, respectively. In addition, the simulated results show the cut-off frequency, fT = 1.28 GHz, and maximum frequency, fmax = 10.5 GHz. In addition, the peak electric field observed near the gate edge is 0.93 MV/cm. Moreover, the proposed DTPNH-MOSFET shows 11% improvement in breakdown voltage when compared to the breakdown voltage of conventional DTMOSFET. Therefore, the DTPNH-MOSFET shows a superior performance over other SiC MOSFETs and is a suitable device for future high-power electronics.

Similar content being viewed by others

References

S. Sreejith, J. Ajayan, S.B. Devasenapati, B. Sivasankari, and S. Tayal, A Critical review on reliability and short circuit robustness of silicon carbide power MOSFETs. SILICON 15, 623 (2023).

Y. Wang, G. Han, W. Xu, T. You, H. Hu, Y. Liu, and Y. Hao, Recessed-gate Ga2O3-on-SiC MOSFETs demonstrating a stable power figure of merit of 100 mW/cm2 up to 200 °C. IEEE Trans. Elect. Dev. 69, 1945 (2022).

R.P. Ramamurthy, N. Islam, M. Sampath, D.T. Morisette, and J.A. Cooper, The tri-gate MOSFET: a new vertical power transistor in 4H-SiC. IEEE Elect. Dev. Lett. 42, 90 (2020).

H. Yang, S. Hu, S. Ran, J.A. Wang, and T. Liu, Simulative researching of a 1200V SiC trench MOSFET with an enhanced vertical RESURF effect. IEEE J. Elect. Dev. Soc. 8, 1335 (2020).

Y. Kagawa, N. Fujiwara, K. Sugawara, R. Tanaka, Y. Fukui, Y. Yamamoto, and S. Yamakawa, 4H-SiC trench MOSFET with bottom oxide protection. Mater. Sci. Forum 778, 919 (2014).

A. Agarwal and B.J. Baliga, Implant straggle impact on 1.2 kV SiC power MOSFET static and dynamic parameters. IEEE J. Elect. Dev. Soc. 10, 245 (2022).

A. Niwa, T. Imazawa, R. Kojima, M. Yamamoto, T. Sasaya, T. Isobe, and H. Tadano, A dead-time-controlled gate driver using current-sense FET integrated in SiC MOSFET. IEEE Trans. Pow. Elect. 33(4), 3258 (2017).

H.C. Luo, L.M. Wang, S.G. Wang, C.J. Tan, K. Zheng, G.Q. Zhang, and X.P. Chen, Investigations of SiC VDMOSFET with floating island structure based on TCAD. IEEE Trans. Elect. Dev. 66(5), 2295 (2019).

K. Han, B.J. Baliga, and W. Sung, Split-gate 1.2-kV 4H-SiC MOSFET: analysis and experimental validation. IEEE Elect. Dev. Let. 38(10), 1437 (2017).

K. Han, B.J. Baliga, and W. Sung, A novel 1.2 kV 4H-SiC buffered-gate (BG) MOSFET: analysis and experimental results. IEEE Elect. Dev. Let. 39, 248 (2017).

Y.L. Zheng, W.M. Tang, T. Chau, J.K. Sin, and P.T. Lai, Simulation study of 4H-SiC high-k pillar MOSFET with integrated Schottky barrier diode. IEEE J. Elect. Dev. Soc. 9, 951 (2021).

S. Liu, X. Cheng, L. Zheng, T. Sledziewski, T. Erlbacher, L. Sheng, and Y. Yu, Impact of the transition region between active area and edge termination on electrical performance of SiC MOSFET. Sol-Stat Elect. 171, 107 (2020).

L. Wang, Y. Jia, X. Zhou, Y. Zhao, D. Hu, Y. Wu, and Z. Deng, Degradation of 650 V SiC double-trench MOSFETs under repetitive overcurrent switching stress. Microelect. Rel. 133, 114 (2022).

L. Zhang, Y. Liu, J. Fang, and Y. Liu, Investigation of a 4H-SiC Trench MOSFET with back-side super junction. Micromach 13, 177 (2022).

A. Siddiqui, R.Y. Khosa, and M. Usman, High-k dielectrics for 4H-silicon carbide: present status and future perspectives. J. Mater. Chem. 15, 5055 (2021).

L. Liang, L. Wei, L. Sichao, L. Xuefei, and W. Yanqing, Interface properties study on SiC MOS with high-k hafnium silicate gate dielectric. AIP Adv. 8, 12 (2018).

Y. Liu, W. Yang, H. Feng, Y. Onozawa, S. Wakimoto, N. Fujishima, J.K. Sin, Trench field plate engineering for high efficient edge termination of 1200 V-class SiC devices. Intern Symp on Pow Semicond Dev, 143-146. (2019)

Y. Zhao, H. Niwa, and T. Kimoto, Impact ionization coefficients of 4H-SiC in a wide temperature range. Jpn. J. Appl. Phys. 58(1), 018001 (2018). https://doi.org/10.7567/1347-4065/aae985.

Y.Z. Cheng, Y. Wang, X. Wu, and F. Cao, 4H-SiC UMOSFET with an electric field modulation region below P-body. IEEE Trans. Elect. Dev. 67, 3298 (2020).

J.C. Guo and C.S. Chang, SiC strained nMOSFETs with enhanced high-frequency performance and impact on flicker noise and random telegraph noise. IEEE Trans. Microw. Theor. Tech. 68, 2259 (2020).

A.S. Augustine Fletcher, D. Nirmal, J. Ajayan, L. Arivazhagan, K. Hamza, and P. Murugapandiyan, 60 GHz double deck T-Gate AlN/GaN/AlGaN HEMT for V-Band Satellites. SILICON 20, 1 (2021).

X. Li, Z. Guangyong, and L. Xinyu, The stability, optical properties and solar-thermal conversion performance of SiC-MWCNTs hybrid nanofluids for the direct absorption solar collector (DASC) application. Sol. Ener. Mater. Sol. Cel. 206, 110 (2020).

A. Hussein, C. Alberto, W. Pat, K. Christian, (2016) Performance benchmark of Si IGBTs vs. SiC MOSFETs in small-scale wind energy conversion systems. IEEE Inter. Pow. Elect. Mot. Cont. Conf. 963-968.

B. Narayanasamy, S. Arvind, L. Fang, and C. Cai, Reflected wave phenomenon in SiC motor drives: consequences, boundaries, and mitigation. IEEE Trans. Pow. Elect. 35, 10629 (2020).

B. Sarlioglu (2019) Automotive power electronics: Current status and future trends. Inter. Conf. Optim. Elect. Elect. Equip. 1-2.

D. Dong, M. Agamy, J.Z. Bebic, Q. Chen, and G. Mandrusiak, A modular SiC high-frequency solid-state transformer for medium-voltage applications: design, implementation, and testing. IEEE J. Emer. Sel. Top. Pow. Elect. 7, 768 (2019).

Acknowledgments

The authors acknowledge the Centre for Research in Semiconductor Devices, Department of Electronics and Communication Engineering, Karunya Institute of Technology and Sciences, Coimbatore, India for providing all facilities to carry out this research work.

Funding

No funding for this research

Author information

Authors and Affiliations

Contributions

ASA Fletcher-TCAD Simulation and paper writing. AF TCAD Simulation PM Paper editing and English correction. JA Idea and concept. DN Idea and concept.

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that there is no conflict of interest reported in this paper.

Ethics Approval

All procedures performed in studies were in accordance with the ethical standards of the institutional and/or national research committee and with the comparable ethical standards.

Consent for Publication

Authors give consent for the publication of the Submitted Research article in Silicon.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Fletcher, A.S.A., Franklin, S.A., Murugapandiyan, P. et al. 4.87 kV SiC MOSFET Using HfSiOx/SiO2 Gate Dielectrics Combined with PN Pillars. J. Electron. Mater. 53, 2601–2608 (2024). https://doi.org/10.1007/s11664-024-11014-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-024-11014-y