Abstract

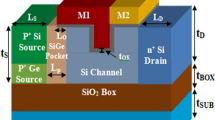

Electron wavefunctions are switched spatially from one quantum well to another by varying the gate voltage V g in spatial wavefunction-switched (SWS) field-effect transistors (FETs), which comprise two or more coupled quantum wells serving as the transport channel. This is shown for Si/SiGe and InGaAs/AlInAs quantum well systems. The presence of charge in a particular well or channel is used to encode four states 00, 01, 10, 11. This unique property is used for two-bit processing, resulting in compact two-bit static random-access memory devices. Experimental data including capacitance–voltage peaks in Si and InGaAs multiple quantum well SWS-FETs has verified the SWS phenomenon. Replacing quantum wells by an array of cladded quantum dots, forming a quantum dot superlattice (QDSL) layer, enhances the contrast and noise margin in SWS-FETs. This paper reports I–V and C–V characteristics for a fabricated twin-drain SWS-quantum dot channel (QDC) FET comprising four layers of self-assembled SiO x -Si quantum dots. SWS-QDC-FETs are shown to be scalable to ∼9 nm, and comprise four layers of cladded quantum dots with an array of 3 × 3 forming the channel.

Similar content being viewed by others

References

F.C. Jain, B. Miller, E. Suarez, P.-Y. Chan, S. Karmakar, F. Al-Amoody, M. Gogna, J. Chandy, and E. Heller, J. Electronic Materials 40, 1717 (2011).

F. Jain and E. Heller, US Patent# 8,294,137 (23 October 2012).

F.C. Jain, J. Chandy, B. Miller, E.-S. Hasaneen, and E. Heller, Int. J. High Speed Electron. Syst. 20, 641 (2011).

P. Gogna, E. Suarez, M. Lingalugari, J. Chandy, E. Heller, E.-S. Hasaneen, and F.C. Jain, J. Electron. Mater. 42, 3337 (2013).

P. Gogna, M. Lingalugari, J. Chandy, F.C. Jain, E. Heller, and E.-S. Hasaneen, Efficient multi-bit SRAMs using spatial wavefunction switched (SWS)-FETs, IEEE conference proceedings of Lester Eastman Conference on High Performance Devices (LEC) (Providence, RI: Brown University, 2012).

E.K. Heller, S.K. Islam, G. Zhao, and F.C. Jain, Solid-State Electron. 42, 901 (1999).

T. Kerkhoven, A.T. Galick, U. Ravaioli, J.H. Arends, and Y. Saad, J. Appl. Phys. 68, 3461 (1990).

T. Kerkhoven, M.W. Raschke, and U. Ravaioli, J. Appl. Phys. 74, 1199 (1993).

K. Uchida, M. Saitoh, and S. Kobayashi, Carrier transport and stress engineering in advanced nanoscale transistors from (100) and transistors to carbon nanotube FETs and beyond, IEDM (2008), pp. 569–572.

T. Tezuka, E. Toyoda, S. Nakaharai, T. Irisawa, N. Hirashita, Y. Moriyama, N. Sugiyama, N. Taoka, Y. Yamashita, O. Kiso, M. Harada, T. Yamamoto, and S. Takagi, Observation of mobility enhancement in strained Si and SiGe tri-gate MOSFETs with multi-nanowire channels trimmed by hydrogen thermal etching, IEDM (2007), pp. 887–890.

J.-H. Park, M. Tada, D. Kuzum, P. Kapur, H.-Y. Yu, H.S. Philip Wong, and K.C. Saraswat, Low temperature (<=380°C) and high performance Ge CMOS Technology with novel source/drain by metal-induced dopants activation and high—K/metal gate stack for monolithic 3D integration, IEDM (2008) pp. 389–392.

J. Lin, S. Lee, H.-J. Oh, W. Yang, G.Q. Lo, D.L. Kwomg, and D.Z. Chi, Plasma PH3-passivated high mobility inversion InGaAs MOSFET fabricated with self-aligned gate-first process and HfO2/TaN gate stack, IEDM (2008) pp. 401–404.

L. Klein, D. Savage, and M. Eriksson, Appl. Phys. Lett. 90, 033103 (2007).

N. Shaji, C. Simmons, M. Thalakulam, L. Klein, H. Qin, H. Luo, D. Savage, M. Lagally, A. Rimberg, R. Joynt, M. Friesen, R.H. Blick, S.N. Coppersmith, and M.A. Eriksson, Nat. Phys. 4, 540 (2008).

A. Franklin, M. Luisier, S.-J. Han, G. Tulevski, C. Breslin, L. Gignac, M. Lundstrom, and W. Haensch, Nano Lett. 12, 758 (2012).

A.D. Franklin, G.S. Tulevski, S.-J. Han, D. Shahrjerdi, Q. Cao, Hong-Yu Chen, H.-S. Philip Wong, and W. Haensch, ACS Nano 6, 1109 (2012).

M. Shulaker, G. Hills, N. Patil, H. Wei, H.-Y. Chen, H.-S. Phillip Wong, and S. Mitra, Nature 501, 526 (2013).

F. Jain, S. Karmakar, P.-Y. Chan, E. Suarez, M. Gogna, J. Chandy, and E. Heller, J. Electronic Materials 41, 2775 (2012).

S.M. Sze, Physics of Semiconductor Devices, 2nd ed. (New York: Wiley, 1981), p. 445.

C.-W. Jiang and M.A. Green, J. Appl. Phys. 99, 114902 (2006).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Jain, F., Chan, PY., Lingalugari, M. et al. Si and InGaAs Spatial Wavefunction-Switched (SWS) FETs with II–VI Gate Insulators: An Approach to the Design and Integration of Two-Bit SRAMs and Binary CMOS Logic. J. Electron. Mater. 44, 3108–3115 (2015). https://doi.org/10.1007/s11664-015-3827-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-015-3827-0