Abstract

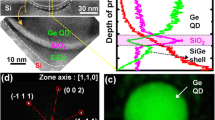

This paper presents the successful use of ZnS/ZnMgS and other II–VI layers (lattice-matched or pseudomorphic) as high-k gate dielectrics in the fabrication of quantum dot (QD) gate Si field-effect transistors (FETs) and nonvolatile memory structures. Quantum dot gate FETs and nonvolatile memories have been fabricated in two basic configurations: (1) monodispersed cladded Ge nanocrystals (e.g., GeO x -cladded-Ge quantum dots) site-specifically self-assembled over the lattice-matched ZnMgS gate insulator in the channel region, and (2) ZnTe-ZnMgTe quantum dots formed by self-organization, using metalorganic chemical vapor-phase deposition (MOCVD), on ZnS-ZnMgS gate insulator layers grown epitaxially on Si substrates. Self-assembled GeO x -cladded Ge QD gate FETs, exhibiting three-state behavior, are also described. Preliminary results on InGaAs-on-InP FETs, using ZnMgSeTe/ZnSe gate insulator layers, are presented.

Similar content being viewed by others

References

J. Chandy and F. Jain, Proc. of International Symposium on Multiple Valued Logic, May, Dallas, TX (2008), pp. 186–190.

F.C. Jain, E. Heller, S. Karmakar, and J. Chandy, Proc. International Semiconductor Device Research Symposium, Dec. 12–15, College Park, MD (2007)

S. Tiwari, F. Rana, K. Chan, H, Hanafi, W. Chan, and D. Buchanan, IEDM Proc., December (1995), pp. 521–525.

R. Velampati and F.C. Jain, NSTI Nanotech , Santa Clara, CA, May 20–24 (2007).

F. Jain and F. Papadimitrakopoulos, Site-specific nanoparticle self-assembly, US Patent 7,368,370 (2008)

X.G. Zhang, P. Li, D.W. Parent, G. Zhao, J.E. Ayers, and F.C. Jain, J. Electron. Mater, 28, 553 (1999) doi:10.1007/s11664-999-0111-1

J.F. Ocampo, E.N. Suarez, F.Jain, and J.E. Ayers, J. Electron. Mater, 37, 1035 (2008) doi:10.1007/s11664-008-0476-6

X.G. Zhang, S. Kalisetty, J. Robinson, G. Zhao, D.W. Parent, J.E. Ayers, and F.C. Jain, J. Electron. Mater, 26, 697 (1997) doi:10.1007/s11664-997-0218-1

M. Geller, T. Marent, and T. Nowozin, Physica E: Low-Dimensional Systems and Nanostructures, 40, 1811 (2008) doi:10.1016/j.physe.2007.09.108

E-S. Hasaneen, E. Heller, R. Bansal, and F. Jain, Solid-State Electronics, 48, 2055 (2004). doi:10.1016/j.sse.2004.05.073

B. Yarlagadda, A. Rodriguez, P. Li, R. Velampati, J.F. Ocampo, E.N. Suarez, P.B. Rago, D. Shah, J.E. Ayers, and F.C,. Jain, Appl. Phys Lett, 92, 202103 (2008). doi:10.1063/1.2936078

Acknowledgements

This work is supported in part by ONR Contracts N00014-02-1-0883 and N00014-06-1-0016, and NSF Grants EEC 0407279 (NUE) and ECS 0622068. Discussions with Dr. D. Purdy (ONR) and Dr. R. Khosla (NSF), and technical assistance in processing by Dr. R. Velampati (Intel) and Dr. A. Rodriguez (Intel) are gratefully acknowledged.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Jain, F.C., Suarez, E., Gogna, M. et al. Novel Quantum Dot Gate FETs and Nonvolatile Memories Using Lattice-Matched II–VI Gate Insulators. J. Electron. Mater. 38, 1574–1578 (2009). https://doi.org/10.1007/s11664-009-0755-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-009-0755-x