Abstract

The paper discusses a VCO belonging to the class of Distributed-VCOs (DVCOs) designed for wide tuning range operations. The trade-off between wide bandwidth and phase noise is central to the proposed design and the paper covers the DVCO topology and discusses its operations in detail, starting by the general conditions of oscillation and covering the applied tuning techniques. In particular the paper reports a description of the so called “switched-cells tuning technique”. The design of a fully integrated DVCO is reported. It is based on the “switched-cells tuning technique” and provides the following measured tuning ranges over four sub-bands: 219 MHz around 900, 291 MHz around 1.5 GHz, 392 MHz around 1.8 GHz and 199 MHz around 2.4 GHz. The DVCO performances are discussed and compared with other similar implementation reported in the recent literature showing the potentialities of the proposed approach. According to the reported theory, the results show the applicability of the proposed Distributed VCOs for wide bandwidth applications.

Similar content being viewed by others

1 Introduction

Multi-band, multi-standard requirements dominate modern wireless telecommunications most of all in advanced systems based on the paradigm of Software Defined Radios (SDR) [1] both at the lower GHz and higher GHz bands [2, 3]. In these implementations the VCO design faces a difficult trade-off between wide tuning range and phase noise.

Different techniques are possible to design a wideband VCO: transformer based VCOs [3], frequency translation (division, multiplication, injection locking) [4], multiple VCOs [5], switched inductors based VCOs [6], multiple inductors based VCOs [7], inductor reuse based VCOs [8]. These tuning techniques are commonly adopted at low frequencies and there is a great interest in adopting similar approaches at higher frequencies.

DVCOs have been introduced to obtain a wide tuning range while providing good phase noise as an alternative to ring oscillators, which usually provide wide tuning range and poor phase noise, and LC-VCOs, which provide better phase noise over smaller bands. A DVCO is based on a Distributed Amplifier (DA) operating in the reverse gain mode [9–12], or in the forward gain mode [13–20]. DVCOs are also known as travelling wave VCOs which belong to the class of wave-based oscillators wherein there are the rotary-travelling wave VCOs (also called closed-loop Distributed VCOs) and standing-wave VCOs [21].

Theoretically, the DVCO could benefit of the wide bandwidth of the amplifier and, avoiding passive components, it allows to design fully integrated VCOs which operate at higher frequencies when compared to the integrated LC-VCOs for a given technology. The literature proposes several examples of DVCOs operating in the forward gain mode [13–20], but none of these solutions exploits completely the potentiality of such class of oscillators in terms of wide tuning range.

The topologies proposed in [22] and [23] aim to take advantage of the wide bandwidth of the DA to design a wide tuning range VCO. The approach proposed in [23], is based on the idea to separate the amplification from the phase shifting. In this way the DA can play the role of a “loop-gain tank”. Therefore, the amplifier potentially provides the oscillation sustainment over a very wide bandwidth while giving an uniform phase noise, output power and harmonics suppression. A key aspect of this topology is how the phase shifting is implemented to exploit the DA potentialities.

Section 2 discusses the operation of this type of DVCO and the general condition of oscillations. Section 3 introduces a study on the implementation of the phase shifting techniques for wideband applications. To validate the proposed “switched cell tuning technique” a fully integrated DVCO prototype operating at low GHz has been implemented and its performances are reported in Sect. 4. The potentialities of the proposed approach are evidenced in this section comparing the prototype measurements with the literature.

2 Distributed VCO

In the classical DVCO the DA amplifies and simultaneously assures the right phase shift between the gate (base) and the drain (collector) transmission lines, so that the Barkahusen criteria is satisfied. Assuming equal propagation properties for both transmission lines into the DA, the oscillation frequency, f o, is [13]:

where v phase is the phase velocity along the transmission lines, l is the length of the single cell, n is the number of transistors, L and C are the inductance and the capacitance per unit length and f C is the cut-off frequency of the loaded transmission lines. According to (1), there are two possibilities for achieving the tuning: to change the phase velocity and/or the effective length of the transmission lines.

In practical implementations, the number of transistors is limited by the losses in the DA, and it does not exceed 3–4. Therefore, the DA operates at a frequency close to f C introducing some drawbacks: the characteristic impedance of transmission lines strongly varies with the frequency; the attenuation of the transmission lines, due to impedance mismatches, increases and the noise figure of the DA increases as well.

To overcome these limits, the basic idea is to split the DVCO into two blocks: the DA followed by a Synthetic Line (SL) (Fig. 1) [23]. This allows to design a DVCO with a wide tuning range while providing small variations of the output power, reduced phase noise and low harmonic generation over the entire band [24].

In this topology, the DA must introduce enough inverting gain to sustain the oscillation over a wide bandwidth, according to its distributed nature, regardless of the required phase shift. Therefore, the transmissions line cut-off frequency in the amplifier, f C,amp, can be set far enough from the tuning band upper limit.

The phase shift required for the oscillation is controlled by the SL which is, in its basic version, an m-cells periodic structure. The electrical behavior of the SL depends on the topology of its basic cell.

The tuning obtained by varying the electrical parameters of the SL does not affect the in phase power-sum at each tap point on the drain (collector) line of the DA, allowing a greater frequency variation without the switching off of the oscillation. An additional degree of freedom is given by the choice of the SL cell topology, depending on the circuit requirements.

The advantage of this approach, first of all, is that the characteristic impedance, Z0, of the DA is almost constant all over the tuning band. At the same time, a flat behavior is ensured over the entire tuning band by the DA itself along with an optimum noise figure at its center band which translates in better phase noise performances. The uniformity of the performances in terms of output power, phase noise and harmonics suppression all over the wide tuning range, achievable by using this topology is very important for wide bandwidth VCOs.

Similar techniques, based on the use of two blocks, govern the operations of other oscillators for achieving a wide tuning range. Some examples are those based on uniform or multi-section transmission lines described in [25] and the ring oscillator presented in [26] where the LC delay lines are used to reduce the errors in the free-running frequency caused by process variations.

2.1 The general condition of oscillation

It is possible to obtain the general conditions of oscillation generalizing the equation derived in [13]. To this purpose, it is useful to calculate the open loop gain given by the product of the individual gain in the cascade of the DA and the SL as shown in Fig. 2. The DA contains n transistors and two transmission lines. In the following we assume a MOS implementation but similar consideration can be made for the bipolar case. The forward wave on the gate line is amplified by the transistors and absorbed by the termination matched to characteristics impedance of the gate line, Zg. If the incident wave on the drain line travels with the same phase velocity, then each gain stage adds power in phase to the signal at each tap point on the drain line, the backward wave on the drain line is absorbed by the termination matched to characteristics impedance of the drain line, Zd. Assuming that the spacing between the transistors is smaller than half wavelength then their input and output impedances can be considered distributed and added to the parameters per unit length of the transmission lines.

The DA gain can be calculated from the circuit reported in Fig. 3.

The impedance, Zk, seen at kth tap of the drain line is Zd//ZSLK, where Zd is the characteristics impedance of the drain line and ZSLK is the input impedance of the SL transformed along the path to the kth tap point along the drain transmission line:

where ΓSL is the reflection coefficient at the input of the SL and γd is the complex propagation constant of the loaded drain line. The voltage at the kth tap point is:

where Gm is the large-signal transconductance of each transistor. The voltage at the kth tap point of the gate line is related to the gate line segment l g and to the complex propagation constant of the loaded gate line γg:

where vin is the voltage at the input node of the DA. The voltage, vo, across the load ZSL can be determined by using the superposition method. The contribute to vo due to the kth transistor is:

By substituting in (5), (3) and (4), it is possible to achieve the following expression:

Summing all the contributions, vo is expressed by:

Using the identity, an−bn = (a−b)(an−1 + an−2b + ··· + bn−1), the previous equation becomes:

Finally, the DA gain is expressed by:

In the case of γglg = γdld = γl, the voltage gain is equal to:

In the previous equations it has been considered the case of a matched load, Zd, connected to the drain line which absorbs the reflected wave. By using the previous approach, it is easy to generalize the expression of the DA gain when a generic load impedance is connected to the drain line.

The gain of the second stage is the ratio between the voltage, vo, calculated before, and vr (Fig. 2). The SL is a cascade of m identical cells, and can be modeled as a transmission line. By using the relation between the values of voltages along a transmission line, it is possible to express as follows the gain of the second stage:

where ΓL is the reflection coefficient at the output section of the SL while γsl is the complex propagation constant of the SL; the expression of γsl depends on the type of cell into the SL.

The open loop gain is equal to ADA × ASL. In the case of γglg = γdld = γl, the open loop gain is:

Finally the general conditions of oscillation is expressed by the following equation:

This expression sets both the amplitude and the frequency of oscillation. In the case of γglg = γdld = γl, the previous equation becomes:

3 The tuning techniques

The most common techniques used for the classical DVCO operations are inherent-varactor and delay-balanced current steering tuning [13]. Other techniques are the delay variation by positive feedback tuning technique [15] and the current starving method [20]. The inherent-varactor tuning allows to vary the oscillating frequency by modifying the phase velocities along the gate (base) and drain (collector) lines in the DA. This change is achieved by controlling the DC bias voltage of the active components of the DA which in turn varies the capacitances along the lines, thus inducing the desired phase-shift variation. This solution is well suited for integration, because it does not require external components. On the other hand, the variations induced in the transistors bias point are unacceptable when a wide tuning range is required, because they usually bring to the damping of the oscillation. Moreover, the capacitances in the two SLs do not vary with the same rate when the DC voltage varies, thus, generating a difference in phase velocity which does not allow the in-phase sum of the contributions along the gain line. This condition results in strong amplitude variations of the oscillation in the tuning band.

The delay-balanced current steering tuning technique varies the effective basic cell line length using the current-steering technique. Usually this solution is used to finely tune the oscillation as it offers less tuning span than the inherent-varactor technique.

As previously discussed, in the DVCO based on the splitting in two blocks: the DA followed by a SL, the DA acts as a “loop-gain tank” and has the capability to sustain the oscillation over a wide bandwidth. Given a set of specs for the oscillator, the SL has to be designed in order to take advantage of the DA operations. The weak interaction between the tuning controlled by the SL and the gain inserted by the DA gives the possibility to implement new tuning schemes.

A possible arrangement for the SL is described in [27] using switched-capacitors banks. These are commonly used in LC-VCOs design to achieve a coarse variation of the capacitance, C, which governs the oscillation frequency. This variation, ΔC, is usually controlled by exploiting a digital tuning scheme.

A second solution to design the SL is based on the use of the “switched-cells tuning technique” proposed in [28] which seems to be a suitable way to implement a SL that guarantees wideband operations.

These two tuning techniques add to the basic topology described in [23] and [24] the multi-band capability, extending in this way the potentialities of this kind of DVCO. Comparing these two solutions, the technique introduced in [28] and used in this work, seems to be the better way for fully exploiting the wideband DA. In fact the switched-cell tuning technique allows a weaker interaction between the SL and the DA than the switched-capacitors banks technique. Moreover the use of the switched bank of varactors, described in Sect. 4, allows to overcome some limits of the DVCO reported in [28] making this topology suitable for practical implementations of wideband DVCO.

3.1 The switched-cells tuning technique

The frequency of oscillation depends on the length of the path that the signal has to undergo inside the loop, the longer is the path the lower is the frequency that fulfills the Barkhausen criterion. The key point is to implement a suitable tuning technique that is able to modify the path without leading to the switching off of the oscillation. In order to achieve this result, the change should not introduce a significant variation into the operation of the DVCO both in the first and in the second block. In particular, the impedance changes when the phase velocity along the SL varies performing the tuning in each sub-band. Such tuning, thus, must be as insensitive as possible to the load impedance variations presented at the input port of the SL to the DA in order to not modify the operation of the DA itself. The “switched-cells tuning technique” is able to meet this requirement. Moreover the loss in the SL should remain constant after the change in the length of the path. Actually, this is harder to achieve due to the fact that the losses increase inherently extending the path. Operating only on the SL it is not possible to solve this problem and then it is necessary to take into account the increased losses and compensate them with the gain of the DA.

The “switched-cells tuning technique” introduced in [28] is based on the simple idea of modifying the number of cells in the signal path into the SL by using a digital control scheme to implement the coarse jumps among the sub-bands of the multi-band DVCO. The periodic m-cells structure introduces approximately a phase shift, equal to m times the unitary phase shift, φsc, the higher is the number of cells the more this approximation is correct. In practical implementations the loading that each cells has at its ports need to be properly taken into account [29]. Assuming the use of the same DA with three different periodic structures using the same basic cell but with different cell numbers m1, m2, m3 with m1 < m2 < m3, since the oscillation frequency is determined by the phase shift equal to 360° along the loop, the corresponding three DVCOs oscillate at different frequencies respecting the following relation: fosc1 > fosc2 > fosc2 .

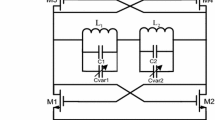

Two implementations are possible (Fig. 4). In the first one, the necessary phase shift is introduced by choosing the right branch (Fig. 4(a)). In the second one, the blocks are arranged in a cascaded structure (Fig. 4(b)). The number of different paths corresponds to the number of multi-bands of synthesis. In both the configurations depicted in Fig. 4, there are three available different lengths of the signal path.

An important difference between these two configurations is the fact that in the parallel topology the cells number in each branch is equal to the number of cells necessary for the wanted band of synthesis associated with such branch. In the cascade topology the number of cells inserted into the path is the sum of the number of cells inside the blocks activated by the SPDTs. For a given design adopting the same cell topology, the parallel configuration has a higher number of cells than the cascade one. It represents a disadvantage in the case of an integrated implementation of the proposed topology in terms of area used on chip by the second block. On the other hand in the cascade topology the loading made by each block on the others is a design key point. In the parallel topology the matching is considerably relaxed because each branch is inserted in the loop separately. In both the solutions an important key point is to take into account the role of the parasitic introduced by the switches. Let N be the number of desired sub-bands, in the parallel architecture the main problem introduced by the switches are the N-1 parasitic off-capacitances which represent a not negligible load at the edges of the synthetic line. With a π-cell topology it is easier to absorb these parasitic into the parameters of the line. For the cascade architecture the parasitic capacitive loading is smaller and the main problem are the increased and variable losses introduced by the switches depending on the number of switches in the “on state”.

Therefore the cascade architecture is the better solution primarily in terms of area consumption, while the parallel topology simplifies the matching design. The fine tuning inside each sub-band is made by varying the phase velocity along the inserted cells into the loop using the varactors in each cell.

3.2 Some considerations on the design

The choice of the single cell topology and the bias point are the main key aspects affecting the DVCO performances.

3.2.1 Single cell topology

The SL mentioned so far, refers to the second block of the DVCO. Actually also the two transmission lines of the DA can be implemented as SLs. Specially in this case, the choice of the better topology of the elementary cell in an RFIC implementations becomes an important design point. The simpler topologies are the T cell and π-cell. Considering the electrical equivalent model of an integrated inductor, the π-cell allows to have simultaneously two advantages: to reduce the number of inductors and to facilitate the matching. While the first advantage is an intrinsic feature of this topology, the second advantage comes from the electrical equivalent model of an integrated inductor. Indeed, it is a π-cell, then, the parasitic elements can be absorbed completely into the basic cell components that constituted the SL, in the same way used to absorb the input and output impedances of the transistors. Differently, in the case of T-cell, the parasitic capacitances at the edges of the SL cannot be absorbed. For these reasons it is possible, by using π-cells, to obtain more predictable transmission lines.

3.2.2 Bias point in the DA

Another design issue is the choice of the best bias point that reduces the harmonics of the generated signal inside the DA. Unlike classical DVCO, there is not filtering inside the DA itself, the filtering which reduces the harmonics is introduced by the SL. Although the output of the DVCO is a clean waveform, it is important to choose a proper bias point in order to stabilize the oscillation. The phase shift introduced by the SL is set by modifying the value of the phase velocity along this line. This change varies the cutoff frequency, f cSL, of the line as well. Then, there is a direct relation between the filtering performed by the SL and the phase shift needed for the oscillation. The greater is the phase shift introduced by the SL, the smaller is the cutoff frequency and the higher is the filtering. For this reason the filtering is theoretical slightly more effective for frequencies of oscillation near the lower edge of the range of synthesis.

4 Measurements and results

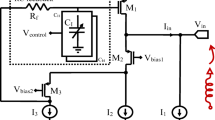

The fully integrated DVCO has been designed and tested using a low-cost 0.35 µm SiGe technology. The prototype comprises the DA, the SL, the output buffer and a decoder used for managing the coarse tuning. The size of the final layout is 3.6 × 3.2 mm2, the micro photo of the chip is reported in Fig. 5. It absorbs 17.6 mA from 3.3 V. The DVCO core uses 9.6 mA, the remaining current is mainly absorbed by the output buffer. The prototype has been designed for oscillating in four different bands. The first band is centered around 900 MHz, the second one around 1.5 GHz, the third one around 1.8 GHz and the last one around 2.4 GHz.

Inside the DA, the π-cell topology has been used to reduce the number of inductors. To separate the bias network from the signal path, MIM (Metal–Insulator–Metal) capacitances have been used instead of poly–poly capacitances not only for the higher Q factor but primarily for the achievable big reduction of the bottom plate-well/substrate parasitic capacitance. This latter has the same unwanted effect of the parasitic components of the inductors and it can lead to a reduction of the band of synthesis.

The switched-cells structure used to design the SL is the parallel configuration of Fig. 4(a) with four branches each one governing one of the four wanted bands. This implementation uses more area than the cascade topology but it simplifies the matching design and represents a simpler way to test this tuning scheme.

The device has been designed and simulated by using Cadence and the simulated performances in the four bands are summarized in Table 1. Simulated phase noise and harmonics suppression are good and uniform along the tuning ranges. The post-layout simulations provide optimum results in terms of tuning range confirming the theory.

The specs adopted for the design define quite wide sub-bands and the use of abrupt varactors in each cell of the SL allows to meet the requirements. Actually the process variations could introduce a sensible dc offset which, in turn, would shift the effective tuning characteristic C(V) provided by the abrupt varactors causing a reduction of the synthesized tuning range. To manage this problem, the reported circuit adopts a switched bank of varactors able to better control the effective C(V) provided by each cell even in case of dc offset. An accurate Montecarlo analysis has been performed and finally the DVCO has been fabricated.

The output synthesized by the prototype has been measured with a spectrum analyzer, Agilent E4407B. The measured tuning ranges are reported in Fig. 6 compared with the simulations in each sub-bands. All the measured sub-bands are smaller than the simulated one and the agreement is not perfect but acceptable.

In Fig. 7 the phase noise at the at the upper band limit of the sub-band 1 is reported. The phase noise measurements in all sub-bands have been estimated by using the following equation:

where fm is the frequency offset and RBW is resolution bandwidth used for the measurement.

In Table 2 the measurements are summarized. The harmonic suppression and phase noise have been measured in 15 values of frequency for each sub-band.

The phase noise measurements pointed out a deterioration in correspondence of the upper limit of each sub-band. Probably, this is due to the different effectiveness of the filtering introduced by the SL, as predicted by the theoretical analysis. Indeed this latter is slightly more effective for frequencies of oscillation close to the lower edge of the range of synthesis.

In Table 3 are reported the measurements of similar DVCOs found in literature and operating in forward gain mode.

Measurements demonstrated that the proposed technique achieves a wider tuning range compared to previous implementations while providing uniform performances. Moreover, the proposed approach can be easily frequency scaled furnishing a powerful solution even for mm-wave applications.

5 Conclusions

As expected from theory, the experimental results for the proposed DVCO demonstrate good performances in terms of wide tuning range, phase noise, and harmonics suppression.

The key advantages of the proposed structure reside in the availability over a wide bandwidth of a gain-tank and the concurrent possibility to implement the “switched-cells tuning technique”. This represents an optimum starting point to design a wideband VCO like those required by modern advanced transceivers.

References

Mitola, J. (1995). The software radio architecture. IEEE Communications Magazine, 33(5), 26–38.

Rong, S., & Loung, H. C. (2012). Analysis and design of transformed-based dual-band VCO for software-defined radios. IEEE Transactions Circuits and Systems-I, 59(3), 449–462.

W.F. Hao, K. S. Yeo, & W.M. Lim (2012). A 60 GHz VCO with 25.8% Tuning range by switching return-path in 65 nm CMOS. In: Proceedings of the Asian Solid State Circuits Conference, pp. 277–280.

W. Deng, K. Okada, & A. Matsuzawa (2011). A 25 MHz-6.44 GHz LC-VCO using a 5-port inductor for multi-band frequency generation. In: Proceedings of the Radio Frequency Integrated Circuits Symposium, pp. 1–4.

Y. Kim, B. Cho, & Y. Na (2009). A design of fractional-N frequency synthesizer with quad-band (700 MHz/AWS/2100 MHz/2600 MHz) VCO for LTE application in 65 nm CMOS process. In: Proceedings of the Asia Pacific Microwave Conference, pp. 369–372.

M. Tiebout (2002). A CMOS fully integrated 1 GHz and 2 GHz dual band VCO with a voltage controller inductor. In: Proceedings of the ESSCIRC, pp. 799–802.

Tchamov, N., Broussev, S., Uzunov, I., & Rantala, K. K. (2007). Dual-band LCVCO architecture with a fourth-order resonator. IEEE Transactions Circuits and Systems-II, 54(3), 277–281.

Borremans, J., Bevilacqua, A., Bronckers, S., Dehan, M., Kuijk, M., Wambacq, P., & Craninckx, J. (2008). A compact wideband front-end using a single-inductor dual-band VCO in 90 nm digital CMOS. IEEE Journal of Solid State Circuits, 43(12), 2693–2705.

Skvor, Z., Saunders, S. R., & Aitchison, C. S. (1992). Novel decade electronically tunable microwave oscillator based on the distributed amplifier. Electronics Letters, 28(17), 1647–1648.

Divina, L., & Skvor, Z. (1998). The distributed oscillator at 4 GHz. IEEE Transactions on Microwave Theory and Techniques, 46(12), 2240–2243.

S.-F. Chang, M.-D. Wei, S.-C. Chang, T.-Y. Chih, J.-C. Wu & J.-L. Chen (2007). A Ka band distributed voltage-controlled oscillator with costant 15-dBm output power. In: Proceedings of the 16th IEEE Mobile and Wireless Communications Summit, pp. 1–4.

A. Acampora, A. Collado & A. Georgiadis (2010). Nonlinear analysis and optimization of a distributed voltage controlled oscillator for cognitive radio. In: Proceedings of the IEEE Int. Microwave Workshop on RF Front-ends for Software Defined and Cognitive Radio Solutions, pp. 1–4.

Hui, Wu, & Hajimiri, A. (2001). Silicon-based distributed voltage-controlled oscillators. IEEE Journal of solid-state circuits, 36(3), 493–502.

B. Kleveland, C. H. Diaz, D. Dieter, L. Madden, T. H. Lee, & S. S. Wong (1999). Monolithic CMOS distributed amplifier and oscillator. In: Proceedings of the IEEE ISSCC Digest of Technical Papers, pp. 70–71.

Bilionis, P., Birbas, A. N., & Birbas, M. K. (2007). Fully integrated differential distributed VCO in 0.35-μm SiGe BiCMOS technology. IEEE Transactions on Microwave Theory Techniques, 55(1), 13–22.

N.Seller, A. Cathelin, H.Lapuyade, J.B. Begueret, E. Chataigner & D. Belot (2007). A 10 GHz distributed voltage controlled oscillator for WLAN application in a VLSI 65 nm CMOS process. In: Proceedings of the IEEE RFIC Symposium, pp. 115–118.

K. Bhattacharyya & T.H. Szymanski (2005). Performance of a 12 GHz monolithic microwave distributed oscillator in 1,2 V 0.18um CMOS with a new simple design technique for frequency changing. In: Proceedings of the IEEE WAMICON, pp. 174–177.

Tsang, K. F., & Yuen, C. M. (2004). A 2.7 V, 5.2 GHz Frequency synthesizer with 1/2-subharmonically injection-locked distributed voltage controlled oscillator. IEEE Transaction on Consumer Electronics, 50(4), 1237–1243.

E.-C. Park & E. Yoon (2004). A 13 GHz CMOS distributed oscillator using MEMS coupled transmission lines for low phase noise. In: Proceedings of the IEEE ISSCC Digest of Technical Papers, pp. 300–309.

Guckenberger, D., & Kornegay, K. T. (2005). Design of a differential distributed amplifier and oscillator using close-packed interleaved transmission lines. IEEE Journal of Solid-State Circuits, 40(10), 1997–2007.

Chien, J. C., & Lu, L.-H. (2007). Design of wide-tuning-range millimeter-wave CMOS VCO with a standing-wave architecture. IEEE Journal of Solid State Circuits, 42(9), 1942–1952.

Z.A.Shaik & P.N.Shastry (2006). A novel distributed voltage-controlled oscillator for wireless systems. In: Proceedings the of IEEE of Radio and Wireless Symposium, pp. 423–426.

Avitabile, G., Cannone, F., Capodiferro, M., Carella, L., & Lofù, N. (2006). Coarse-fine, wideband distributed voltage controlled oscillator for wireless applications. Electronics Letters, 42(5), 285–286.

F. Cannone, G.Avitabile, & N. Lofù (2006). New wideband distributed voltage controlled oscillator with a coarse-fine tuning. In: Proceedings of the 9th European Conference on Wireless Technology, pp. 302–305.

Grebennikov, A. (2007). RF and microwave transistor oscillator design (pp. 360–398). Hoboken, NJ: Wiley.

Ma, D. K., & Long, J. R. (2004). A subharmonically injected LC delay line oscillator for 17 GHz quadrature LO generation. IEEE Journal of Solid State Circuits, 39(9), 1434–1445.

F. Cannone & G. Avitabile (2008). Multi-band VCO based on distributed VCO and switched-capacitors banks. In: Proceedings of the 17th MIKON, pp. 1–4.

F. Cannone, G. Avitabile & D. Cascella (2010). Multi-standard/multi-band distributed VCO based on the”switched-cells tuning technique” for SDR applications. In: Proceedings of the International Symposium on Circuits and Systems, pp. 1991–1994.

D. R. Jachowski, & C. M. Krowne (2004). Frequency dependent of left-handed and right-handed periodic transmission structures. In: Proceedings of the MTT-S, pp. 1831–1834.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

Open Access This article is distributed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made.

About this article

Cite this article

Cannone, F., Avitabile, G. Analysis and design of wideband distributed VCOs based on switched-cells tuning technique. Analog Integr Circ Sig Process 84, 43–51 (2015). https://doi.org/10.1007/s10470-015-0555-6

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-015-0555-6