Abstract

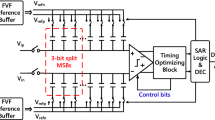

Successive-approximation-register (SAR) ADC has gained popularity owing to its low power consumption in the growing field of ADC development. This work describes such a structure through the use of a novel low offset comparator thereby reducing the non-linearity performance along with significant improvement in energy-delay metric. A high speed control circuitry is introduced to improve the overall frequency of operation of SAR-ADC minimizing its speed limitation. Capacitive based digital-to-analog converter is used that switches in alternate cycles to reduce the static power dissipation. The ADC architecture is designed in 45-nm CMOS technology at layout of \(0.0139 \,{\hbox {mm}}^{2}\). The extracted results show that the proposed design is a reliable framework to ascertain the effectiveness of SAR-ADC with a faster performance. The results demonstrate an improvement of 47.75% in figure-of-merit. SNDR and SFDR are found to be 57.2 dB and 61.4 dB respectively at input frequency of 10 MHz. The sampling frequency is taken as 1 GHz with a power supply of 1 V.

Similar content being viewed by others

References

Sekimoto, R., Shikata, A., Yoshioka, K., Kuroda, T., & Ishikuro, H. (2013). A 0.5-V 5.2-fJ/conversion-step full asynchronous SAR ADC with leakage power reduction down to 650 pW by boosted self-power gating in 40-nm CMOS. IEEE Journal of Solid-State Circuits, 48(11), 2628–2636. https://doi.org/10.1109/JSSC.2013.2274851.

Razavi, B. (2013). Design considerations for interleaved ADCs. IEEE Journal of Solid-State Circuits, 48(8), 1806–1817. https://doi.org/10.1109/JSSC.2013.2258814.

Hu, W., Liu, Y. T., Nguyen, T., Lie, D. C., & Ginsburg, B. P. (2013). An 8-bit single-ended ultra-low-power SAR ADC with a novel DAC switching method and a counter-based digital control circuitry. IEEE Transactions on Circuits and Systems I: Regular Papers, 60(7), 1726–1739. https://doi.org/10.1109/TCSI.2012.2230587.

Guo, W., Kim, Y., Tewfik, A. H., & Sun, N. (2017). A fully passive compressive sensing SAR ADC for low-power wireless sensors. IEEE Journal of Solid-State Circuits, 52(8), 2154–2167. https://doi.org/10.1109/JSSC.2017.2695573.

Weaver, S., Hershberg, B., & Moon, U.-K. (2014). Digitally synthesized stochastic flash ADC using only standard digital cells. IEEE Transactions On Circuits and Systems I: Regular Papers, 64(1), 84–91. https://doi.org/10.1109/TCSI.2013.2268571.

Weaver, S., Hershberg, B., Kurahashi, P., Knierim, D., & Moon, U. (2010). Stochastic flash analog-to-digital conversion. IEEE Transactions on Circuits and Systems I, 57(11), 2825–2833. https://doi.org/10.1109/19.728791.

Liu, Y. T., Xing, D. Y., Wang, Y., & Chen, J. (2016). A dual-exposure wide dynamic range CMOS image sensor with 12 bit column-parallel incremental sigma-delta ADC. Microelectronics Journal, 55, 189–194. https://doi.org/10.1016/j.mejo.2016.07.006.

Fan, H. (2017). Effective method to improve linearity of high-resolution SAR ADC. Microelectronics Journal, 61, 35–42. https://doi.org/10.1016/j.mejo.2016.12.010.

Tripathi, V., et al. (2013). An 8-bit 450-MS/s single-bit/cycle SAR ADC in 65-nm CMOS. In Proceedings of IEEE ESSCIRC (pp. 117–120). https://doi.org/10.1109/ESSCIRC.2013.6649086.

Wei, H., et al. (2011). A 0.024 mm\(^2\) 8b 400 MS/s SAR ADC with 2b/cycle and resistive DAC in 65 nm CMOS. In IEEE ISSCC Digest of Technical Papers (pp. 188–190). https://doi.org/10.1109/ISSCC.2011.5746276.

Kull, L., et al. (2013). A 3.1 mW 8b 1.2 GS/s single-channel asynchronous SAR ADC with alternate comparators for enhanced speed in 32 nm digital SOI CMOS. In IEEE ISSCC Digest of Technical Papers (pp. 468–469). https://doi.org/10.1109/ISSCC.2013.6487818.

Hu, V. P. H., Fan, M. L., Su, P., & Chung, C. T. (2013). Threshold voltage design and performance assessment of hetero-channel SRAM cells. IEEE Transactions on Electronic Devices, 60(1), 147–152. https://doi.org/10.1109/TED.2012.2228863.

Kobayashi, T., Nogami, K., Shirotori, T., & Fujimoto, Y. (1993). A current controlled latch sense amplifier and a static power saving input buffer for low-power architecture. IEEE Journal of Solid State Circuits, 28(4), 523–552. https://doi.org/10.1109/4.210039.

Han, J., et al. (2012). A 64 \(\times\) 32bit 4-read 2-write low power and area efficient register file in 65 nm CMOS. IEICE Electronics Express, 9(16), 1355–1361. https://doi.org/10.1109/ASICON.2011.6157311.

Schienkel, D., Mensink, E., Kiumperink, E., van Tuijl, E., & Nauta, B. (2007). A double tail latch type voltage sense amplifier with 18 ps set up\(+\)hold time. In International Solid State Conference (pp. 314–315). https://doi.org/10.1109/ISSCC.2007.373420.

Jeon, H., & Kim, Y. B. (2012). A novel low power, low offset and high speed CMOS dynamic latched comparator. Analog Integrated Circuits and Signal Processing, 70(3), 337. https://doi.org/10.1007/s10470-011-9687-5.

Mashadi, S. B., & Lotfi, R. (2014). Analysis and design of a low voltage low power double tail comparator. IEEE Transactions on Very Large Scale Integration (VLSI), 22(2), 343–352. https://doi.org/10.1109/TVLSI.2013.2241799.

Lei, K. M., Mak, P. I., & Martins, R. P. (2013). Systematic analysis and cancellation of kickback noise in a dynamic latched comparator. Analog Integrated Circuits and Signal Processing, 77(2), 277–284. https://doi.org/10.1007/s10470-013-0156-1.

Nakajima, Y., Kato, N., Sakaguchi, A., Ohkido, T., & Miki, T. (2013). A 7-bit 1.4 GS/s ADC with offset drift suppression techniques for one-time calibration. IEEE Transactions on Circuits and Systems-I, 60(8), 1979–1990. https://doi.org/10.1109/TCSI.2013.2256236.

Chen, V., & Pileggi, L. (2014). A 69.5 mw 20 gs/s 6b time-interleaved ADC with embedded time-to-digital calibration in 32 nm CMOS SOI. IEEE Journal of Solid State Circuits, 29(12), 2891–2901. https://doi.org/10.1109/JSSC.2014.2364043.

Cai, S., Tabasy, E., Shafik, A. Z., Kiran, S., Hoyos, S., & Palermo, S. (2015). A 25 gs/s 6b TI binary search ADC with soft-decision selection in 65 nm CMOS. In Symposium on VLSI circuits. https://doi.org/10.1109/VLSIC.2015.7231248.

Arian, A., et al. (2012). A 10-bit 50-MS/s redundant SAR ADC with split capacitive-array DAC. Analog Integrated Circuits and Signal Processing, 71(3), 583–589. https://doi.org/10.1007/s10470-011-9812-5.

Liu, M., Xie, Y., & Zhu, Z. (2016). A 67.2 dB SNDR 1.8-V 12-bit 2-MS/s SAR ADC without calibration. Analog Integrated Circuits and Signal Processing, 86(1), 151–158. https://doi.org/10.1007/s10470-015-0662-4.

Wakimoto, T., Li, H., & Murase, K. (2011). Statistical analysis on the effect of capacitance mismatch in a high-resolution successive-approximation ADC. IEEJ Transactions on Electrical and Electrical Engineering, 6(S1), 89–93. https://doi.org/10.1002/tee.20625.

Gylling, V., & Olsson, R. (2015). Implementation of a 200 MSps 12-bit SAR ADC. Master Thesis, Department of Information Technology, Lund University.

McCarthy, M. (2003). Peak-to-peak resolution versus effective resolution. Application Note AN-615. Analog Device.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Begum, F., Mishra, S., Islam, M.N. et al. A 10-bit 2.33 fJ/conv. SAR-ADC with high speed capacitive DAC switching using a novel effective asynchronous control circuitry. Analog Integr Circ Sig Process 100, 311–325 (2019). https://doi.org/10.1007/s10470-019-01450-w

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-019-01450-w