Abstract

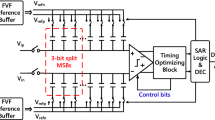

This paper presents a 10-bit 2.5-MS/s successive-approximation-register (SAR) analog- to-digital-converter (ADC) design for micro controller unit of signal process system. Because of the proposed new segmented architecture of 7 MSBs-plus-3 LSBs capacitor–resistor hybrid digital-to-analog-converter using a thermometer decoder for the most significant 5 MSBs, this design achieves superior static nonlinearity and dynamic performance of SNDR, SFDR. Utilizing the proposed deviation calibration technique, the discharging and charging via substrate resulting from deviation of the comparator’s common-mode voltage is cancelled. The ADC is fabricated in a standard 1P5M 0.13-μm CMOS technology. The peak DNL and INL are +0.18/−0.20-LSB, +0.30/−0.25 LSB respectively while the ENOB is 9.52-bit around all process–voltage–temperature corner analysis. At a 2.3-V supply voltage and a 2.5-MS/s sampling rate, the ADC achieves a SNDR of 60.46 dB, SFDR of 75.32 dB while the power dissipation is 0.191-mW, that resulting in a figure of merit of 98.45 fJ/c-s. The die of ADC measures 0.51 × 0.20 mm2 resulting in area efficiency of 122.6 μm2/code and compared with the benchmark SAR ADCs, this work is the most area efficient design.

Similar content being viewed by others

References

Lee, J., Kang, J., et al. (2009). A 2.5 mW 80 dB DR 36 dB SNDR 22 MS/s logarithmic pipeline ADC. IEEE Journal of Solid-State Circuits, 44(10), 2755–2765.

Lee, C., & Flynn, M. (2011). A SAR assisted two-stage pipeline ADC. IEEE Journal of Solid-State Circuits, 46(4), 859–869.

Lin, Y., Doris, K., et al. (2012). An 11b pipeline ADC with parallel-sampling technique for converting multi-carrier signals. IEEE Transactions on Circuits and Systems I, 59(5), 906–914.

Chang, S.-I., Yoon, E. (2009). A low-power area-efficient 8 bit SAR ADC using dual capacitor arrays for neural micro-systems. 2009 Annual International Conference of the IEEE in Engineering in Medicine and Biology Society, 1647–1650.

Hwang, T.-H., Cui, W.-H., Yang, I.-S., & Kwon, O.-K. (2010). A highly area-efficient controller for capacitive touch screen panel systems. IEEE Transactions on Consumer Electronics, 56(2), 1115–1122.

Liu, C.-C., Chang, S.-J., Huang, G.-Y., & Lin, Y.-Z. (2010). A 10 bit 50 MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE Journal of Solid-State Circuits, 45(4), 731–740.

Furuta, M., Nozawa, M., & Itakura, T. (2011). A 10-bit, 40-MS/s, 1.21 mw pipelined SAR ADC using single-ended 1.5-bit/cycle conversion technique. IEEE Journal of Solid-State Circuits, 46(6), 1360.

Dey, A., & Bhattacharyya, T. (2011). A low power 120 KSPS 12-bit SAR ADC with a novel switch control method for internal DAC, in SOC Conference (SOCC), 2011 IEEE International, 76–80.

Elzakker, M. V., et al. (2008). A 1.9uW 4.4 fJ/conversion-step 10 bit 1 MS/s charge redistribution ADC. IEEE ISSCC Digest of Technical Papers, 45, 244–246.

Ginsburg, B. P., et al. (2008). Highly interleaved 5-bit, 250-MSample/s, 1.2-mW ADC with redundant channels in 65-nm CMOS. IEEE Journal of Solid-State Circuits, 43, 2641.

Kuo, C. H., & Hsieh, C. E. (2011). A high energy-efficiency SAR ADC based on partial floating capacitor switching technique. IEEE ESSCIRC, 475–478.

Ahmed, I., et al. (2009). A 50 MS/s 9.9 mW pipeline ADC with 58 dB SNDR in 0.18 μm CMOS using capacitive charge-pumps. IEEE ISSCC Digest of Technical Papers, 2164–2165.

Verma, N., & Chandrakasan, A. (2007). An ultra-low energy 12 bit rate resolution-scalable SAR ADC for wireless sensor nodes. IEEE Journal of Solid-State Circuits, 42(6), 1196–1205.

Zeng, Z., et.al. (2010). A 10 bit 1 Ms/s low power SAR ADC for RSSI application. 2010 10th IEEE International Conference in Solid-State and Integrated Circuit Technology (ICSICT), 569–571.

Kang, J. J., Flynn, M. P., (2009). A 12 bit 11 MS/s successive approximation ADC with two comparators in 0.13 μm CMOS. 2009 Symposium on VLSI Circuits Digest of Techical Papers, 240–241.

Zhu, Y., Chan, C. H., et al. (2010). A 10-bit 100 MS/s reference-free SAR ADC in 90 nm CMOS. IEEE Journal of Solid-State Circuits, 45(6), 1111–1121.

Acknowledgments

The authors would like to thank HHN Grace, China for chip fabrication and testing support and Ning Zhou, Tao Chen for technical discussions during the chip design and test.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Dai, R., Zheng, Y., Wang, Z. et al. A 10-bit 2.5-MS/s SAR ADC with 60.46 dB SNDR in 0.13-μm CMOS technology. Analog Integr Circ Sig Process 80, 255–261 (2014). https://doi.org/10.1007/s10470-014-0318-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-014-0318-9