Abstract

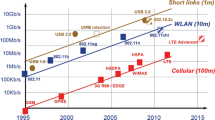

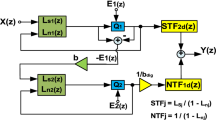

This paper presents a low power and area-efficient 3rd-order continuous-time delta-sigma (CT ΔΣ) modulator for LTE/TD-SCDMA digital receivers. In the proposed modulator, the integrators’ coefficients are programmable to meet all LTE and TD-SCDMA signal bandwidths and dynamic range requirements. Moreover, to meet both the high performance and low-cost requirements, the proposed analog-to-digital converter (ADC) adopts: a low-cost excess loop delay compensation method, a non-return-to-zero feedback digital-to-analog converter (DAC) which is clocked by low-noise LC phase lock loop, an on-chip tuning scheme to reduce sensitivity to bandwidth variations, and dynamic element matching 9-level DACs. The CT ΔΣ modulator is designed and fabricated in a 0.13 μm 1-poly 6-metal standard CMOS technology and occupies an active area of 0.20 mm2. For all signal bandwidths of LTE/TD-SCDMA standards, the proposed ADC achieves 70–87 dB dynamic range, and 66–84 dB peak SNDR with 8.4–10.2 mW power consumption under 1.5 V power supply.

Similar content being viewed by others

References

Technologies, Agilent. (2009). LTE and the evolution to 4G wireless: Design and measurement challenges. London: Wiley.

Prithiviraj, V., Manikandan, K., Prasanna, C., & Saranesh, S. (2009). Front end design of software defined BTS for interoperability between GSM and CDMA. In International conference on wireless communication, vehicular technology, information theory and aerospace & electronic systems technology, 2009. Wireless vitae (pp. 655–659). IEEE.

Shriram, K. V., Venkateshwaran, K., Vaithiyanathan, V., & Subashri, V. (2009). Design of analog to digital converter for SDR (software defined radio). In International conference for internet technology and secured transactions, icitst 2009, London, Uk, November (pp. 1–5).

Fakhoury, H., Jabbour, C., Khushk, H., & Nguyen, V. T. (2009). A 65 nm CMOS EDGE/UMTS/WLAN tri-mode four-channel time-interleaved ΣΔ ADC. Circuits and systems and TAISA conference, 2009. NEWCAS-TAISA ‘09. Joint IEEE north-east workshop on (pp. 1–4). IEEE.

Christen, T., & Huang, Q. (2010). A 0.13 µm CMOS 0.1–20 MHz bandwidth 86–70 dB DR multi-mode DT ΔΣ ADC for IMT-Advanced. Esscirc (pp. 414–417). IEEE.

Malla, P., Lakdawala, H., Kornegay, K., & Soumyanath, K. (2008). A 28 mW Spectrum-Sensing Reconfigurable 20 MHz 72 dB-SNR 70 dB-SNDR DT ΔΣ ADC for 802.11n/WiMAX Receivers. In Solid-state circuits conference, 2008. ISSCC 2008. Digest of Technical Papers. IEEE International (pp. 496–631).

Mitteregger, Gerhard, Ebner, Christian, Mechnig, Stephan, Blon, Thomas, Holuigue, Christophe, & Romani, Ernesto. (2007). A 20-mw 640-MHz CMOS continuous-time ΔΣ ADC with 20-MHz signal bandwidth, 80-dB dynamic range and 12-bit ENOB. IEEE Journal of Solid-State Circuits, 41(12), 2641–2649.

Arias, J., Kiss, P., Prodanov, V., & Boccuzzi, V. (2006). A 32-mw 320-MHz continuous-time complex delta-sigma ADC for multi-mode wireless-LAN receivers. IEEE Journal of Solid-State Circuits, 41(2), 339–351.

Paton, S., Giandomenico, A. D., Hernandez, L., Wiesbauer, A., Potscher, T., & Clara, M. (2004). A 70-mw 300-MHz cmos continuous-time ΣΔ ADC with 15-MHz bandwidth and 11 bits of resolution. IEEE Journal of Solid-State Circuits, 39(7), 1056–1063.

Breems, L. J., Rutten, R., & Wetzker, G. (2004). A cascaded continuous-time sigma delta modulator with 67-dB dynamic range in 10-MHz bandwidth. IEEE Journal of Solid State Circuits, 39(12), 2152–2160.

Straayer, M. Z., & Perrott, M. H. (2008). A 12-bit, 10-MHz bandwidth, continuous-time, ADC with a 5-bit, 950-Ms/s vco-based quantizer. IEEE Journal of Solid-State Circuits, 43(4), 805–814.

Reddy, K., & Pavan, S. (2009). A power efficient continuous time ΔΣ modulator with 15 MHz bandwidth and 70 BD dynamic range. Analog Integrated Circuits and Signal Processing, 63(3), 397–406.

Yuan, J., & Yang, Y. (2012). A 22 mw 512 MHz CMOS continuous time Sigma-Delta ADC in 1.2 V with 16 MHz signal bandwidth and 70 DB dynamic range. Analog Integrated Circuits and Signal Processing, 72(1), 47–53.

GPP TS 36.101 V9.0.0, June 2009.

Stefania Sesia, Issam Toufik, & Matthew Baker. (2011). In LTE—The UMTS long term evolution: From theory to practice, second edition.

Norsworthy, S. R. & Schreier R. (1997). Temes g.c. “Delta-Sigma data converters. Theory, design and simulation. Wiley-IEEE Press.

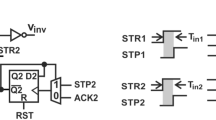

Pavan, S. (2008). Excess loop delay compensation in continuous-time delta-sigma modulators. Circuits & Systems II Express Briefs IEEE Transactions on, 55(II), 1119–1123.

Alamdari, H. H., El-Sankary, K., & El-Masry, E. (2009). Excess loop delay compensation for continuous-time ΔΣ modulators using interpolation. Electronics Letters, 45(12), 609–610.

Dagher, E. H., Stubberud, P. A., Masenten, W. K., Conta, M., & Dinh, T. V. (2004). A 2-GHz analog-to-digital delta-sigma modulator for CDMA receivers with 79-dB signal-to-noise ratio in 1.23-MHz bandwidth. IEEE Journal of Solid-State Circuits, 39(11), 1819–1828.

Keller, M., Buhmann, A., Sauerbrey, J., Ortmanns, M., & Manoli, Y. (2008). A comparative study on excess-loop-delay compensation techniques for continuous-time sigma-delta modulators. IEEE Transactions on Circuits and Systems I: Regular Papers, 55(11), 3480–3487.

Tortosa, R., de la Rosa, J. M., Rodriguez-Vazquez, Angel, & Fernandez, F. V. (2005). Analysis of clock jitter error in multibit continuous-time ΣΔ modulators with NRZ feedback waveform. IEEE International Symposium on Circuits and Systems (vol.39, pp.3103–3106 vol. 4). IEEE.

Schreier, R., & Temes, G. C. In Understanding delta-sigma data converters. Understanding delta-sigma data converters/. IEEE Press.

Baird, R. T., & Fiez, T. S. (1995). Linearity enhancement of multibit ΔΣ A/D and D/A converters using data weighted averaging. IEEE Transactions on Circuits & Systems II Analog & Digital Signal Processing, 42(12), 753–762.

Galton, I. (1997). Spectral shaping of circuit errors in digital-to-analog converters. Circuits & Systems II Analog & Digital Signal Processing IEEE Transactions on, 44(10), 808–817.

Schreier, R., & Zhang, B. (1995). Noise-shaped multibit D/Aconvertor employing unit elements. Electronics Letters, 31(20), 1712–1713.

Risbo, L., Hezar, R., Kelleci, B., Kiper, H., & Fares, M. (2011). Digital approaches to ISI-mitigation in high-resolution oversampled multi-level D/A converters. IEEE Journal of Solid-State Circuits, 46(12), 2892–2903.

Sanyal, A., & Sun, N. (2014). An enhanced ISI shaping technique for multi-bit ΔΣ DACs. In IEEE international symposium on circuits and systems (pp. 2341–2344).

Sanyal, Arindam, Chen, Long, & Sun, Nan. (2015). Dynamic element matching with signal-independent element transition rates for multibit delta sigma modulators. Circuits & Systems I Regular Papers IEEE Transactions on, 62(5), 1325–1334.

Huang, M., Chen, D., Wang, Z., Guo, J., Dagher, E. H., Xu, B., et al. (2014). A power-area-efficient, 3-band, 2-RX MIMO, TD-LTE receiver with direct-coupled ADC. International Journal of Circuit Theory and Applications, 43(6), 806–821.

Schoofs, R., Steyaert, M. S. J., & Sansen, W. M. C. (2007). A design-optimized continuous-time delta-sigma ADC for WLAN applications. Circuits & Systems I Regular Papers IEEE Transactions on, 54(1), 209–217.

Acknowledgments

This work was partly supported by a grant from National Science and Technology Major Project of China (2010ZX03001-004-03). The authors wish to thank the RME layout group and lab group for careful layout design and chip evaluation.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Xu, K., Cai, M., Dagher, E.H. et al. A 10.2 mW multi-mode continuous-time ΔΣ ADC with 70–87 dB DR and 0.7–10 MHz bandwidth for TD-SCDMA and LTE digital receivers. Analog Integr Circ Sig Process 89, 395–410 (2016). https://doi.org/10.1007/s10470-016-0852-8

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-016-0852-8