Abstract

The resistive switching memory characteristics of 100 randomly measured devices were observed by reducing device size in a Cr/CrO x /TiO x /TiN structure for the first time. Transmission electron microscope image confirmed a via-hole size of 0.4 µm. A 3-nm-thick amorphous TiO x with 4-nm-thick polycrystalline CrO x layer was observed. A small 0.4-µm device shows reversible resistive switching at a current compliance of 300 µA as compared to other larger size devices (1–8 µm) owing to reduction of leakage current through the TiO x layer. Good device-to-device uniformity with a yield of >85 % has been clarified by weibull distribution owing to higher slope/shape factor. The switching mechanism is based on oxygen vacancy migration from the CrO x layer and filament formation/rupture in the TiO x layer. Long read pulse endurance of >105 cycles, good data retention of 6 h, and a program/erase speed of 1 µs pulse width have been obtained.

Similar content being viewed by others

1 Introduction

Recently resistive random access memory (RRAM) has been investigated for the next-generation non-volatile memory applications [1, 2]. The RRAM device offers a promise for NVM application due to its simple structure, low power consumption, high density, fast program/erase speed, and low cost [3]. Various materials like HfO x [4], TaO x [5, 6], TiO x [7–10], and so on have been reported by many groups. Other materials such as ZnO [11], BaWO4 [12], and so on have been reported also. Among of them, TiO x is one of the most promising materials owing to its fab-friendly, good thermal stability, adequate band gap (~3.0 eV) for low leakage, high dielectric constant (κ ~ 80), and so on [13]. Kwon et al. [14] have reported the bipolar resistive switching in Pt/TiO2/Pt structure at a high current compliance (CC) of 30 mA. Jeong et al. [15] have reported the bilayer switching layers in a Pt/Ni/a-TiO2/Al2O3/Pt structure with a CC of >1 mA. Park et al. [16] have unveiled the multi-bit resistive switching operation in an Ir/TiO x /TiN structure with a CC of 1 mA. Goren et al. [17] demonstrated bistable memory effect in Co/TiO2/TiO x /Co/Pd structure with a low CC of approximately 100 µA. Zeng et al. [18] have reported resistive switching characteristics using a Pt/ZrO2/TiO2/Pt structure at a CC of 10 mA. Strachan et al. [19] have reported the resistive switching characteristics using a Cr/Pt/TiO2/Pt structure at a CC of 250 µA.

Although many groups have reported these TiO x -based different RRAM devices, however, resistive switching characteristics by reducing device size as well as leakage current in a Cr/CrO x /TiO x /TiN structure have not been investigated yet. To obtain good resistive switching characteristics, both amorphous TiO x switching and polycrystalline CrO x oxygen vacancy supply layers are effectively combined with smaller device sizes. Microstructure and device size are confirmed by transmission electron microscope (TEM) image. The switching mechanism is owing to oxygen vacancy filament formation/rupture into the TiO x switching layer. Weibull distribution plot of 100 randomly measured devices with a size of 0.4 × 0.4 µm2 shows good device-to-device uniformity with a yield of >85 %. It is found that higher slope/shape factor indicates higher uniformity of the devices. By investigating the scale factor, it is found that the device can be operated with low voltage of ±1 V and a low current of <300 µA. Long read pulse endurance of >105 cycles, stable data retention of >6 h, and good program/erase (P/E) endurance with a pulse width of 1 µs are obtained, which indicate future application of this new Cr/CrO x /TiO x /TiN resistive switching memory device.

2 Experimental

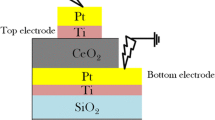

The Cr/CrO x /TiO x /TiN RRAM devices were fabricated using 8-inch SiO2/Si wafers. The device process flow is shown in Fig. 1. The thickness of SiO2 layer was 200 nm. A 200-nm-thick titanium-nitride (TiN) as a bottom electrode (BE) was deposited on SiO2 layer. Next 150-nm-thick SiO2 layer was deposited to different pattern via-hole sizes ranging from 0.4 × 0.4 to 8 × 8 µm2 using both photolithography and dry etching processes. Then, 8 inch wafer was broken to 2 × 2 inch2 pieces and did next step. The chromium (Cr) metal as a top electrode (TE) was deposited by radio frequency (RF) sputtering. The Cr metal target with a constant argon (Ar) gas flow rate of ten sccm was used. During deposition, chamber pressure and deposition power were 6 mTorr and 100 W, respectively. A TiO x resistive switching layer with a CrO x layer was observed after deposition of Cr TE. Finally, lift-off process was done to get a simple Cr/CrO x /TiO x /TiN structure. More than 150 devices for each size were obtained on a small piece of 8 inch wafer.

The memory characteristics were investigated by measuring 100 randomly picked devices. Thickness and microscopic structure of Cr/CrO x /TiO x /TiN RRAM device were analyzed by transmission electron microscopy with energy of 200 keV. Electrical characteristics were measured by Agilent 4156C/B1500 precision semiconductor analyzer. During measurement, the bias was applied on the TE and the BE was grounded.

3 Results and Discussion

Figure 2a shows TEM image of a typical via-hole size of 0.4 × 0.4 µm2. The length of via-hole is found to be approximately 0.5 µm. A thickness of Cr layer is approximately 150 nm. High-resolution TEM image on inside via-hole region confirms the layer-by-layer of Cr/CrO x /TiO x /TiN structure (Fig. 2b). The thickness of amorphous TiO x layer is approximately 3 nm, which acts as a switching layer. This TiO x layer is grown during the Cr TE deposition owing to lower Gibbs free energy of TiO2 (−887.6 kJ (mol)−1 at 300 K). In addition, reactive Cr TE is also partially oxidized at the Cr/TiO x interface and creates CrO x owing to lower Gibbs free energy of Cr2O3 of −694.88 kJ (mol)−1 [20, 21]. This CrO x layer with a thickness of approximately 4 nm is polycrystalline. Elemental analysis of Cr/CrO x /TiO x /TiN structure has been explored by EDX spectrum. The existence of Cr, Ti, O, N elements in corresponding layers of 1, 2, 3 are shown in Fig. 2c. The peaks’ position of Cr, Ti, O, N elements are found to be 5.4, 4.5, 0.4, and 0.28 keV, respectively. Due to both lower Gibbs free energy and deposition by sputtering, the defective CrO x layer is formed or oxygen vacancy is observed in the CrO x layer. Therefore, this CrO x layer acted as an oxygen vacancy supply layer to form conductive filament into the TiO x switching layer and good switching characteristics can be observed below.

a TEM image of Cr/CrO x /TiO x /TiN RRAM device with a via-hole size of 0.4-µm device. b HRTEM image shows a CrO x layer in between TiO x switching and Cr electrode because of partially oxidization of Cr metal during deposition. c EDX spectrum confirms the presence of Cr, Ti, O, and N elements in 1, 2, and 3 denoted layers of (b)

Figure 3a exhibits the current–voltage (I–V) switching characteristics of a 0.4-µm device at a CC of 300 µA. Voltage sweeping direction is shown by arrows 1–4. The device requires a very small forming voltage (V form) of 0.9 V because of both thin TiO x switching layer and vacancy supply from the CrO x layer. Small SET (V SET) and RESET voltages (V RESET) are found to be 0.6 and −0.6 V, respectively. The RESET currents are found to be 314 and 391 µA for first and second cycle, respectively.

Current–voltage characteristics with device size-dependence switching of 100 measured devices. a Bipolar I–V switching characteristics. b Cumulative probability of RESET currents for 0.4-µm device at a low CC of 300 µA, c Box chart plot of IRS, HRS, and LRS of 0.4, 1, and 8 µm devices. Error bars mean a range of total data distribution

Cumulative probability of RESET currents for the first and second cycles is shown in Fig. 3b. At a 50 % probability, the RESET currents are found to be 329 and 344 µA for 1st and 2nd cycles, respectively. The RESET current is slightly higher (~15 %) than current compliance owing to small current overshoot effect, which can be reduced by optimizing operation current. Further study is needed to evaluate this effect. This current overshoot effect is happening during formation or SET of the devices. Therefore, this structure provides good current clamping and minimizes current overshoot effects, even a one-resistor (1R) configuration.

Cumulative probability of initial resistance state (IRS), high resistance state (HRS), and low resistance state (LRS) for three different device sizes of 0.4, 1, and 8 µm is shown in Fig. 3c. The average values of IRS are 457.5, 46.5, and 670 Ω for the 0.4-, 1-, and 8-µm devices, respectively. The leakage currents increase with increasing device sizes, which are owing to the presence of much higher amount of defects or oxygen vacancies (V o) in larger device sizes. The average values of HRS/LRS are 144/2.7, 1.5/1.2 kΩ, and 188/175 Ω for 0.4, 1, and 8 µm, respectively at a read voltage (V read) of 0.2 V. This implies that large size devices (1 and 8 µm) do not show the bipolar resistive switching at a low CC of 300 µA. By reducing the device size as well as leakage current, good resistive switching characteristics could be observed even a simple structure has been designed and fabricated here. In addition, it is found that a non-zero current of approximately 2 × 10−7 A is observed at initial and high resistance state, which might possibly be due to capacitive effect. However, a further study is needed.

Figure 4a shows weibull distribution of IRS, HRS ,and LRS for the 0.4-µm devices. These narrow dispersion values interpret that device-to-device uniformity is good with a yield (i.e., switchable devices with consecutive 2 cycles and resistance ratio is >2) of 85 %. We can justify successive switching devices or reliability test as follows by weibull distribution plot [22]. Mathematically, this can be expressed as

where F(Q) is the cumulative distribution function of failure, Q is the values of measured data, β is the slope value of weibull distribution curve or shape factor which signifies the statistical dispersion of data, and α 63 % is the scale factor value from weibull distribution at approximately F = 63 %. Higher β value means that distribution is more uniform. The uniform distribution means that the fitting line should be perpendicular on X-axis. Using Eq. (1), weibull distribution patterns of IRS, HRS, LRS, V form, V SET, and V RESET for the 0.4-µm devices have been depicted in Fig. 4. Using Eq. (2), the values of β are found to be from the fitting curves, as shown by straight line. The β value of LRS (2.5) distribution is narrower than those of both HRS (1.84) and IRS (1.1), as listed values in Table 1. In addition, IRS distribution of the 0.4-µm devices is narrowest as compared to widely scattered β values for 1-µm (0.46) and 8-µm (0.96) devices (not shown here), which may also related to the higher leakage.

It is found that the average values of V form, V SET, V RESET for the 0.4-µm devices are 0.9, 0.7, and −0.54 V, respectively. As compared to the V SET, a small V form of 0.9 V is necessary to switch a pristine device or it is like a forming-free device, which is very useful for integrated circuit (IC) application and saving extra device process step as well as low cost. The formation step can be avoided by reducing voltage of <3 V then the device will be used directly after fabrication. A 3 V battery can be used directly to program/erase this memory device or extra voltage amplifier which is used in Flash memory is not needed. The β values of V form, V SET, and V RESET are 10.4, 7.34, and 3.9 (Fig. 4b–d), which suggests that formation of the devices is more uniform than those of the SET and RESET voltages. The values of standard deviation of V form, V SET, and V RESET are 0.174, 0.189, and 0.139, respectively, which assert good device-to-device uniformity yield.

The values of scale factor (α 63 %) for the HRS and LRS are found to be 139.5 and 6 kΩ, respectively. A resistance ratio of approximately 20 is obtained. For a single bit operation, a resistance ratio of >2 is enough to indentify ‘0’ and ‘1’ states [1, 3, 23]. The higher resistance ratio is better for MLC operation. Therefore, scientists are as large as resistance ratio with maintaining other memory parameters, which is also good for future application. The values of α 63 % for the V form, V SET, and V RESET are found to be 0.97, 0.66, and −0.64 V, respectively. This suggests that the device could be operated at low voltage of ±1 V.

To evaluate the current conduction mechanism, LRS shows ohmic and HRS shows the space-charge-limited current conduction (SCLC). Stochastic filament formation in TiO x layer by oxygen vacancy will lead to respond to the ohmic nature of LRS. On the other hand, injected electrons through the electrodes are exceeded than those thermally generated free electrons in the TiO x layer. Therefore, oxygen vacancy filament formation/rupture into the TiO x layer under external bias is the switching mechanism, which is also reported by other research groups in different structures [14, 19, 24]. In the Cr/CrO x /TiO x /TiN structure, when positive bias is applied on the Cr TE then the potential is distributed in series of TiO x and CrO x layers. It is true that TiO x layer has more insulating property than the CrO x layer. Therefore, the potential drop on a pristine device is higher across the TiO x layer. Then, Ti–O bonds start to break and electrical conductivity of the TiO x layer is increased. In this situation, the potential drop (V > V form > V SET) across CrO x layer is increased, which results in the oxygen vacancies as a positive charge in the CrO x layer moving towards TiO x layer as well as the V o filament is formed into the TiO x layer (Fig. 5a). The device switches from IRS (or HRS) to LRS. By applying negative bias (V < V RESET) on the Cr TE, the oxygen vacancies attracted toward the TE and stored into the CrO x layer, which results that the filament is broken (Fig. 5b). Then, the device switches back from LRS to previous HRS. However, there is difference in between IRS and HRS because of Ti–O bonds break during the formation of filament initially. Due to these CrO x /TiO x bilayers’ action, repeatable bipolar resistive switching cycles are observed.

Schematic illustration of switching mechanism. a Under SET operation, the oxygen vacancy is migrated from CrO x layer to the TiO x switching layer and oxygen vacancy conducting filament is formed. b Under RESET operation, the oxygen vacancy is moved toward CrO x layer from the TiO x layer and the filament is ruptured

To explore the performance potentiality of the Cr/CrO x /TiO x /TiN RRAM devices, program/erase (P/E) endurance and data retention characteristics have been evaluated (Fig. 6). The memory device shows long read pulse endurance measured at V read of 0.2 V (Fig. 6a). The device is programed with difference CCs of 300 and 500 µA. After programing the data are read with a pulse width of 500 µs. The LRS values for CCs of 300 and 500 µA are 5 and 3 kΩ, respectively. The value of LRS decreases with increasing current compliance, which can be used as a multi-level cell. After erasing the data are read with a pulse width of 500 µs. The long read pulse endurance of >105 cycles is obtained. Good data retention of 6 h with a good memory window (HRS/LRS) of approximately 40 can be achieved from this RRAM device (Fig. 6b). This memory device shows good P/E endurance of >500 cycles at V read of 0.2 V (Fig. 6c). A P/E pulse width of 1/1 µs and voltage of 3/−2 V are applied. A small fluctuation of LRS in both data retention and P/E endurance was observed, which can be assumed to be the generation and redistribution of oxygen vacancies in the TiO x switching layer owing to rapid increasing pulse operation. Shen et al. [25] have also discussed about the P/E endurance failure in Pt/BST/SRO RRAM structure due to generation and redistribution of defects in switching material. Further improvement is needed for P/E cycles. Eventually, this memory device with reducing size has very keen potential for future nanoscale non-volatile memory application.

4 Conclusions

In summary, observation of resistive switching memory by reducing device size as well as leakage current has been revealed in a new Cr/CrO x /TiO x /TiN RRAM device. By measuring 100 random devices it is found that a smaller size device has lower leakage current and resistive switching characteristics are observed. Both TEM image and EDX spectrum confirm a device size of 0.4 × 0.4 µm2 with the presence of amorphous TiO x and polycrystalline CrO x layer is also observed. The 0.4-µm devices can perform resistive switching at a low CC of 300 µA owing to lower leakage current as compared to larger size devices. Weibull plots of IRS, HRS, LRS, V form, V SET, and V RESET show that more than 85 % devices have good switching with tight distribution. The slope/shape factor indicates the device uniformity. The resistive switching is due to the formation/rupture of oxygen vacancy filament in the TiO x switching layer and the CrO x layer acts as a vacancy supply layer. Therefore, long read pulse endurance of >105 cycles, data retention of >6 h, and P/E endurance of >500 cycles with a pulse width of 1 µs at a low operation current of 300 µA are obtained. It is concluded that a new Cr/CrO x /TiO x /TiN RRAM device has a simple fabrication process and good resistive switching memory characteristics, which will be very promising for future nanoscale non-volatile memory application.

References

F. Pan, S. Gao, C. Chen, S. Song, F. Zeng, Recent progress in resistive random access memories: materials, switching mechanisms, and performance. Mater. Sci. Eng. R 83, 1–59 (2014). doi:10.1016/j.mser.2014.06.002

K. Terabe, T. Hasegawa, T. Nakayama, M. Aono, Quantized conductance atomic switch. Nature 433, 47–50 (2005). doi:10.1038/nature03190

R. Waser, M. Aono, Nanoionics-based resistive switching memories. Nat. Mater. 6, 833–840 (2007). doi:10.1038/nmat2023

B. Govoreanu, G.S. Kar, Y-Y. Chen, V. Paraschiv, S. Kubicek, et al., 10 × 10 nm2 Hf/HfO x crossbar resistive RAM with excellent performance, reliability and low-energy operation. Electron Devices Meeting (IEDM), 31.6.1–31.6.4. (2011). doi:10.1109/IEDM.2011.6131652

M.-J. Lee, C.B. Lee, D. Lee, S.R. Lee, M. Chang et al., A fast, high-endurance and scalable non-volatile memory device made from asymmetric Ta2O5−x /TaO2−x bilayer structures. Nat. Mater. 10, 625–630 (2011). doi:10.1038/nmat3070

A. Prakash, D. Jana, S. Maikap, TaOx–based resistive switching memories: prospective and challenges. Nanoscale Res. Lett. 8, 418 (2013). doi:10.1186/1556-276X-8-418

B.J. Choi, D.S. Jeong, S.K. Kim, C. Rohde, S. Choi et al., Resistive switching mechanism of TiO2 thin films grown by atomic-layer deposition. J. Appl. Phys. 98, 033715 (2005). doi:10.1063/1.2001146

J.J. Yang, M.D. Pickett, X. Li, D.A.A. Ohlberg, D.R. Stewart, R.S. Williams, Memristive switching mechanism for metal/oxide/metal nanodevices. Nat. Nanotechnol. 3, 429–433 (2008). doi:10.1038/nnano.2008.160

C. Hermes, R. Bruchhaus, R. Waser, Forming-free TiO2-based resistive switching devices on CMOS-compatible W-plugs. IEEE Electron Device Lett. 32(11), 1588–1590 (2011). doi:10.1109/LED.2011.2166371

L. Qingjiang, A. Khiat, L. Salaoru, C. Papavassiliou, X. Hui, T. Prodomakis, Memory impedance in TiO2 based metal-insulator-metal devices. Sci. Rep.-UK 4, 4522 (2014). doi:10.1038/srep04522

L. Li, Y. Zhang, Z. Chew, A Cu/ZnO nanowire/Cu resistive switching device. Nano-Micro Lett. 5(3), 159–162 (2013). doi:10.1007/BF03353745

B. Sun, Y. Liu, W. Zhao, J. Wu, P. Chen, Hydrothermal preparation and white-light controlled resistive switching behavior of BaWO4 nanospheres. Nano-Micro Lett. 7(1), 80–85 (2014). doi:10.1007/s40820-014-0021-5

B. Prasai, B. Sai, M.K. Underwood, J.P. Lewis, D.A. Drabold, Properties of amorphous and crystalline titanium dioxide from first principles. J. Mater. Sci. 47(21), 7515–7521 (2012). doi:10.1007/s10853-012-6439-6

D.-H. Kwon, K.M. Kim, J.H. Jang, J.M. Jeon, M.H. Lee et al., Atomic structure of conducting nanofilaments in TiO2 resistive switching memory. Nat. Nanotechnol. 5, 148–153 (2010). doi:10.1038/nnano.2009.456

H.Y. Jeong, J.Y. Lee, S.Y. Choi, Interface-engineered amorphous TiO2-based resistive memory devices. Adv. Funct. Mater. 20, 3912–3917 (2010). doi:10.1002/adfm.201001254

J. Park, M. Jo, S. Jung, J. Lee, W. Lee, S. Kim, S. Park, J. Shin, H. Hwang, New set/reset scheme for excellent uniformity in bipolar resistive memory. IEEE Electron Device Lett. 32(3), 228–230 (2011). doi:10.1109/LED.2010.2094599

E. Goren, M. Ungureanu, R. Zazpe, M. Rozenberg, L.E. Hueso, P. Stoliar, Y. Tsur, F. Casanova, Resistive switching phenomena in TiO x nanoparticle layers for memory applications. Appl. Phys. Lett. 105, 143506 (2014). doi:10.1063/1.4897142

B. Zeng, D. Xu, M. Tang, Y. Xiao, Y. Zhou, R. Xiong, Z. Li, Y. Zhou, Improvement of resistive switching performance via an amorphous ZrO2 layer formation in TiO2-based forming-free resistive random access memory. J. Appl. Phys. 116, 124514 (2014). doi:10.1063/1.4896402

J.P. Strachan, M.D. Pickett, J.J. Yang, S. Aloni, A.L.D. Kilcoyne, G.M. Ribeiro, R.S. Williams, Direct identification of the conducting channels in a functioning memristive device. Adv. Mater. 22, 3573–3577 (2010). doi:10.1002/adma.201000186

W.Y. Chang, H.W. Huang, W.T. Wang, C.H. Hou, Y.L. Chueh, J.R. He, High uniformity of resistive switching characteristics in a Cr/ZnO/Pt device. J. Electrochem. Soc. 159, G29–G32 (2012). doi:10.1149/2.092203jes

N.R. Mann, R.E. Schafer, N.D. Singpurwalla, Methods for Statistical Analysis of Reliability and Life Data (Wiley publishers, New York, 1974)

K. Kamiya, M.Y. Yang, S.G. Park, B.M. Kope, Y. Nishi, M. Niwa, K. Shiraishi, ON–OFF switching mechanism of resistive-random-access-memories based on the formation and disruption of oxygen conducting channels. Appl. Phys. Lett. 100, 073502 (2012). doi:10.1063/1.3685222

S. Roy, S. Maikap, G. Sreekanth, M. Dutta, D. Jana, Y.Y. Chen, J.R. Yang, Improved resistive switching phenomena and mechanism using Cu–Al alloy in a new Cu:AlO x /TaO x /TiN structure. J. Alloy. Compd. 637, 517–523 (2015). doi:10.1016/j.jallcom.2015.02.168

H.H. Pham, L.W. Wang, Oxygen vacancy and hole conduction in amorphous TiO2. Phys. Chem. Chem. Phys. 17, 541 (2015). doi:10.1039/C4CP04209C

W. Shen, R. Dittmann, U. Breuer, R. Waser, Improved endurance behavior of resistive switching in (Ba, Sr)TiO3 thin films with W top electrode. Appl. Phys. Lett. 93, 222102 (2008). doi:10.1063/1.3039809

Acknowledgments

This work was supported by Ministry of Science and Technology (MOST) Taiwan, under Contract no. NSC-102-2221-E-182-057-MY2. The authors are grateful to EOL/ITRI, Hsinchu, Taiwan for their experimental support.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

Open Access This article is distributed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made.

About this article

Cite this article

Jana, D., Samanta, S., Roy, S. et al. Observation of Resistive Switching Memory by Reducing Device Size in a New Cr/CrO x /TiO x /TiN Structure. Nano-Micro Lett. 7, 392–399 (2015). https://doi.org/10.1007/s40820-015-0055-3

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s40820-015-0055-3