Abstract

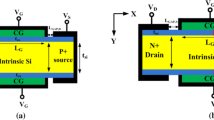

Accumulation of trap charges at the semiconductor and oxide interface is the most dominating factor and cannot be neglected as it degrades device performance and reliability. This manuscript, presents detailed investigation to analyze the impact of interface trap charges (ITCs) on the performance parameters of the proposed device i.e., heterogeneous dielectric dual metal gate step channel TFET (HD DMG SC-TFET). The comparative study is conducted with dual metal gate step channel TEFT (DMG SC-TFET). The proposed device shows improved current carrying capability, suppressed ambipolar behaviour with steeper subthreshold swing. The purpose of this study to determine the ITCs impact on DC characteristics and analog/RF electrical performance parameters of the proposed device. It further observed that the proposed device exhibit superior performance due to dielectric engineering at oxide layer. Moreover, advanced communication devices must respond linearly therefore, the impact of ITCs on linearity parameters is also studied. From this brief comparative investigation, it is observed that the proposed TFET exhibits negligible distortion in linearity parameters with little or no impact of trap charges as compared to DMG SC-TFET. Thus, proposed TFET is appropriate for ultra-low power high-frequency electronic devices.

Similar content being viewed by others

Data Availability

The data and material concerned to the manuscript may be made available on request.

References

Koswatta SO, Lundstrom MS, Nikonov DE (2009) Performance comparison between pin tunneling transistors and conventional mosfets. IEEE Transactions on Electron Devices 56(3):456–465

Tsai M-H, Ma T-P (1994) The impact of device scaling on the current fluctuations in mosfet’s. IEEE Transactions on Electron Devices 41(11):2061–2068

Sun S-W, Tsui PG (1995) Limitation of cmos supply-voltage scaling by mosfet threshold-voltage variation. IEEE Journal of Solid-State Circuits 30(8):947–949

Saraswat S, Yadav DS, Kumar S, Parmar N, Sharma R, Kumar A (2020) Performance analysis of tmg finfets for low power application with improved analog/rf characteristics, pp 1–5

Choi WY, Park B-G, Lee JD, Liu T-JK (2007) Tunneling field-effect transistors (tfets) with subthreshold swing (ss) less than 60 mv/dec. IEEE Electron Device Letters 28(8):743–745

Bizindavyi J, Verhulst AS, Smets Q, Verreck D, Sorée B, Groeseneken G (2018) Band-tails tunneling resolving the theory-experiment discrepancy in esaki diodes. IEEE Journal of the Electron Devices Society 6:633–641

Avci UE, Rios R, Kuhn KJ, Young IA (2011) Comparison of power and performance for the tfet and mosfet and considerations for p-tfet, pp 869–872

Singh P, Samajdar DP, Yadav DS (2021) A low power single gate l-shaped tfet for high frequency application. In: 2021 6th International conference for convergence in technology (I2CT). IEEE, pp 1–6

Avci UE, Morris DH, Young IA (2015) Tunnel field-effect transistors: prospects and challenges. IEEE Journal of the Electron Devices Society 3(3):88–95

Parmar N, Yadav DS, Kumar S, Sharma R, Saraswat S, Kumar A (2020) Performance analysis of a novel dual metal strip charge plasma tunnel fet, pp 1–5

Singh P, Yadav DS (2021) Design and investigation of f-shaped tunnel fet with enhanced analog/rf parameters. Silicon

Nigam K, Sharma D et al (2016) Approach for ambipolar behaviour suppression in tunnel fet by workfunction engineering. Micro & Nano Letters 11(8):460–464

Boucart K, Ionescu AM (2007) Double-gate tunnel fet with high-k gate dielectric. IEEE Transactions on Electron Devices 54(7):1725–1733

Vijayvargiya V, Vishvakarma SK (2014) Effect of drain doping profile on double-gate tunnel field-effect transistor and its influence on device rf performance. IEEE Transactions on Nanotechnology 13(5):974–981

Yadav DS, Sharma D, Sharma DG, Bajpai S (2018) High frequency analysis of gaasp/insb hetero-junction double gate tunnel field effect transistor, pp 1–6

Sharma R, Yadav DS, Kumar S, Parmar N, Saraswat S, Kumar A (2020) Novel perspective approach to improve performance of nanowire tfet, pp 1–6

Singh P, Yadav DS (2021) Impactful study of f-shaped tunnel fet. Silicon

Kumar S, Yadav DS, Saraswat S, Parmar N, Sharma R, Kumar A (2020) A novel step-channel tfet for better subthreshold swing and improved analog/rf characteristics, pp 1–6

Pala M, Esseni D, Conzatti F (2012) Impact of interface traps on the iv curves of inas tunnel-fets and mosfets: a full quantum study, pp 6–6

Pandey CK, Singh A, Chaudhury S (2019) Analysis of interface trap charges on dielectric pocket soi-tfet, pp 337–340

Qiu Y, Wang R, Huang Q, Huang R (2014) A comparative study on the impacts of interface traps on tunneling fet and mosfet. IEEE Transactions on Electron Devices 61(5):1284–1291

Madan J, Chaujar R (2016) Interfacial charge analysis of heterogeneous gate dielectric-gate all around-tunnel fet for improved device reliability. IEEE Transactions on Device and Materials Reliability 16(2):227–234

Chandan BV, Nigam K, Sharma D, Pandey S (2018) Impact of interface trap charges on dopingless tunnel fet for enhancement of linearity characteristics. Applied Physics A 124(7):503

Nepusz T, Petróczi A, Négyessy L, Bazsó F (2005) A novel concept for field-effect transistors-the tunneling carbon nanotube fet 1:153–156

Chien ND, Shih C-H (2017) Oxide thickness-dependent effects of source doping profile on the performance of single-and double-gate tunnel field-effect transistors. Superlattices and Microstructures 102:284–299

Boucart K, Ionescu AM (2007) Length scaling of the double gate tunnel fet with a high-k gate dielectric. Solid-State Electronics 51(11–12):1500–1507

Joseph HB, Singh SK, Hariharan R, Tarauni Y, Thiruvadigal DJ (2019) Simulation study of gated nanowire inas/si hetero p channel tfet and effects of interface trap. Materials Science in Semiconductor Processing 103:104605

Buchanan DA (1999) Scaling the gate dielectric: Materials, integration, and reliability. IBM Journal of Research and Development 43(3):245–264

Raad BR, Sharma D, Kondekar P, Nigam K, Yadav DS (2016) Drain work function engineered doping-less charge plasma tfet for ambipolar suppression and rf performance improvement: a proposal, design, and investigation 63(10):3950–3957

Ranjan R, Pradhan K, Sahu P et al (2016) A comprehensive investigation of silicon film thickness (t si) of nanoscale dg tfet for low power applications. Advances in Natural Sciences: Nanoscience and Nanotechnology 7(3):035009

Yadav DS, Sharma D, Tirkey S, Sharma DG, Bajpai S, Soni D, Yadav S, Aslam M, Sharma N (2018) Hetero-material cptfet with high-frequency and linearity analysis for ultra-low power applications. Micro & Nano Letters 13(11):1609–1614

Kumar S, Yadav DS (2021) Temperature analysis on electrostatics performance parameters of dual metal gate step channel tfet. Applied Physics A 127(5):1–11

Sze SM (2008) Semiconductor devices: physics and technology. Wiley

Chander S, Sinha SK, Kumar S, Singh PK, Baral K, Singh K, Jit S (2017) Temperature analysis of ge/si heterojunction soi-tunnel fet. Superlattices and Microstructures 110:162–170

Yadav DS, Sharma D, Tirkey S, Bajaj S (2018) A systematic investigation of the integrated effects of gate underlapping, dual work functionality and hetero gate dielectric for improved performance of cp tfets. Journal of Computational Electronics 17(1):118–128

Kranti A, Armstrong GA (2010) Nonclassical channel design in mosfets for improving ota gain-bandwidth trade-off. IEEE Transactions on Circuits and Systems I: Regular Papers 57(12):3048–3054

Singh P, Yadav DS (2021) Impact of temperature on analog/rf, linearity and reliability performance metrics of tunnel fet with ultra-thin source region. Applied Physics A 127(9):1–15

Aslam M, Sharma D, Soni D, Yadav S, Raad BR, Yadav DS, Sharma N (2018) Effective design technique for improvement of electrostatics behaviour of dopingless tfet: proposal, investigation and optimisation. Micro & Nano Letters 13(10):1480–1485

Verma PK, Gupta SK (2020) Proposal of charge plasma based recessed source/drain dopingless junctionless transistor and its linearity distortion analysis for circuit applications. Silicon 13:1–28

Musalgaonkar G, Sahay S, Saxena RS, Kumar MJ (2019) Nanotube tunneling fet with a core source for ultrasteep subthreshold swing: a simulation study. IEEE Transactions on Electron Devices 66(10):4425–4432

Kim JH, Kim HW, Kim G, Kim S, Park B-G (2016) Demonstration of l-shaped tunnel field-effect transistors ieee trans. Electron Devices 63:1774–1778

Ko E, Lee H, Park J-D, Shin C (2016) Vertical tunnel fet: design optimization with triple metal-gate layers. IEEE Transactions on Electron Devices 63(12):5030–5035

Acknowledgements

The authors would like to thank Dr. Dip Prakash Samajdar from Department of Electronics and Communication Engineering, PDPM Indian Institute of Information Technology, Design & Manufacturing, Jabalpur, Madhya Pradesh, India for providing valuable suggestions and support to carry out this research work.

Funding

Not applicable.

Author information

Authors and Affiliations

Contributions

Sachin Kumar: Conceptualization, data curation, formal analysis, methodology, investigation, writing - original draft. Dharmendra Singh Yadav: Supervision, validation, visualization, writing - review & editing.

Ethics declarations

The manuscript follows all the ethical standards, including plagiarism.

Conflict of interest

No conflicts of interest.

Consent for Publication

Yes.

Consent to Participate

Yes.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Kumar, S., Yadav, D.S. Assessment of Interface Trap Charges on Proposed TFET for Low Power High-Frequency Application. Silicon 14, 9291–9304 (2022). https://doi.org/10.1007/s12633-021-01616-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01616-0