Abstract

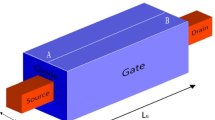

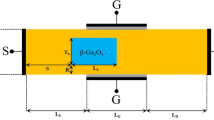

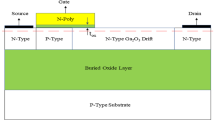

In this paper, we present a solution for understanding volume depletion and essentially decreasing the leakage current of β-Ga2O3 junctionless FETs (βJL-FETs) by embedding the 4H-SiC layer into the BOX layer (βESJL-FET). Using the silvaco simulator with 2-D simulations, we illustrate that the βESJL-FET with an embedded 4H-SiC layer shows a very high ION/IOFF ratio of ~1012 even for a 40 nm channel length. The main idea of this work focuses on changing the volume depletion for achieving a lower leakage current. Also, the other goal is obtaining the lower self-heating effect provided by replacing 4H-SiC with a higher thermal conductivity into the BOX layer. Although the silicon FETs are more applicable but, due to better performance at the ultra-scaled dimensions, we propose the β-Ga2O3 instead of silicon. Ga2O3 has a higher effective mass and lower bond distance than silicon and is suitable for short-channel devices.

Similar content being viewed by others

Data Availability

This manuscript has associated data in a data repository. [Authors’ comment: The data that support the findings of this study are available from the corresponding author, upon reasonable request.].

References

Lenka AS, Mishra SS, Mishra SS, Bhanja U, Mishra GP (2017) An extensive investigation of work function modulated trapezoidal recessed channel MOSFET. Superlattice Microst 111:878–888

Gola D, Singh B, Tiwari PK (2019) Subthreshold Characteristic Analysis and Models for Tri-Gate SOI MOSFETs Using Substrate Bias Induced Effects. IEEE Trans Nanotechnol 18:329–335. https://doi.org/10.1109/TNANO.2019.2906567

Wei S, Zhang G, Shao Z, Geng L, Yang CF (Oct. 2018) Analysis of a high-performance ultra-thin body ultra-thin box silicon-on-insulator MOSFET with the lateral dual-gates: featuring the suppression of the DIBL. Microsyst Technol 24(10):3949–3956. https://doi.org/10.1007/s00542-017-3532-4

Madadi D, Orouji AA, Abbasi A (2020) Improvement of nanoscale SOI MOSFET heating effects by vertical Gaussian drain-source doping region. Silicon 13:645–651. https://doi.org/10.1007/s12633-020-00453-x

Madadi D, Orouji AA (2020) Investigation of Short Channel Effects in SOI MOSFET with 20 nm Channel Length by a β -Ga 2 O 3 Layer. ECS J Solid State Sci Technol 9(4):045002. https://doi.org/10.1149/2162-8777/ab878b

Anvarifard MK, Orouji AA (Dec. 2015) Evidence for enhanced reliability in a novel nanoscale partially-depleted SOI MOSFET. IEEE Trans Device Mater Reliab 15(4):536–542. https://doi.org/10.1109/TDMR.2014.2328583

Anvarifard MK, Ramezani Z, Amiri IS, Nejad AM (Mar. 2020) A nanoscale-modified band energy junctionless transistor with considerable progress on the electrical and frequency issue. Mater Sci Semicond Process 107:104849. https://doi.org/10.1016/j.mssp.2019.104849

Singh J, Jain AK, Kumar MJ (2019) Realizing a planar 4H-SiC Junctionless FET for Sub-10-nm regime using P+ pocket. IEEE Trans Electron Devices 66(7):3209–3214. https://doi.org/10.1109/TED.2019.2914633

Rout SP, Dutta P (2020) Impact of high mobility III-V compound material of a short channel thin-film SiGe double gate junctionless MOSFET as a source. Eng Reports 2(1):1–13. https://doi.org/10.1002/eng2.12086

Rudenko T, Nazarov A, Yu R, Barraud S, Cherkaoui K, Razavi P, Fagas G (2013) Electron mobility in heavily doped junctionless nanowire SOI MOSFETs. Microelectron Eng 109:326–329. https://doi.org/10.1016/j.mee.2013.03.050

Duarte JP, Choi S-J, Moon D-I, Choi Y-K (2011) Simple analytical bulk current model for Long-Channel double-gate Junctionless transistors. IEEE Electron Device Lett 32(6):704–706. https://doi.org/10.1109/LED.2011.2127441

Wang T, Lou L, Lee C (2013) A junctionless gate-all-around silicon nanowire FET of high linearity and its potential applications. IEEE Electron Device Lett 34(4):478–480. https://doi.org/10.1109/LED.2013.2244056

Madadi D, Orouji AA (2021) Scattering mechanisms in β-Ga2O3 junctionless SOI MOSFET: investigation of electron mobility and short channel effects. Mater Today Commun 26:102044. https://doi.org/10.1016/j.mtcomm.2021.102044

Madadi D, Orouji AA (Mar. 2021) beta-Ga2O3 Double Gate Junctionless FET with an Efficient Volume Depletion Region, [Online]. Available: https://arxiv.org/abs/2103.13022 Accessed 25 Mar 2021

Singh J, Kumar MJ (2017) A planar Junctionless FET using SiC with reduced impact of Interface traps: proposal and analysis. IEEE Trans Electron Devices 64(11):4430–4434. https://doi.org/10.1109/TED.2017.2752227

Jazaeri F, Barbut L, Koukab A, Sallese J-M (2013) Analytical model for ultra-thin body junctionless symmetric double gate MOSFETs in subthreshold regime. Solid State Electron 82:103–110. https://doi.org/10.1016/j.sse.2013.02.001

Jazaeri F, Sallese J-M (2018) Modeling nanowire and double-gate. Junctionless field-effect transistors. Cambridge University Press. https://doi.org/10.1017/9781316676899

Sallese JM, Chevillon N, Lallement C, Iñiguez B, Prégaldiny F (2011) Charge-based modeling of junctionless double-gate field-effect transistors. IEEE Trans Electron Devices 58(8):2628–2637. https://doi.org/10.1109/TED.2011.2156413

Madadi D, Orouji AA (2021) Investigation of tied double gate 4H–SiC junctionless FET in 7 nm channel length with a symmetrical dual p+ layer. Phys E Low-dimensional Syst Nanostructures 126:114450. https://doi.org/10.1016/j.physe.2020.114450

Lee C-W, Afzalian A, Akhavan ND, Yan R, Ferain I, Colinge J-P (2009) Junctionless multigate field-effect transistor. Appl Phys Lett 94(5):053511. https://doi.org/10.1063/1.3079411

Liu TY, Pan FM, Sheu JT (2015) Characteristics of gate-all-around junctionless polysilicon nanowire transistors with twin 20-nm gates. IEEE J Electron Devices Soc 3(5):405–409. https://doi.org/10.1109/JEDS.2015.2441736

Il Moon D, Choi SJ, Duarte JP, Choi YK (2013) Investigation of silicon nanowire gate-all-around junctionless transistors built on a bulk substrate. IEEE Trans Electron Devices 60(4):1355–1360. https://doi.org/10.1109/TED.2013.2247763

Madadi D, Orouji AA (2021) Investigation of 4H-SiC gate-all-around cylindrical nanowire junctionless MOSFET including negative capacitance and quantum confinements. Eur Phys J Plus 136(7):785. https://doi.org/10.1140/epjp/s13360-021-01787-0

Madadi D, Orouji AA (2021) A β –Ga2O3 MESFET to amend the carrier distribution by using a tunnel diode. IEEE Trans Device Mater Reliab 21(1):26–32. https://doi.org/10.1109/TDMR.2020.3046530

Madadi D, Orouji AA (2020) New high-voltage and high-speed β-Ga2O3 MESFET with amended electric field distribution by an insulator layer. Eur Phys J Plus 135(7):578. https://doi.org/10.1140/epjp/s13360-020-00523-4

Saeidi A, Jazaeri F, Stolichnov I, Ionescu AM (Dec. 2016) Double-gate negative-capacitance MOSFET with PZT gate-stack on ultra thin body SOI: an experimentally calibrated simulation study of Device performance. IEEE Trans Electron Devices 63(12):4678–4684. https://doi.org/10.1109/TED.2016.2616035

Wan J, Le Royer C, Zaslavsky A, Cristoloveanu S (2011) Gate-induced drain leakage in FD-SOI devices: What the TFET teaches us about the MOSFET. Microelectron Eng 88(7):1301–1304. https://doi.org/10.1016/j.mee.2011.03.092

Rassekh A, Fathipour M (2020) A single-gate SOI nanosheet junctionless transistor at 10-nm gate length: design guidelines and comparison with the conventional SOI FinFET. J Comput Electron, no. 0123456789 19:631–639. https://doi.org/10.1007/s10825-020-01475-9

Orouji AA, Rahimifar A, Jozi M (2016) A novel double-gate SOI MOSFET to improve the floating body effect by dual SiGe trench. J Comput Electron 15(2):537–544. https://doi.org/10.1007/s10825-016-0801-x

Karbalaei M, Dideban D (Feb. 2016) A novel silicon on insulator MOSFET with an embedded heat pass path and source side channel doping. Superlattice Microst 90:53–67. https://doi.org/10.1016/j.spmi.2015.12.001

Sreenivasulu VB, Narendar V (Oct. 2021) Characterization and optimization of junctionless gate-all-around vertically stacked nanowire FETs for sub-5 nm technology nodes. Microelectron J 116:105214. https://doi.org/10.1016/j.mejo.2021.105214

Sreenivasulu VB, Narendar V (2021) Design insights into RF/analog and linearity/distortion of spacer engineered multi-fin SOI FET for terahertz applications. Int J RF Microw Comput Eng. https://doi.org/10.1002/mmce.22875

Karbalaei M, Dideban D, Heidari H (Dec. 2019) Improvement in electrical characteristics of silicon on insulator (SOI) transistor using graphene material. Results Phys 15:102806. https://doi.org/10.1016/j.rinp.2019.102806

Liddy KJ et al (2019) Thin channel β -Ga 2 O 3 MOSFETs with self-aligned refractory metal gates. Appl Phys Express 12(12):126501. https://doi.org/10.7567/1882-0786/ab4d1c

Higashiwaki M et al (2013) Depletion-mode Ga 2 O 3 metal-oxide-semiconductor field-effect transistors on β-Ga 2 O 3 (010) substrates and temperature dependence of their device characteristics. Appl Phys Lett 103(12):123511. https://doi.org/10.1063/1.4821858

Masten HN, Phillips JD, Peterson RL (2019) Ternary alloy rare-earth Scandate as dielectric for $\beta$ -Ga 2 O 3 MOS structures. IEEE Trans Electron Devices 66(6):2489–2495. https://doi.org/10.1109/TED.2019.2911237

Moser NA et al (2017) High pulsed current density β -Ga 2 O 3 MOSFETs verified by an analytical model corrected for interface charge. Appl Phys Lett 110(14):143505. https://doi.org/10.1063/1.4979789

Higashiwaki M, Sasaki K, Kuramata A, Masui T, Yamakoshi S (2012) Gallium oxide (Ga 2O 3) metal-semiconductor field-effect transistors on single-crystal β-Ga 2O 3 (010) substrates. Appl Phys Lett 100(1):2010–2013. https://doi.org/10.1063/1.3674287

Qin Y, Dong H, Long S, He Q, Jian G, Zhang Y, Zhou X, Yu Y, Hou X, Tan P, Zhang Z, Liu Q, Lv H, Liu M (2019) Enhancement-mode β-Ga2O3 metal-oxide-semiconductor field-effect solar-blind phototransistor with ultrahigh Detectivity and photo-to-dark current ratio. IEEE Electron Device Lett 40(5):742–745. https://doi.org/10.1109/LED.2019.2908948

Lv Y, Zhou X, Long S, Wang Y, Song X, Zhou X, Xu G, Liang S, Feng Z, Cai S, Fu X, Pu A, Liu M (2020) Enhancement-Mode β -Ga 2 O 3 Metal-Oxide-Semiconductor Field-Effect Transistor with High Breakdown Voltage over 3000 V Realized by Oxygen Annealing. Phys Status Solidi Rapid Res Lett 14(3):1900586. https://doi.org/10.1002/pssr.201900586

McCluskey MD (2020) Point defects in Ga2O3. J Appl Phys 127(10). https://doi.org/10.1063/1.5142195

Mun JK, Cho K, Chang W, Jung HW, Do J (2019) 2.32 kV breakdown voltage lateral β-Ga2O3 MOSFETs with source-connected field plate. ECS J Solid State Sci Technol 8(7):Q3079–Q3082. https://doi.org/10.1149/2.0151907jss

Lv Y, Zhou X, Long S, Liang S, Song X, Zhou X, Dong H, Wang Y, Feng Z, Cai S (2019) Lateral source field-plated β-Ga2O3 MOSFET with recorded breakdown voltage of 2360 v and low specific on-resistance of 560 mΩ cm2. Semicond Sci Technol 34(11):2–6. https://doi.org/10.1088/1361-6641/ab4214

Frodason YK, Zimmermann C, Verhoeven EF, Weiser PM, Vines L, Varley JB (2021) Multistability of isolated and hydrogenated Ga–O divacancies in β Ga2O3. Phys Rev Mater 5(2):025402. https://doi.org/10.1103/PhysRevMaterials.5.025402

Oh J, Ma J, Yoo G (2019) Simulation study of reduced self-heating in β-Ga2O3 MOSFET on a nano-crystalline diamond substrate. Results Phys 13, no. February:102151. https://doi.org/10.1016/j.rinp.2019.02.087

Karsthof R, Bathen ME, Galeckas A, Vines L (2020) Conversion pathways of primary defects by annealing in proton-irradiated n type 4H -SiC. Phys Rev B 102(18):184111. https://doi.org/10.1103/PhysRevB.102.184111

Zeng K, Jia Y, Singisetti U (2016) Interface state density in atomic layer deposited SiO2/β-Ga2O3 (̅201) MOSCAPs. IEEE Electron Device Lett 37(7):906–909. https://doi.org/10.1109/LED.2016.2570521

Ma J, Cho HJ, Heo J, Kim S, Yoo G (2019) Asymmetric double-gate β-Ga2O3 Nanomembrane field-effect transistor for energy-efficient power devices. Adv Electron Mater 5(6):1–7. https://doi.org/10.1002/aelm.201800938

Device Simulator ATLAS, “Silvaco International.” Santa Clara 〈www.silvaco.com〉, 2015

Razavi P, Fagas G (2013) Electrical performance of III-V gate-all-around nanowire transistors. Appl Phys Lett 103(6):063506. https://doi.org/10.1063/1.4817997

Acknowledgements

Not applicable.

Funding

No funding to declare.

Author information

Authors and Affiliations

Contributions

All of the authors contributed to the idea, simulation of the research, the analysis of the results, and the writing of the manuscript.

Corresponding author

Ethics declarations

Ethics Approval and Consent to Participate

Not applicable.

Consent for Publication

Not applicable.

Competing Interests

The authors declare that they have no conflict of interest.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Madadi, D. β-Ga2O3 Junctionless FET with an Ω Shape 4H-SiC Region in Accumulation Mode. Silicon 14, 7595–7602 (2022). https://doi.org/10.1007/s12633-021-01510-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01510-9