Abstract

An inspiring UTBB SOI MOSFET structure with enhanced immunity to the drain-induced barrier lowering (DIBL) is analyzed. The structure includes the dual-gates in the lateral direction. The voltage difference is applied between the dual-gates, through which the electrostatic potential and the energy band along the channel are modified and the electrical performance is boosted. The electrical characteristics are investigated by measuring the electron concentration, the conduction band energy level, and the potential at the front-surface. The impact of the negative voltage bias applied to the right gate on the performance of the new device is studied, and compared to that of the conventional ultra-thin body ultra-thin box silicon-on-insulator (UTBB SOI) devices. The results reveal that the undesirable DIBL values are lower in this innovative device than that in the conventional UTBB SOI MOSFET.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The ultra-thin body ultra-thin box (UTBB) SOI MOSFET with the lightly-doped channel is demonstrating a high advantage for ultimate MOSFET scaling because of its dramatic suppression of short-channel effects (SCEs) (Young 1989; Grenouillet et al. 2013), and its superiority of low-power high-speed application (Haond 2014; Stephane and Thomas 2016). The SCEs, which mainly includes the threshold voltage roll-off, the drain induced barrier lowering (DIBL), and the subthreshold swing degradation, is the major barrier for MOSFET downscaling. Therefore, based on the UTBB SOI technology, a number of methods have been proposed to further reduce the SCEs, by employing the channel engineering, the source/drain engineering (Yamada et al. 2013b, c; Srivastava et al. 2016), the back-biasing technique (Burignat et al. 2010; Karatsori et al. 2015), the thickness modulation of the buried oxide layer (Yamada et al. 2013a), and the gate voltage difference engineering (Anvarifard et al. 2009; Anvarifard and Orouji 2013; Lahgere et al. 2015).

The DIBL characterizes the physical phenomena that in the short channel devices operating in the subthreshold region, the potential barrier between the source and the channel is lowered because of the bias voltage applied to drain. And it causes excess carriers injecting into the channel and resulting in an increased subthreshold current. The DIBL can be evaluated as the gate threshold voltage shift due to the drain voltage variation (Colinge and Colinge 2002; Arshad et al. 2012; Mutlu and Rahman 2000). Based on the innovative concept of the lateral dual-gates to shield the drain voltage and reduce the DIBL, in this paper, the carrier density, the energy band, and the potential along the channel are investigated quantitatively. Moreover, the resultant magnitude of the DIBL, by setting the optimum voltage difference on the dual-gates, is compared to that of a conventional UTBB SOI device. Then, the impact of the negative voltage bias of the right gate (Gate_Control) on the DIBL is explained, in the scenario of the UTBB MOSFET with a lightly-doped silicon film. And the channel length is 22–46 nm. The results of this work are instructive for design and application of the novel UTBB SOI devices.

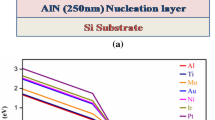

2 Proposed device

The schematic cross-sectional view of a n-channel UTBB SOI MOSFET with the lateral dual-gates for modeling and simulation is shown in Fig. 1. The x- and y-axes of the 2D structure are taken along the source-channel and gate-to-gate-oxide interfaces, respectively. The two poly-gates are named as Gate_Main and Gate_Control, respectively. And there is a small gap between the gates, which is filled by SiO2. In this work, the total channel length is 22–46 nm. The lengths of the Gate_Main and the Gate_Control are equal. The length of the small gap is set to be the constant 2 nm. The lengths of the Gate_Main, the Gate_Control, and the split are denoted by L M , L C , L S , respectively. That is, L M = L C , and L S = 2 nm. V G_M and V G_C are the voltage biases applied to the Gate_Main and the Gate_Control, accordingly. Their voltage difference is named as V diff . It is concluded from this study that when Gate_Main dominates the device to work in the subthreshold region, the negative offset voltage on the Gate_Control can play an important role in reducing the DIBL. And the simulation results from Synopsys TCAD have been thoroughly analyzed. The symbols (t oxf , t si , t oxb , t sub , and x d ) used in Fig. 1 are the thicknesses of the gate-oxide, silicon film, buried-oxide, substrate, and depletion region in the substrate, respectively. V D , V S , and V Sub are the bias voltages applied to the drain, the source, and the substrate, respectively. The source voltage V S is connected to the ground, so V Sub is also called as V BS . And ’ Sub is the potential at the substrate/buried-oxide interface. The typical parameters are summarized in Table 1.

To analyze the impact of voltage difference engineering on electrical performance, it is essential to compare the new structure with the conventional UTBB SOI structure with the same dimensional parameters, doping concentration, according to Table 1. For the new device, the voltage on the Gate_Main is defined as threshold voltage. For both the new and the conventional structures, the threshold voltage values are extracted from numerical simulation outputs by industrial standard linear-extrapolation techniques, in which V TH is obtained by linearly extrapolating the Id-versus-Vg characteristics to the Vg-axis at some small V DS (Krutsick et al. 1987).

3 Analysis of electrical characteristics

Figure 2 shows the electron concentration along the front-channel of both structures in a log scale with different V G_C , at the constant V G_M = 1.2 V, V DS = 1.2 V, and V sub = 0 V. And the gate voltage of the conventional UTBB SOI device is also set to the constant 1.2 V. In spite of no direct voltage bias on the gap, it is observed that the electron concentration under the gap is none-zero under all dependent voltage difference conditions. And the electron concentrations under the gap and the interfaces of the two different gates are continuous. The electron concentration below the Gate_Control with the various V G_C bias condition is always smaller than that for the conventional UTBB SOI structure. And the electron concentration below the Gate_Control decreases rapidly and greatly from 1019 to 108 cm−3 when V G_C reducing from 1.2 to −1.2 V. Figure 3 exhibits the electron concentration along the front-channel of the new structure in a log scale with the different V DS . In Fig. 3, V G_M is 0.5 V, and V G_C is −1.2 V. No matter V DS is 0.5 or 1.4 V, the surface electron concentrations beneath the gap and the Gate_Control all drop sharply. And the value of electron concentrations beneath the Gate_Control for V DS = 0.5 V and V DS = 1.4 V are quite close. So it can be deduced that the deep negative V G_C can shielded the impact of V DS ’ increment.

Corresponding to the surface charge in Figs. 2 and 3, the variation of the conduction band energy along the front-surface under different voltages are shown in Figs. 4 and 5. Some common characters are observed from Figs. 4 and 5 that the conduction band is bent to go up in the middle under the gap and the Gate_Control. Because the states of the carrier (in the accumulation, the depletion, or the inversion) beneath the gap and the Gate_Control are inconsistent with the state created by V G_M beneath the Gate_Main. The variation of conduction band energy along the front-channel of both structures with the different V G_C , at the constant V DS of 1.2 V and V G_M of 1.2 V, is shown in Fig. 4. It can be seen that with V G_C gradually decreasing from 1.2 to −1.2 V, the conduction band beneath the Gate_Control moves gradually away from the Fermi level, as the electron concentration gradually decreases in the right channel region, which leads to a greater degree of curvature for the conduction band under the Gate_Control. Then, the variation of conduction band energy along the front-channel for the new structure with the different V DS , at the constant V G_M and V G_C , is shown in Fig. 5, in which situation V G_M is just a little higher than the threshold voltage, whereas the deep minus V G_C is much smaller than the threshold voltage. It is observed that even though the varying V DS can affect conduction band at any position along the channel, and can adjust the steepness of the gradients of the bending for the conduction band, there are still the uphill curves from the start of the gap towards the middle area beneath the Gate_Control, which can in turn exert great resistance for the electron moving to the drain.

In same voltage bias scenario as in Figs. 5 and 6 characteristics the variation of the front-surface potential as the function of the position along channel with different V DS . And the front-surface potential distribution just under the gap, which is part of Fig. 6, is zoomed-into further highlight in Fig. 7. As shown in Fig. 6, the potential variation under Gate_Main, especially the difference of the potentials at the source/channel interface is tiny enough to be ignored under various biases on V DS . Because the deep minus voltage on Gate_Control can make the drain voltage’s influence become less on the left side of the channel. Also as highlighted in Fig. 7, the front-surface potential distribution under the gap is a linear function. Moreover, in the case of different V DS , the linear slope can be considered approximately equal. Other than a step function of front-surface potential proposed by (Anvarifard et al. 2009), we observed from Fig. 6 that the front-surface potential is a continuous function. The channel can be divided into three regions, namely, Channel_Main, Channel_Gap, and Channel_Control. Either the Channel_Main or the Channel_Control is controlled by its corresponding gate. The surface potentials of the Channel_Main and Channel_Control all fit with the parabolic approximation theory (Young 1989; Suzuki and Pidin 2003), but with different curvature. In addition, it is observed from Fig. 7 that surface potential of the Channel_Gap is a linear function. And the boundary surface potential values at the interfaces of Gate_Main to gap, and Gate_Control to gap are continuous without the mutation point.

Then, Fig. 8 gives further comparison of the horizontal potential along the front-surface, the back-surface, and 2 nm below the front-surface for the proposed structure. Then the horizontal potential distribution just under the gap, which is part of Fig. 8, is zoomed-into highlight in Fig. 9. It is different from the front-surface potential mainly controlled by the lateral dual-gates on the topside that the back-surface potential is mainly controlled by the continuous substrate voltage. Thus, the back-surface potential is one single parabolic. From the front-surface to the back-surface perpendicularly, the influence of the top lateral dual-gates on the potential distribution inside the silicon film gradually decreases. Just as highlighted in Fig. 9, along the boundary of the gap, the potential values at front-surface, the back-surface, and 2 nm below the front-surface are different. And the slopes of the potential distributions beneath the gap are also different. As a result, the vertical potential distributions along the edges of the gap inside the silicon film are changing with an unfix trend, according to the various front/back voltage coupling conditions.

To exemplify the impact of Gate_Control on the channel current, in Fig. 10, we examine the I DS -versus-V G_M characteristic in V G_C = −1.2 V, and compare it to the normal I DS -versus-V GS curve of the conventional UTBB SOI device. The currents are in log scale in Fig. 10. The conclusion drawn from Fig. 10 is consistent with the conclusion from the previous diagrams of the conduction band energy and the potential that with higher energy barrier introduced by V G_C , the drain current of the new device is less in all states than that of the conventional device. Therefore, this feature can be optimally explored in the standby mode to achieve as low dissipation power as possible by setting the V G_C to be far below the threshold voltage. In this work, in the discussions of the threshold roll-off in Fig. 11 and the DIBL in Figs. 12, 13, and 14, V G_C is set to be −1.2 V, which is negative of the 1.2 V power supply. And all the threshold voltage values of the novel device are extracted from the I DS -versus-V G_M curves under such V G_C bias.

The threshold voltage roll-off as a function of channel length is depicted and compared to the conventional UTBB SOI device in Fig. 11. It is observed as the channel length shrinks, the threshold voltage decreases for either the new or the conventional devices. But the unique shielding drain voltage feature of the negative V G_C permits the tuning of threshold voltage for a considerable range of channel length under the nanometer region for the new structure. As a result, the shrinking of the channel length gives an exponential roll-off behavior (Shee et al. 2014) for the conventional device. Comparatively, the threshold is higher in every channel length node for the new device. And the trend of threshold voltage roll-off with the channel length decrease is slower for the new device. This is another superior of the new structure over the conventional UTBB SOI structure.

Figures 12, 13 and 14 analyze the extracted DIBL values under the different conditions. The magnitude of DIBL (in mV/V) is defined as the gate threshold voltage shift due to a drain voltage variation between the linear voltage (V DS1 = 0.05 V) and the saturation voltage (V DS2 = 1.2 V) (Colinge and Colinge 2002; Singh et al. 2017). In Eq. (1), V TH_LINEAR is the linear threshold voltage, and V TH_SATURATE is the saturation threshold voltage:

The comparison of the DIBL’s variation as the function of the channel length for the proposed structure to that for the conventional UTBB SOI device is shown in Fig. 12. And the analyses for the new devices are in case that V G_C = −1.2 V. It is observed that DIBL values for either the new or the conventional devices become higher with the channel length shrinking. But the tendency of the DIBL’s increment for the new device is slower. And it is clear that the new device globally possesses the lower DIBL values in every channel length node than the conventional devices. Therefore, the capability of suppressing the DIBL is much more enhanced in the new devices. Then the comparison of the variation of the DIBL as the function of V G_C for the proposed new structure with different channel length is plotted in Fig. 13. The trends in Fig. 13 are well aligned with the conclusions shown in Fig. 2 and 4. First of all, the negative voltage offset on Gate_Control can raise the energy barrier along the channel to the drain. As a result, the impacts of the V DS on both the source/channel’s conduction band and the channel electrons are partially blocked. Under such a function, as V G_C becomes even negative, the effect of shielding is more obvious. As a result, for the new structure device, the DIBL value decreases with V G_C decrease. Moreover, with the same V G_C , the DIBL for 28 nm is smaller than that for 22 nm. When V DS = 0.05 V, the threshold voltage on Gate_Main is 0.16 V for L = 28 nm, and 0.13 V for L = 22 nm, respectively. It can be concluded from Fig. 13 that for the 1.2 V power supply design, the optimal gate voltage difference is: V G_M = 0 V, V G_C = −1.2 V (which does not need to introduce the charge pump to further decrease the negative voltage on V G_C ). Under these circumstances, the new device works in the subthreshold region, the variation of drain voltage is shielded by V G_C to a greater degree, and the DIBL is minimized. Figure 14 compares of the variation of DIBL as the function of V Sub for the proposed structure with different V G_C to that for the conventional device. It is seen that as the new structure having the lateral dual-gates only on the top, the effect of Gate_Control’s shielding influence of V DS is smaller toward the back-surface. Thus, with the increscent V Sub , the back channel current enlarges gradually, and the DIBL enlarges accordingly for both the conventional device and the new device. Nevertheless, with the negative Gate_Control, the variation of the DIBL as the function of V Sub is still lower than that of the conventional device. Therefore, the lateral voltage difference of the dual-gates on the topside also has the capability to dynamically alleviate the impact of substrate voltage on the DIBL, to a certain extent.

4 Conclusion

In this paper, we have demonstrated that the specified UTBB SOI structure with the voltage difference on lateral dual-gates is superior to the traditional UTBB SOI device for the diminished DIBL effect. And the negative voltage offset on the right gate (Gate_Control) can weaken the impact of the drain voltage on source/channel interface potential. Therefore, the DIBL is suppressed to a extent. Moreover, a conclusion is drawn from the numerical simulation that despite being controlled by the different gate voltages, the front-surface potential of this UTBB SOI device is a continuous function, rather than a step function proposed by (Anvarifard et al. 2009). This device structure is valid not only for UTBB SOI transistors, but also generally useful for the vertical independent double-gate and gate-all-around devices featuring a lightly-doped channel. At this stage, as the definite boundary conditions along the dual-gates’ gap inside silicon film have not be derived yet, the complete potential distribution model is beyond the scope of this study, and will be developed in near future based on a more reasonable boundary condition approximation along the lateral dual-gates’ gap inside silicon film.

References

Anvarifard MK, Orouji AA (2013) Voltage difference engineering in SOI MOSFETs: a novel side gate device with improved electrical performance. Mater Sci Semicond Process 16:1672–1678. doi:10.1016/j.mssp.2013.05.006

Anvarifard KM, Armaki MG, Hosseini SE (2009) A new transistor of dual-gate SOI and evidence for diminished short channel effects. In: 2009 International conference on emerging trends in electronic and photonic devices & systems (ELECTRO-2009), pp 29–32. doi:10.1109/ELECTRO.2009.5441180

Arshad MKM, Raskin JP, Kilchytsk V (2012) Extended MASTAR modeling of DIBL in UTB and UTBB SOI MOSFETs. IEEE Trans Electron Devices 59:247–251. doi:10.1109/TED.2011.2172993

Burignat S, Flandre D, Arshad MKM et al (2010) Substrate impact on threshold voltage and subthreshold slope of sub-32 nm ultra thin SOI MOSFETs with thin buried oxide and lightly-doped channel. Solid-State Electron 54:213–219. doi:10.1016/j.sse.2009.12.021

Colinge JP, Colinge CA (2002) Physics of semiconductor devices. Kluwer Academic Publishers, New York, Boston, Dordrecht, London, Moscow

Grenouillet L, Liu Q, Wacquez R et al (2013) UTBB FDSOI scaling enablers for the 10 nm node. In: 2013 IEEE SOI-3D-subthreshold microelectronics technology unified conference (S3S), pp 1–2. doi:10.1109/S3S.2013.6716546

Haond M (2014) UTBB/FDSOI: reasons for success. In: 2014 SOI-3D-subthreshold microelectronics technology unified conference (S3S), pp 1–2. doi:10.1109/S3S.2014.7028212

Karatsori TA, Tsormpatzoglou A, Theodorous CG et al (2015) Analytical compact model for lightly-doped nanoscale ultrathin-body and box SOI MOSFETs with back-gate control. IEEE Trans Electron Devices 62:3117–3124. doi:10.1109/TED.2015.2464076

Krutsick TJ, White MH, Wong HS et al (1987) An improved method of MOSFET modeling and parameter extraction. IEEE Trans Electron Devices 34:1676–1680. doi:10.1109/T-ED.1987.23136

Lahgere A, Sahu C, Singh J (2015) Electrically doped dynamically configurable field-effect transistor for low-power and high-performance applications. Electron Lett 51:1284–1286. doi:10.1049/el.2015.0079

Mutlu AA, Rahman M (2000) Two-dimensional analytical model for drain induced barrier lowering (DIBL) in short channel MOSFETs. Southeastcon 2000. Proc IEEE 2000:340–344. doi:10.1109/SECON.2000.845589

Shee S, Bhattacharyya G, Dutta PK el al (2014) Threshold voltage roll-off and DIBL model for DMDG SON MOSFET: a quantum study. In: Proceeding of the 2014 IEEE students’ technology symposium, pp 381–385. doi:10.1109/TechSym.2014.6808080

Singh A, Kapoor D, Sharma R (2017) Performance analysis of SiGe double-gate N-MOSFET. J Semicond 38:044003-1-7. doi:10.1088/1674-4926/38/4/044003

Srivastava NA, Mishra VK, Chauhan RK (2016) Analytical modelling of surface potential of modified source FD-SOI MOSFET. In: 2016 International conference on emerging trends in communication technologies (ETCT), pp 1–4. doi:10.1109/ETCT.2016.7882990

Stephane M, Thomas S (2016) UTBB FDSOI: evolution and opportunities. Solid-State Electron 125:63–72. doi:10.1016/j.sse.2016.07.003

Suzuki K, Pidin S (2003) Short-channel single-gate SOI MOSFET model. IEEE Trans Electron Devices 50:1297–1305. doi:10.1109/TED.2003.813450

Yamada T, Abe S, Nakajima Y et al (2013a) Quantitative extraction of electric flux in the buried-oxide layer and investigation of its effects on MOSFET characteristics. IEEE Trans Electron Devices 60:3996–4001. doi:10.1109/TED.2013.2284792

Yamada T, Nakajima Y, Hanajiri T et al (2013b) Suppression of drain-induced barrier lowering in silicon-on-insulator MOSFETs through source/drain engineering for low-operating-power system-on-chip applications. IEEE Trans Electron Devices 60:260–267. doi:10.1109/TED.2012.2225063

Yamada T, Nakajima Y, Hanajiri T et al (2013c) Corrections to “suppression of drain-induced barrier lowering in silicon-on-insulator MOSFETs through source/drain engineering for low-operating-power system-on chip applications”. IEEE Trans Electron Devices 60:4281–4283. doi:10.1109/TED.2013.2286957

Young KK (1989) Short-channel effect in fully depleted SOI MOSFETs. IEEE Trans Electron Devices 36:399–402. doi:10.1109/16.19942

Acknowledgements

This work was supported by the National Natural Science Foundation of China (under Grants 61504047 and 61505068). It was also supported by the Provincial Natural Science Foundation of Fujian, China (under Grants 2016J01313, 2016J05159, and 2015J01265), by the Program for Top Youth Talents in Universities of Fujian Province (TYTFJ 2015), and by the Program for New Century Excellent Talents in University of Fujian Province (NCETFJ 2016).

Author information

Authors and Affiliations

Corresponding authors

Rights and permissions

Open Access This article is distributed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made.

About this article

Cite this article

Wei, S., Zhang, G., Shao, Z. et al. Analysis of a high-performance ultra-thin body ultra-thin box silicon-on-insulator MOSFET with the lateral dual-gates: featuring the suppression of the DIBL. Microsyst Technol 24, 3949–3956 (2018). https://doi.org/10.1007/s00542-017-3532-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00542-017-3532-4