Abstract

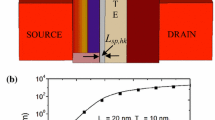

This paper extensively studies the spacer technology, including low-k/high-k, single/dual dielectrics on the device performances focusing on the leakage current. The tactical use of a spacer, introduction of a low bandgap material as a pocket on the source side along with the incorporation of gate dielectrics helped in improving the switching ratio effectively. A systematic comparison is made in between the conventional symmetrical single low-k spacer 3D FinFET and the proposed optimized 3D FinFET. Various device architectures are evaluated by showing significant improvements in on current (Ion) and off state leakage (Ioff), leading to a high switching ratio (Ion/Ioff) and the subthreshold slope (SS). An Ion/Ioff of value 1 × 106 indicates sufficient electrostatics to control over the channel, and our study results in ~8 time of this value. These parameters are obtained after the appropriate selection of low-k & high-k spacer length on both sides of the source and drain. The use of SiGe material near the source side to modulate carrier mobility and incorporating high-k gate dielectric to suppress leakage.

Similar content being viewed by others

References

Chang L et al (2003) Extremely scaled silicon nano-CMOS devices. Proc IEEE 91(11):1860–1873

Shaik RR, Arun G, Chandrasekar L, and Pradhan KP (2020) “A study of Workfunction variation in pocket doped FD-SOI technology towards temperature analysis,” Silicon, pp. 1–10

Collaert N, de Keersgieter A, Dixit A, Ferain I, Lai LS, Lenoble D, Mercha A, Nackaerts A, Pawlak BJ, Rooyackers R, Schulz T, San KT, Son NJ, van Dal MJH, Verheyen P, von Arnim K, Witters L, de Meyer K, Biesemans S, Jurczak M (2008) Multi-gate devices for the 32 nm technology node and beyond. Solid State Electron 52(9):1291–1296

Hisamoto D et al (2000) FinFET-a self-aligned double-gate MOSFET scalable to 20 nm. IEEE Trans. Electron Devices 47(12):2320–2325

Kedzierski J, Meikei Ieong, Nowak E, Kanarsky TS, Ying Zhang, Roy R, Boyd D, Fried D, Wong HSP (2003) Extension and source/drain design for high-performance FinFET devices. IEEE Trans. Electron Devices 50(4):952–958

Auth C et al. (2012) “A 22nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors,” in 2012 symposium on VLSI technology (VLSIT), pp. 131–132

Goud AA, Gupta SK, Choday SH, and Roy K (2013) “Atomistic tight-binding based evaluation of impact of gate underlap on source to drain tunneling in 5 nm gate length Si FinFETs,” in 71st Device Research Conference, pp. 51–52

Yeo Y-C, King T-J, Hu C (2002) Direct tunneling leakage current and scalability of alternative gate dielectrics. Appl Phys Lett 81(11):2091–2093

Mukhopadhyay S, Neau C, Cakici RT, Agarwal A, Kim CH, Roy K (2003) Gate leakage reduction for scaled devices using transistor stacking. IEEE Trans Very Large Scale Integr Syst 11(4):716–730

Sachid AB, Chen M-C, Hu C (2017) Bulk FinFET with low-$$\$kappa $ spacers for continued scaling. IEEE Trans. Electron Devices 64(4):1861–1864

Manoj CR, Sachid AB, Yuan F, Chang C-Y, Rao VR (2009) Impact of fringe capacitance on the performance of nanoscale FinFETs. IEEE electron device Lett 31(1):83–85

Sachid AB, and Hu C (2012) “A little known benefit of FinFET over planar MOSFET in highperformance circuits at advanced technology nodes,” in 2012 IEEE International SOI Conference (SOI), pp. 1–2

Trivedi V, Fossum JG, Chowdhury MM (2004) Nanoscale FinFETs with gate-source/drain underlap. IEEE Trans. Electron Devices 52(1):56–62

Shenoy RS, Saraswat KC (2003) Optimization of extrinsic source/drain resistance in ultrathin body double-gate FETs. IEEE Trans Nanotechnol 2(4):265–270

Fossum JG et al. (2003) “Physical insights on design and modeling of nanoscale FinFETs,” in IEEE International Electron Devices Meeting 2003, pp. 21–29

Goud AA, Venkatesan R, Raghunathan A, and Roy K (2015) “Asymmetric underlapped FinFET based robust SRAM design at 7nm node,” in 2015 Design, Automation & Test in Europe Conference & Exhibition (DATE), pp. 659–664

Akkala AG, Venkatesan R, Raghunathan A, Roy K (2016) Asymmetric underlapped sub-10-nm n-FinFETs for high-speed and low-leakage 6T SRAMs. IEEE Trans. Electron Devices 63(3):1034–1040

Wang TED et al., “Importance of VDIBLSS/(Ion/Ioff) in Evaluating the Performance of n-Channel Bulk FinFET Devices”

Lee ZK, Nemati F, and Robins S (2006) “High ion/Ioff SOI MOSFET using body voltage control.” Google Patents

Mohapatra SK, Pradhan KP, Singh D, Sahu PK (2015) The role of geometry parameters and fin aspect ratio of sub-20nm SOI-FinFET: an analysis towards analog and RF circuit design. IEEE Trans Nanotechnol 14(3):546–554

Pal PK, Kaushik BK, Dasgupta S (2014) Investigation of symmetric dual-k spacer trigate FinFETs from delay perspective. IEEE Trans. Electron Devices 61(11):3579–3585

Sachid AB, Manoj CR, Sharma DK, Rao VR (2007) Gate fringe-induced barrier lowering in underlap FinFET structures and its optimization. IEEE Electron Device Lett 29(1):128–130

Sachid AB et al. (2008) “Sub-20 nm gate length FinFET design: Can high-$κ$ spacers make a difference?,” in 2008 IEEE International Electron Devices Meeting, pp. 1–4

Sachid AB, Chen M-C, Hu C (2016) FinFET with high-$$\$kappa $ spacers for improved drive current. ieee electron device Lett 37(7):835–838

Roy D, Biswas A (2017) Asymmetric underlap spacer layer enabled nanoscale double gate MOSFETs for design of ultra-wideband cascode amplifiers. Superlattice Microst 110:114–125

Nandi A, Saxena AK, Dasgupta S (2014) Enhancing low temperature analog performance of underlap FinFET at scaled gate lengths. IEEE Trans Electron Devices 61(11):3619–3624

Kanungo S, Chattopadhyay S, Gupta PS, Sinha K, Rahaman H (2016) Study and analysis of the effects of SiGe source and pocket-doped channel on sensing performance of dielectrically modulated tunnel FET-based biosensors. IEEE Trans. Electron Devices 63(6):2589–2596

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Samal, A., Pradhan, K.P. & Mohapatra, S.K. Improvising the Switching Ratio through Low-k / High-k Spacer and Dielectric Gate Stack in 3D FinFET - a Simulation Perspective. Silicon 13, 2655–2660 (2021). https://doi.org/10.1007/s12633-020-00618-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-020-00618-8