Abstract

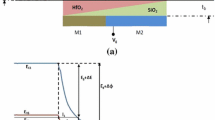

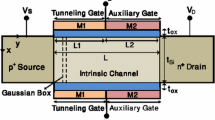

In this paper, we propose and develop an analytical model of a Triple material double gate Tunnel Field Effect Transistor (TM-DG TFET) with hetero-dielectric gate oxide stack comprising of SiO2 and HfO2. The two-dimensional Poisson’s equation has been solved using parabolic-approximation method to model the channel potential and electric field. Analytical model of drain current is developed by integrating the band-to-band tunneling generation rate over the channel thickness (tsi) and shortest tunneling path (\(L_{\min }\)). A Transconductance model is also developed using this drain current model. The proposed TM-DG TFET also provides better result with reference to input-output characteristics, subthreshold swing, ION/IOFF current ratio and ambipolar effect compared to the dual material double gate (DM-DG) TFET. The analytical model has been validated with the numerical data obtained from commercial TCAD software.

Similar content being viewed by others

References

Seabaugh C, Zhang Q (2010) Low-voltage tunnel transistors for beyond CMOS logic. Proc IEEE 98:2095–2110

Koswatta SO, Lundstrom MS, Nikonov DE (2009) Performance comparison between p-i-n tunneling transistors and conventional MOSFETs. IEEE Trans Electron Devices 56:456–465

Toh EH, Wang GH, Samudra G, Yeo YC (2008) Device physics and design of germanium tunneling field-effect transistor with source and drain engineering for low power and high performance applications. J Appl Phys 103:104504–1–104504-5

Kumar MJ, Janardhanan S (2013) Doping-less tunnel field effect transistor: Design and investigation. IEEE Trans Electron Devices 60:3285–3290

Saurabh S, Kumar MJ (2010) Estimation and compensation of process-induced variations in nano scale tunnel field-effect transistors for improved reliability. IEEE Trans Device Mater Rel 10:390–395

Choi WY, Park BG, Lee JD, Liu TJK (2007) Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett 28:743–745

Ionescu AM, Riel H (2011) Tunnel field-effect transistors as energy efficient electronic switches. Nature 479:329–337

(2014) International Technology Roadmap for Semiconductor

Shen C, Ong SL, Heng CH, Samudra G, Yeo YC (2008) A variational approach to the two-dimensional nonlinear Poisson’s equation for the modeling of tunneling transistors. IEEE Electron Device Lett 29:1252–1255

Saurabh S, Kumar MJ (2011) Novel attributes of a dual material gate nanoscale tunnel field-effect transistor. IEEE Trans Electron Devices 58:404–410

Gholizadeh M, Hosseini SE (2014) A 2-D analytical model for doublegate tunnel FETs. IEEE Trans Electron Devices 61:1494–1500

Gowami R, Bhowmick B (2017) An algorithm for extraction of threshold voltage in heterojunction TFETs. IEEE Trans Nanotechnol 16:90–93

Goswami R, Bhowmick B (2018) An analytical model of drain current in a nanoscale circular gate TFET. IEEE Trans Electron Devices 64:45–51

Barah D, Singh AK, Bhowmick B (2018) Silicon. https://doi.org/10.1007/s12633-018-9894-0

Kane EO (1961) Theory of tunneling. J Appl Phys 32:83–91

Kumar S, Goel E, Singh K, Singh B, Kumar M, Jit S (2016) A compact 2-D analytical model for electrical characteristics of double gate TFETs with SiO2/High-K stacked gate oxide structure. IEEE Trans Electron Devices 63:3291–3299

Kumar S, Goel E, Singh K, Singh B, Singh PK, Baral K, Jit S (2017) 2-D analytical modeling of the electrical characteristics of dual-material double-gate TFETs with a SiO 2/HfO 2 stacked gate-oxide structure. IEEE Trans Electron Devices 64:960–968

Bagga N, Sarkar SK (2015) An analytical model for tunnel barrier modulation in triple metal double gate TFET. IEEE Trans Electron Devices 62:2136–2142

(2013) ATLAS: Device simulator software, SILVACO Int., Santa Clara, CA, USA

Vishnoi R, Kumar MJ (2014) Compact analytical model of dual material gate tunneling field-effect transistor using interband tunneling and channel transport. IEEE Trans Electron Devices 61:1936–1942

Villalon A, Le Carval G, Martinie S, Le Royer C, Jaud M-A, Cristoloveanu S (2014) Further insights in TFET operation. IEEE Trans Electron Devices 61:2893–2898

Min J, Wu J, Taur Y (2015) Analysis of source doping effect in tunnel FETs with staggered bandgap. IEEE Electron Device Lett 36:1094–1096

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Gupta, S.K., Kumar, S. Analytical Modeling of a Triple Material Double Gate TFET with Hetero-Dielectric Gate Stack. Silicon 11, 1355–1369 (2019). https://doi.org/10.1007/s12633-018-9932-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-018-9932-y