Abstract

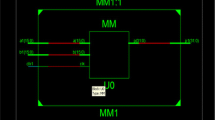

The advancement in wireless telecommunication technologies like 3G, 4G and now 5G enrich the demand of high performance portable devices, operating at high frequencies i.e. from few hundred MHz to several GHz. High performance can only be achieved at the cost of high power dissipation. Nowadays, the use of FPGAs is rapidly increasing due to its low cost and smaller time to market. Today’s high end FPGAs are capable of implementing high performance designs such as transceivers for RF application, signal processing and image processing applications etc. This is only possible due to their complex designs that includes on chip dedicated multipliers, Dual RAM blocks, Ethernet and DCMs etc. Since FPGAs consume large amount of power, it becomes a challenge for the designers to implement low power battery operated communication systems. Several power estimation models are available in literature for early stage power estimation of FPGAs in the synthesis design flow but they provide less accuracy (high percentage error) for the designs incorporated with low power reduction technique. This paper presents the limitation of existing power estimation model proposed by Deng. The given model is converted into a script using MATLAB. The power values estimated from the power model (script) are compared with the high level synthesis tool: Xpower Analyzer targeted to Virtex FPGA. For estimation of power values, an embedded multiplier is synthesized for two different configurations: one with ‘CE’ (low power) and another without ‘CE’ for different I/O vector length. The results suggested that the given low level power estimation models provide less accuracy (high % error) for the designs incorporated with low power reduction technique i.e. with ‘CE’. Further, there is a scope of remodel the existing model for the observed shortcoming.

Similar content being viewed by others

References

Deng, L., Sobti, K., Chakrabarti, C., (2011). Accurate models for estimating area and power of FPGA implementations. In Proceedings of IEEE International Conference on Acoustics Speech and Signal Processing, (pp. 1417–1420).

Jevtic, R., & Carreras, C. (2010). Power estimation of embedded multiplier blocks in FPGAs. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 18(5), 835–839.

Choy, N. C. K., Wilton, S. J. E., (2006). Activity-based power estimation and characterization of DSP and multiplier blocks in FPGAs. In Proceedings of FPT, (pp. 253–256).

Ell´eouet, D., Julien, N., Houzet, D., Cousin, J. G., Martin, E. (2004). Power consumption characterization and modeling of embedded memories in Xilinx Virtex 400E FPGA. In Proceedings of the EUROMICRO Systems on Digital System Design, (pp. 394–401).

Verma, G., Kumar, M., & Khare, V. (2015). Low power techniques for digital system design. Indian Journal of Science and Technology, 8(17), IPL063

Mishra, S., Verma, G. (2013). Low power and area efficient implementation of BCD adder on FPGA. In Proceeding of IEEE International Conference on Signal Processing and Communication, (pp. 461–465).

Shinde, J., Salankar, S. S. (2011). Clock gating-A power optimizing technique for VLSI circuits. In Proceedings of Annual IEEE India Conference, (pp. 1–4).

Castro, J., Parra, P., Acosta, A. J. (2010). Optimization of clock-gating structures for low-leakage high-performance applications. In Proceedings of IEEE International Symposium on Efficient Embedded Computing, (pp. 3220–3223).

Teng, S. K., Soin, N. Regional clock gate splitting algorithm for clock tree synthesis. In Proceedings of IEEE International Conference on Semiconductor Electronics, (pp. 131–134).

Babighian, P., Benini, L., & Macii, E. (2005). A scalable algorithm for RTL insertion of gated clocks based on ODCs computation. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 24(1), 29–42.

Huda, S., Mallick, M., Anderson, J. H. (2009). Clock Gating Architectures for FPGA Power Reduction. In Proceedings of IEEE International Conference onField Programmable Logic and Applications, (pp. 112–118).

Kumar, T., Pandey, B., Das, T., & Chowdhry, B. S. (2014). Mobile DDR IO standard based high performance energy efficient portable ALU design on FPGA. Wireless Personal Communications, 76(3), 569–578.

Kumar, T., Pandey, B., Musavi, S. H. A., & Zaman, N. (2015). CTHS based energy efficient thermal aware image ALU Design on FPGA. Wireless Personal Communications, 83(1), 671–696.

Xilinx, San Jose, CA. (2003). Using embedded multipliers in Spartan-3 FPGA. Xilinx Appl. Note XAPP467, v.1.1.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Verma, G., Kumar, M. & Khare, V. Low Power Synthesis and Validation of an Embedded Multiplier for FPGA Based Wireless Communication Systems. Wireless Pers Commun 95, 365–373 (2017). https://doi.org/10.1007/s11277-016-3897-1

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-016-3897-1