Abstract

Cadmium sulphide (CdS) thin-films have been electrodeposited using two electrode system to be used as the hole back diffusion barrier (hbdb) layer for graded bandgap solar cells with p-type windows. Cadmium acetate dihydrate [Cd(CH3COO)2·2H2O] and ammonium thiosulphate [(NH4)2S2O3] have been used as the cadmium (Cd) and sulphur (S) precursors respectively. In this work, CdS layers have been grown on glass/FTO (fluorine doped tin oxide) substrates at cathodic potentials ranging from 1300 to 1460 mV in order to find the best growth voltage. N-type conductivity is observed for all the layers and band-gap ranged between ~ 2.36 and ~ 2.40 eV for as-deposited layers and ~ 2.31 and ~ 2.36 eV for air-annealed layers. X-ray diffraction (XRD) analysis revealed cubic/hexagonal mixed crystallinity for the as-grown layers which indicates a tendency of transiting towards hexagonal structure upon annealing. Compositional and morphological characteristics of the layers have been investigated with energy dispersive X-ray (EDX) and scanning electron microscopy (SEM) respectively.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

CdS/CdTe based solar cells, being one of the current market leaders for thin-film photovoltaics (PV), recorded 22.1% highest conversion efficiency, along with an ~ 18% module efficiency [1, 2]. The major growth techniques used for large area CdS/CdTe-based solar cell fabrication are, close spaced sublimation (CSS) [3], sputtering [4] and electrochemical deposition (ED) [5]. However, with respect to deposition process continuity, doping simplicity, self-purification, scalability, manufacturability, economic viability and Cd-containing waste reduction, electrodeposition (ED) is considered one of the leading techniques [6,7,8,9,10,11].

Our group has been working on CdTe-based thin-film PV research using all electrodeposited semiconductors following the graded bandgap (GBG) device structure. Graded bandgap solar cells, first conceptualised by Konagai and Takahashi [12], was later improved and next-generation multilayer graded bandgap solar cells were proposed and implemented by our group [11, 13,14,15]. Between the two proposed approaches of graded bandgap devices on n-type and p-type window materials, cells fabricated on p-type windows have a potential of achieving high performance due to its possibility of producing higher open circuit voltage (Voc). This was experimentally demonstrated by achieving Voc = 1.175 mV with GaAs/AlGaAs system [16].

Our current efforts are focused on developing CdTe-based graded bandgap devices with p-type windows, using low-cost and scalable electro-plated materials. For multilayer GBG solar cells, apart from the regular window layer and absorber layer, improvements can be made by including an electron back-diffusion barrier (ebdb) layer and a hole back-diffusion barrier (hbdb) layer [17]. This will minimize the recombination of photo-generated and separated charge carriers caused by thermionic emission over the potential barrier [11, 17], as depicted in Fig. 1. A wide bandgap p-type CdTe:Mg material has already been developed and characterised by the group to be used as the possible p-window and reported in reference [18].

n-CdS is widely used as the window layer in electroplated graded bandgap solar cells developed with n-window approach. The most widely used cadmium (Cd) precursor is CdCl2 in this case [19, 20]. But for electrodepositing CdS as a wide-bandgap hole back diffusion barrier (hbdb) layer, precursors should be chosen very carefully because, in this case the whole glass/FTO/p-window/CdTe absorber layer would require to be submerged into the CdS electrolytic bath. Chlorine being a very strong corrosive agent and for having the strong hydrochloric acidity due to Cl− and H+ ions in the electrolyte, the underlying device structure can be dissolved [21]. Therefore, cadmium acetate [Cd(CH3COO)2] precursor with weaker acidity has been used in this work.

Moreover, literature suggests sodium thiosulphate (Na2S2O3) as the most widely used S precursor for CdS electrodeposition. But, this precursor tends to provide accumulation of sodium (Na), a p-type dopant in the CdS bath, which by incorporating through absorption or reaction may reduce the electrical conductivity of the CdS layer [22]. Hence, ammonium thiosulphate [(NH4)2S2O3] has been used as the S precursor in this work.

This work focuses on growing ED CdS with the mixture of these precursors for the first time along with investigating through the growth potential and post-annealing characteristics. The aim is to grow n-CdS to be used as an hbdb layer suitable to be deposited on glass/TCO/p-window/CdTe-absorber layer for developing graded bandgap devices in future.

2 Experimental procedure

Cadmium sulphide (CdS) thin-film layers were grown from a 400 ml aqueous solution of 99% pure 0.3 M cadmium acetate dihydrate [Cd(CH3COO)2.2H2O] and 99.5% pure 0.06 M ammonium thiosulphate [(NH4)2S2O3] in de-ionised water. All these chemicals have been purchased from Sigma-Aldrich Ltd (UK). The pH and temperature of the solution has been kept constant at 3.00 ± 0.02 and ~ 85 °C respectively. The pH has been adjusted using either nitric acid or ammonium hydroxide (NH4OH). Two electrode electrodeposition technique has been used for depositing the semiconductor materials on glass/TEC-7 Fluorine doped tin oxide (glass/FTO) substrates having sheet resistance of ~ 7 Ω/square. High purity carbon rod has been used as the anode whereas, cathode (working electrode) has been prepared by attaching a glass/FTO substrate to a carbon rod using insulating polytetrafluoroethylene (PTFE) tape. Prior to electrodeposition, the substrates were cut into 3 cm × 3 cm dimension and rinsed thoroughly with de-ionized water after washing with soap solutions using cotton buds. The substrates were later dried with nitrogen gas. GillAC potentiostat from ACM Instruments is used as the power source for the 2-electrode ED system. The electrolytic solution was heated and stirred using a hot plate and magnetic stirrer. Moderate stirring rate has been applied to the bath throughout the electrodeposition process.

Cyclic voltammetry has been carried out to determine an estimated range of deposition potential where Cd and S co-deposition takes place. The deposited layers were investigated using energy dispersive X-ray (EDX) spectroscopy for compositional and material identification analysis and X-ray diffraction (XRD) for structural analysis and scanning electron microscopy (SEM) for morphological analysis. For characterising and optimising electrical and optical properties of the ED samples, photoelectrochemical (PEC) cell measurements and optical absorption using UV–Vis spectrophotometry have been carried out.

3 Results and discussion

3.1 Cyclic voltammetric Study

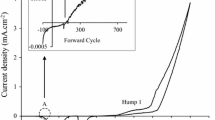

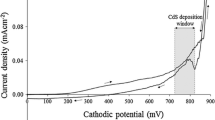

Cyclic voltammograms were separately recorded for electro-purified aqueous electrolytes containing 0.3 M Cd(CH3COO)2·2H2O, 0.06 M (NH4)2S2O3 and a mixture of 0.3 M Cd(CH3COO)2·2H2O and 0.06M (NH4)2S2O3. The pH and temperature of the solutions were adjusted to 3.00 ± 0.02 and ~ 85 °C respectively. The cyclic sweep is recorded with a sweep rate of 3 mVs−1 within a cathodic potential range of 0.0 mV to 2000 mV. Figure 2 depicts a typical voltammogram data plotted with instructive symbols and legends.

Figure 2a depicts, due to the difference of redox potentials amongst the consisting ions, in the forward cycle of voltammogram sulphur (S) having a redox potential (E°) of + 0.449 V (with reference to standard H2 electrode), starts depositing at the beginning at ~ 500 mV. The deposition takes place from the S precursor, according to the electro-chemical reaction Eqs. 1 and 2:

Later, Cd having an E° of − 0.403 V (w.r.t. standard H2 electrode) starts depositing at ~ 850 mV (Fig. 2b and point A in Fig. 2c) according to the electro-chemical reaction Eq. 3:

Hence, Fig. 2c shows the co-deposition of cadmium and sulphur begins hereafter and S-rich CdS starts to deposit from ~ 850 mV onward according to the reaction Eq. 4. As higher cathodic voltage is applied, Cd starts increasingly incorporating to the layer.

Therefore, it is estimated that near-stoichiometric CdS layer can be found within a range of ~ 1300 mV to ~ 1500 mV of growth potential. From 1500 mV onward, there is a relatively higher increment in current density, which indicates the possible dissociation of water.

In the revers cycle of Fig. 2c, the negative peak at ~ 850 mV reconfirms the dissolving of any elemental Cd as well as dissociation of CdS formed on the FTO surface.

3.2 X-ray diffraction (XRD) spectroscopic analysis

Aim of this analysis is to carry out the structural analysis of the deposited layers at different growth voltages. Philips PW X’Pert Pro diffractometer has been used with Cu-Kα monochromator having a wavelength of 1.54 Å, where the source tension and current were kept as 40 kV and 40 mA respectively. XRD spectroscopy have been carried out on 5 as-deposited (AD) and heat-treated (HT) samples grown at 1420, 1430, 1440, 1450 and 1460 mV cathodic potential. In Fig. 3a, at 2Ɵ ≈ 26.6° and ≈ 30.1° the as-deposited samples show XRD peaks corresponding to the diffraction from CdS (111) cubic/(002) hexagonal and CdS (200) cubic planes respectively. It is difficult to differentiate between CdS (111) C and (002) H plane because they coincide within 1%, therefore the XRD peak is often considered as resultant from mixed structures [23, 24]. Also, increment in the dominant peak intensity for AD CdS layers indicates the coinciding of CdS (111)C/(002)H peak with the underlying FTO (110) peak. After heat-treatment it is widely observed that CdS transforms phase from cubic/mixed to completely hexagonal CdS [20, 22]. In this work, the effect of annealing demonstrates a different trend of changes, indexing with the JCPDS reference files 89-0440 for cubic phase and 80-0006 for hexagonal phase. Figure 3b shows, after the heat treatment of the layers at 400 °C for 20 min, whereas CdS (111) C/(002) H mixed phases still stay the preferred orientation at 2Ɵ ≈ 26.6°, the slight (200) C peak disappears and CdS (110) H/(220) C mixed phase come into appearance at 2Ɵ ≈ 43.9°. Though, this does not indicate a confirmed phase transition of the material from mixed to hexagonal, but shows a tendency towards achieving the hexagonal phase which is further supported by later experiments. For the dominant planes resulting from different growth voltages, the trend shows that peak intensity keeps gradually increasing upto 1450 mV and then goes down. Figure 4 depicts this trend for both the as-deposited and heat-treated CdS samples. Along with the peak intensity, change of the CdS crystallite size due to growth voltage is shown in Table 1 for both the AD and HT samples. Crystallite size at the preferred orientation has been calculated using Scherrer’s formula given by Eq. (5).

where wavelength, λ = 1.54 Å, β = full width at half maximum (FWHM) of the diffraction peak in radian and θ = Bragg’s angle of incidence.

Table 1 shows that the as-deposited samples grown at 1450 mV has the largest crystallite size among the others. For HT samples, the trend carries on and all the HT samples show larger crystallite size than their as-deposited counterparts.

However, all CdS layers grown here on the TEC-7 glass/FTO substrates show overlaps of the dominant CdS plane with the dominant FTO (110) plane at 2Ɵ ≈ 26.6°. Since, the first batch of FTO substrates shown the preferred FTO orientation at 2Ɵ ≈ 26.6°, for reconfirmation, another CdS layer has been deposited at the best apparent growth voltage (~ 1450 mV) on another batch of substrate having a different preferred orientation. Figure 5 shows that, CdS layers grown on a substrate having a preferred orientation elsewhere, also depicts a sharp peak intensity at 2Ɵ ≈ 26.6° for both as-deposited and heat-treated samples. The AD layer demonstrates cubic/hexagonal mixed phases at preferred orientation and (200) C peak at 2Ɵ ≈ 30.1°. The HT sample still demonstrates mixed phases at preferred orientation, but (200) C peak disappears and another mixed peak appears at 2Ɵ ≈ 43.9° like the previous batch shown in Figs. 3 and 4. Alongside, there appears a slight peak at 2Ɵ ≈ 25.0° for CdS (100) hexagonal phase. This further indicates a tendency for the layers towards achieve hexagonal phase upon heat-treatment, though having possibilities to have mixed phases present in the structure.

3.3 Energy dispersive X-ray (EDX) spectroscopy

EDX was carried out on the as-deposited and heat-treated CdS samples grown at 1430, 1440 and 1450 mV, using the compositional analysis software associated with the Quanta 650 SEM equipment, in order to obtain the chemical composition of the samples. The heat-treated samples were annealed at 400 °C for 20 min in air. Figure 6 shows the EDX spectra of the as-deposited and heat-treated sample grown at 1450 mV. Table 2 presents the atomic composition of as-dep and HT CdS grown at different voltages along with their changes in Cd/S ratio. It depicts that all the as-dep layers are S-rich in nature regardless the growth potential, whereas after heat treatment all of them shows slight comparative decrement in S percentage which resulted the HT sample grown at 1450 mV reaching stoichiometry. Despite having concerns about accuracy, EDX technique and this analysis give a qualitative idea about the composition of the CdS films and the near-stoichiometric growth potential for the process. This achievement of stoichiometry confirms the structural analysis using XRD and the achievement of highest crystallinity at 1450 mV. Any thin-film layer with only one phase tend to crystallise better during this growth process.

3.4 Photoelectrochemical cell (PEC) measurement

Photoelectrochemical cell measurements were carried out to determine the conduction type of the electrodeposited layers. The measurement is taken by dipping a glass/FTO/CdS layer along with another carbon electrode into an electrolyte prepared from 0.1 M Na2S2O3 (sodium thiosulphate) aqueous solution. The voltage difference between the electrodes under dark (VD) and illuminated (VL) condition is measured to determine the conduction type of the semiconductor layer. This difference (VL − VD) represents the open circuit voltage of the solid/liquid junction and is commonly referred as the PEC signal. Polarity of the PEC signal indicates the conduction type. In this work, negative polarity of the PEC signal directs to n-type semiconductor and positive polarity directs to p-type semiconductor, whereas for metals, insulators and intrinsic semiconductors PEC signal is ideally zero. Figure 7 shows that all the CdS layers deposited at different cathodic potentials are n-type in conductivity as expected [19, 25]. HT samples show a stronger PEC signal compared to that of the AD samples. Strength of the PEC signal qualitatively indicates to the doping density and depletion region strength.

3.5 Optical absorption analysis

Optical absorption study has been carried out using Carry 50 scan UV–Vis spectrophotometer, for AD and HT CdS layers deposited at different growth voltages. The obtained absorption data within the wavelength of 300 nm to 1000 nm, have been used to plot an alternative Tauc plot, where square of absorbance (a2) is plotted against photon energy (hv) [15, 26]. The intersection of extrapolated tangent line derived from the curve, gives the direct band-gap (Eg) of the studied semiconductor material.

According to Figs. 8a and 9, as-deposited CdS layers show direct band-gaps ranging between ~ 2.36 and ~ 2.40 eV, where the lowest band-gap value is observed at ~ 1450 mV of growth potential. Heat-treated CdS layers depict a similar trend as per Figs. 8b and 9, but after heat-treatment, band-gap decreases overall compared to that of the AD leyers. Band-gaps of the HT leyers range between ~ 2.31 and ~ 2.36 eV. The lowest band-gap value (~ 2.31 eV) for the heat-treated samples is found for the layer grown at 1450 mV which differs slightly from the previously measuered Eg values (~ 2.42 eV) for electrodeposited CdS layers in the group [20, 22, 27]. This observation is supported by the visual appearance of the deposited layers as shown in Fig. 10. The CdS layers electrodeposited from these precursors demonstrate an orangish yellow appearance compared to the greeninsh yellow appearance of the previously electrodeposited CdS layers in our group [15, 20]. This indicates a possible shift in the typical absorption point of the layer from lower wavelength towards higher wavelength, and vice-versa for the band-gap energy.

3.6 Scanning electron microscopy (SEM) analysis

In order to carry out the morphological characterisation of the CdS layers, SEM analysis has been done in the form of micrographs with Quanta 650 nano SEM instrument using 15.0 kV electron beam voltage and 32,000× of magnification. SEM images of glass/FTO/CdS substrates have been taken for both as-deposited and heat-treated samples grown at 1440 mV (Fig. 11a, b) and 1450 mV (Fig. 11c, d). In Fig. 11, at both growth voltages, regardless of heat-treatment, all the surfaces demonstrate agglomerations of CdS crystallites. From the SEM micrograph the size of the agglomerations are ranging approximately between ~ 200 and ~ 300 nm. Therefore, individual CdS crystallites are not visible in the SEM image as calculated above in Table 1.

4 Conclusion

In this work, a low acidic precursor for Cd, and Na-free precursor for S were used for the electrolyte, so that CdS layers can be electrodeposited on top of CdTe absorber layers, in order to develop all-electrodeposited graded bandgap devices, starting from p-type wide-bandgap window materials. As the first step towards achieving this, CdS layers were deposited on glass/FTO substrate with the new precursors. The optimised growth voltage was 1450 mV for experimental conditions used in this work. As-deposited material consists of both cubic and hexagonal CdS, but demonstrates a tendency to transit towards hexagonal CdS after heat treatment at 400 °C for 20 min in air. All the layers grown are n-type in electrical conductivity. The only difference observed was the physical appearance of orangish colour instead of greenish yellow colour observed for CdS grown with other precursors. Accordingly, a lower bandgap energy of 2.31 eV was observed for the heat treated CdS layers. Incorporation of the layers in both graded bandgap devices based on n-type and p-type window layers are in progress.

References

First solar, First solar achieves yet another cell conversion efficiency world record. First Sol. Media, pp. 1–2 (2016)

A. Rix, J. Steyl, M.J. Rudman, U. Terblanche, J. van Niekerk, First Solar’s CdTe module technology—performance, life cycle, health and safety impact assessment Centre for Renewable and Sustainable Energy Studies. no. December (2015)

C. Ferekides, D. Marinskiy, V. Viswanathan et al., High efficiency CSS CdTe solar cells. Thin Solid Films, 361–362, 520–526 (2000)

M.M. Soliman, M.M. Shabana, F. Abulfotuh, CdS/CdTe solar cell using sputtering technique. Renew. Energy 8(1–4) 386–389 (1996)

O.K. Echendu, I.M. Dharmadasa, Graded-bandgap solar cells using all-electrodeposited ZnS, CdS and CdTe thin-films. Energies 8(5), 4416–4435 (2015)

A.A. Ojo, I.M. Dharmadasa, The effect of fluorine doping on the characteristic behaviour of CdTe. J. Electron. Mater. 45(11), 5728–5738 (2016)

J. Woodcock, A. Turner, M. Ozsan, J. Summers, Thin film solar cells based on electrodeposited CdTe,” in The Conference Record of the Twenty-Second IEEE Photovoltaic Specialists Conference—1991, (1991), pp. 842–847

D. Cunningham, M. Rubcich, D. Skinner, Cadmium telluride PV module manufacturing at BP solar, Prog. Photovolt. Res. Appl. 10(2), 159–168 (2002)

I.M. Dharmadasa, J. Haigh, Strengths and advantages of electrodeposition as a semiconductor growth technique for applications in macroelectronic devices. J. Electrochem. Soc. 153(1), G47 (2006)

A.A. Ojo, I.M. Dharmadasa, Progress in development of graded bandgap thin film solar cells with electroplated materials. J. Mater. Sci. Mater. Electron. 28(9), 6359–6365 (2017)

I.M. Dharmadasa, Advances in Thin-Film Solar Cells, 2nd edn. (Pan Stanford Publishing Pte. Ltd., Singapore, 2018)

M. Konagai, K. Takahashi, Graded bandgap pGa1 – xAlxAs-nGaAs heterojunction solar cells, J. Appl. Phys. 46(8), 3542–3546 (1975)

A.A. Ojo, I.M. Dharmadasa, 15.3% efficient graded bandgap solar cells fabricated using electroplated CdS and CdTe thin films. Sol. Energy 136, 10–14 (2016)

I.M. Dharmadasa, Third generation multi-layer tandem solar cells for achieving high conversion efficiencies. Sol. Energy Mater. Sol. Cells 85(2), 293–300 (2005)

A.A. Ojo, W.M. Cranton, I.M. Dharmadasa, Next Generation Multilayer Graded Bandgap Solar Cells. (Springer International Publishing, New York, 2019

I.M. Dharmadasa, J. Roberts, G. Hill, Third generation multi-layer graded band gap solar cells for achieving high conversion efficiencies—II: experimental results, Sol. Energy Mater. Sol. Cells, 88(4), 413–422 (2005(

I.M. Dharmadasa, Fermi level pinning and effects on CuInGaSe2-based thin-film solar cells. Semicond. Sci. Technol. 24(5), 55016 (2009)

A. Alam, A. Ojo, J. Jasinski, I. Dharmadasa, Magnesium Incorporation in n-CdTe to produce wide bandgap p-type CdTe:Mg window layers. ChemEngineering 2(4), 59 (2018)

I.M. Dharmadasa, A.A. Ojo, Unravelling complex nature of CdS/CdTe based thin film solar cells. J. Mater. Sci. Mater. Electron. 28(22), 16598–16617 (2017)

A.A. Ojo, I.M. Dharmadasa, Investigation of electronic quality of electrodeposited cadmium sulphide layers from thiourea precursor for use in large area electronics. Mater. Chem. Phys. 180, 14–28 (2016)

J.P. Farr, W.L. Smith, D.S. Steichen, Bleaching Agents, in Kirk-Othmer Encyclopedia of Chemical Technology, vol. 4 (Wiley, Hoboken, 2003), pp. 43–81

N.A. Abdul-Manaf, A.R. Weerasinghe, O.K. Echendu, I.M. Dharmadasa, Electro-plating and characterisation of cadmium sulphide thin films using ammonium thiosulphate as the sulphur source. J. Mater. Sci. Mater. Electron. 26(4), 2418–2429 (2015)

O. Zelaya-Angel, L. Hernandez, O. De Melo et al., Band-gap shift in CdS: phase transition from cubic to hexagonal on thermal annealing. Vacuum 46(8–10), 1083–1085 (1995)

R. Ramírez-Bon, N.C. Sandoval-Inda, F.J. Espinoza-Beltrán, M. Sotelo-Lerma, O. Zelaya-Angel, C. Falcony, Structural transition of chemically deposited CdS films on. J. Phys. Condens. Matter 9(January), 10051–10058 (1997)

W.G.C. Kumarage, R.P. Wijesundera, V.A. Seneviratne, C.P. Jayalath, B.S. Dassanayake, Tunable optoelectronic properties of CBD-CdS thin films via bath temperature alterations. J. Phys. D Appl. Phys. 49(9), 95109 (2016)

I.M. Dharmadasa, M. Madugu, O. Olusola et al., Electroplating of CdTe thin films from cadmium sulphate precursor and comparison of layers grown by 3-electrode and 2-electrode systems. Coatings 7(2), 17 (2017)

O.K. Echendu, F. Birhanu, I.M. Dharmadasa, E.C. Eze, Characteristics of nanocrystallite-CdS produced by low-cost electrochemical technique for thin film photovoltaic application: the influence of deposition voltage. Int. J. Photoenergy 6, article 1600144, (2017)

Acknowledgements

The authors would like to thank Dr. A. A. Ojo for valuable advices and Mr. Ahmed Alfurshuti for assisting some measurements as the work progressed. The first author also wishes to acknowledge the financial contributions made by UA Doctoral Training Alliance (DTA) and CARA for funding the doctoral research, and thank University of Liberal Arts Bangladesh (ULAB) for granting study leave to join the research programme.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare no conflict of interest.

Rights and permissions

OpenAccess This article is distributed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made.

About this article

Cite this article

Alam, A.E., Cranton, W.M. & Dharmadasa, I.M. Electrodeposition of CdS thin-films from cadmium acetate and ammonium thiosulphate precursors. J Mater Sci: Mater Electron 30, 4580–4589 (2019). https://doi.org/10.1007/s10854-019-00750-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10854-019-00750-1