Abstract

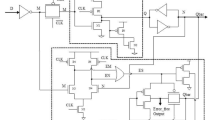

This paper presents and analyzes a high performance latch tolerating single event upsets (SEU) in 45 nm CMOS technology. The internal nodes of the latch are immune to SEUs by combining Muller C-elements with dual modular redundancy and interlocked feedback. The output nodes are SEU resilient and allow a recovery to the correct logic value when an SEU occurs at output nodes. The power dissipation, propagation delay and critical charge of the proposed SEU-tolerant latch are evaluated and discussed with SPICE simulations. The simulation results show that the proposed latch achieves a better tradeoff among soft error rate, delay, power and area than previous hardened latches. On average the HPST latch requires 70.31 % area overhead, but improves the critical charge by 71.05 % and reduces the power delay product by 51.96 %. It is thus an excellent solution for applications requiring both high performance and high reliability. Monte Carlo simulation also verifies the robustness of the proposed latch in presence of process, temperature and voltage (PVT) variations.

Similar content being viewed by others

References

Atkinson NM et al (2011) Effect of transistor density and charge sharing on single-event transients in 90-nm bulk CMOS. IEEE Trans Nucl Sci 58(6):2578–2584

Baumann RC (2005) Radiation-induced soft-errors in advanced semiconductor technologies. IEEE Trans Device Mater Reliab 5(3):305–316

Calin T, Nicolaidis M, Velazco R (1996) Upset hardened memory design for submicron CMOS technology. IEEE Trans Nucl Sci 43(6):2874–2878

Fazeli M, Patooghy A, Miremadi S G, Ejlali A (2007) Feedback redundancy: a power-aware efficient SEU-tolerant latch design for deep sub-micron technologies. Proc IEEE/IFIP Intl Conf Dependable Syst Netw, Edinburgh, pp 276–285

Ghahroodi M M, Ozer E, Bull D (2013) SEU and SET-tolerant ARM Cortex-R4 CPU for Space and Avionics Applications. Proc. Second Workshop on Manufacturable and Dependable Multicore Architectures at Nanoscale (MEDIAN’13), Avignon, France, pp 1–4

Huang Z (2014) A high performance SEU-tolerant latch for nanoscale CMOS technology, Proc. Design, Automation & Test in Europe (DATE’14), Dresden, Germany, pp 1–5

Imhof M E, Wunderlich H-J, Zoellin C G (2008) Integrating Scan Design and Soft Error Correction in Low-Power Applications. Proc. IEEE Intl. On-Line Test Symposium (IOLTS’08), Rhodes, pp 59–64

Kauppila AV et al (2012) Effect of negative bias temperature instability on the single event upset response of 40 nm flip-flops. IEEE Trans Nucl Sci 59(6):2651–2657

Lee H et al (2010) LEAP: Layout Design through Error-Aware Placement for Soft-Error Resilient Sequential Cell Design. Proc. IEEE Intl. Reliability Physics Symp., Anaheim, CA, USA, pp 203–212

Liang H, Wang Z, Huang Z, Yan A (2014) Design of a Radiation Hardened Latch for Low-power Circuits. Proc. Asian Test Symposium (ATS’14), Hangzhou, China, pp 19–24

Lin S, Kim Y-B, Lombardi F (2012) Analysis and design of nanoscale CMOS storage elements for single-event hardening with multiple-node upset. IEEE Trans Device Mater Reliab 12(1):68–77

Lin S, Kim Y-B, Lombardi F (2011) Design and performance evaluation of radiation hardened latches for nanoscale CMOS. IEEE Trans Very Large Scale Integr (VLSI) Syst 19(7):1315–1319

Nan H, Choi K (2012) High performance, low cost, and robust soft error tolerant latch designs for nanoscale CMOS technology. IEEE Trans Circuits Syst 59(7):1445–1457

Nicolaidis M (2007) GRAAL: a new fault tolerant design paradigm for mitigating the flaws of deep nanometric technologies. Proc. IEEE Intl. Test Conference (ITC’07), Santa Clara, pp 1–10

Omana M, Rossi D, Metra C (2010) High-performance robust latches. IEEE Trans Comput 59(11):1455–1465

Predictive Technology Model for Spice, [Online]. Available: http://ptm.asu.edu/

Sheshadri VB, Bhuva BL, Reed RA, Weller RA, Mendenhall MH, Schrimpf RD (2010) Effects of multi-node charge collection in flip-flop designs at advanced technology nodes. Proc. IEEE International Reliability Physics Symposium (IRPS’10), Anaheim, pp 1026–1030

Shirinzadeh S, Asli R N (2013) Design and performance evaluation of a low cost full protected CMOS latch. Proc. 17th CSI Intl. Symp. on Computer Architecture and Digital Systems (CADS’13), Tehran, pp 139–141

Weste N, Harris D (2011) CMOS VLSI Design: A Circuits and Systems Perspective. Addison Wesley

Ye Y, Liu F, Chen M, Nassif S, Cao Y (2011) Statistical modeling and simulation of threshold variation under random dopant fluctuations and line-edge roughness. IEEE Trans Very Large Scale Integr (VLSI) Syst 19(6):987–996

Zhang M et al (2006) Sequential element design with built-in soft error resilience. IEEE Trans Very Large Scale Integr (VLSI) Syst 14(12):1368–1378

Acknowledgments

This work has been co-funded by National Natural Science Foundation of China (NSFC) under Grants No. (61106038, 61274036, 61371025, 61474036).

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: C. Metra

A preliminary version of this paper was presented at the Conference and Exhibition on Design, Automation and Test in Europe (DATE 2014) [6].

Rights and permissions

About this article

Cite this article

Huang, Z., Liang, H. & Hellebrand, S. A High Performance SEU Tolerant Latch. J Electron Test 31, 349–359 (2015). https://doi.org/10.1007/s10836-015-5533-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-015-5533-5