Abstract

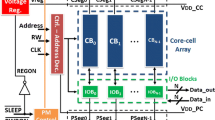

This paper presents the results of resistive-open defect insertion in different locations of Infineon 0.13 μm embedded-SRAM with the main purpose of verifying the presence of dynamic faults. This study is based on the injection of resistive defects as their presence in VDSM technologies is more and more frequent. Electrical simulations have been performed to evaluate the effects of those defects in terms of detected functional faults. Read destructive, deceptive read destructive and dynamic read destructive faults have been reproduced and accurately characterized. The dependence of the fault detection has been put in relation with memory operating conditions, resistance value and clock cycle, and the importance of at speed testing for dynamic fault models has been pointed out. Finally resistive Address Decoder Open Faults (ADOF) have been simulated and the conditions that maximize the fault detection have been discussed as well as the resulting implications for memory test.

Article PDF

Similar content being viewed by others

Avoid common mistakes on your manuscript.

References

R.D. Adams, High Performance Memory Testing, Kluwer Academic Publishers, Sept. 2002.

R.D. Adams and E.S. Cooley, “Analysis of Deceptive Destructive Read Memory Fault Model and Recommended Testing,” IEEE North Atlantic Test Workshop, May 1996.

R.D. Adams and E.S. Cooley, “False Write Through and Un-Restored Write Electrical Level Fault Models for SRAMs,” Records IEEE Int’l Workshop on Memory, Technology, Design and Testing, 1997, pp. 27–32.

Z. Al-Ars and A.J. van de Goor, “Static and Dynamic Behavior of Memory Cell Array Opens and Shorts in Embedded DRAMs,” in Proc. Design, Automation and Test in Europe, 2001, pp. 496–503.

K. Baker et al., “Defect-Based Delay Testing of Resistive Vias-Contacts. A Critical Evaluation,” in Proc. Int’l Test Conf., 1999, pp. 467–476.

L. Dilillo, P. Girard, S. Pravossoudovitch, A. Virazel, and S. Borri, “March iC-: An Improved Version of March C- for ADOFs Detection,” in Proc. VLSI Test Symposium, 2004, pp. 129–134.

L. Dilillo, P., Girard, S. Pravossoudovitch, A. Virazel, S. Borri, and M. Hage-Hassan, “March Tests Improvement for Address Decoder Open and Resistive Open Fault Detection,” in Proc. Latin American Workshop, 2004, pp. 31–36.

L. Dilillo, P., Girard, S. Pravossoudovitch, A. Virazel, S. Borri, and M. Hage-Hassan, “Dynamic Read Destructive Fault in Embedded-SRAMs: Analysis and March Test Solutions,” in Proc. European Test Symposium, 2004.

A.J. van de Goor, “Using March Tests to Test SRAMs,” IEEE Design & Test of Computers, vol. 10, no. 1, pp. 8–14, 1993.

A.J. van de Goor, Testing Semiconductor Memories, Theory and Practice, Gouda, The Netherlands, COMTEX Publishing, 1998.

A.J. van de Goor and Z. Al-Ars, “Functional Memory Faults: A Formal Notation and a Taxonomy,” in Proc. IEEE VLSI Test Symposium, May 2000, pp.281–289.

A.J. van de Goor and J. de Neef, “Industrial Evaluation of DRAM Tests,” in Proc. Design Automation and Test in Europe, 1999, pp. 623–630.

S. Hamdioui, Z. Al-Ars, and A.J. van de Goor, “Testing Static and Dynamic Faults in Random Access Memories,” in Proc. IEEE VLSI Test Symposium, 2002, pp. 395–400.

C.-M. James et al., “Testing for Resistive Opens and Stuck Opens,” in Proc. Int’l Test Conf., 2001, pp. 1049–1058.

M. Marinescu, “Simple and Efficient Algorithms for Functional RAM Testing,” in Proc. Int’l Test Conf., 1982, pp. 236–239.

W. Needham et al., “High Volume Microprocessor Test Escapes—An Analysis of Defects Our Tests are Missing,” in Proc. Int’l Test Conf., 1998, pp. 25–34.

D. Niggemeyer, M. Redeker, and J. Otterstedt, “Integration of Non-classical Faults in Standard March Tests,” Records of the IEEE Int. Workshop on Memory Technology, Design and Testing, 1998, pp. 91–96.

J. Otterstedt et al., “Detection of CMOS Address Decoder Open Faults with March and Pseudo Random Memory Tests,” in Proc. Int’l Test Conf., 1998, pp. 53–62.

R. Rodriquez et al., “Resistance Characterization of Interconnect Weak and Strong Open Defects,” IEEE Design & Test of Computers, vol. 19, no. 5, pp. 18–26, 2002.

M. Sachdev, “Test and Testability Techniques for Open Defects in RAM Address Decoders,” in Proc. IEEE European Design & Test Conference, 1996, pp. 428–434.

M. Sachdev, “Open Defects in CMOS RAM Address Decoders,” IEEE Design & Test of Computers, vol. 14, no. 2, pp. 26–33, 1997.

I. Schanstra and A.J. van de Goor, “Industrial Evaluation of Stress Combinations for March tests applied to SRAMs,” in Proc. Int’l Test Conf., 1999, pp. 983–992.

K. Zarrineh et al., “Defect Analysis and Realistic Fault Model Extensions for Static Random Access Memories,” Records IEEE Int’l Workshop on Memory, Technology, Design and Testing, 2000, pp. 119–124.

Author information

Authors and Affiliations

Corresponding author

Additional information

This work has been partially funded by the French government under the framework of the MEDEA + A503 “ASSOCIATE” European program.

Simone Borri received the M.Sc. Degree (summa cum laude) in Electronics Engineering from the University of Pisa (Italy) in 1995. In 1997 he joined STMicroelectronics as a digital designer in the DSP development group of S.S.D. (formerly Parthus, now Ceva), Dublin, Ireland. From 1998 to 2000 he was with ST Microelectronics, Milan, Italy as ASIC DSP designer in the Car Communication business unit. Since 2000 he is with Infineon Technologies, Sophia-Antipolis, France as Staff design engineer in the embedded-SRAM design group. He has recently joined the Secure Mobile System Business Unit. His current interests include BIST, DFT techniques and SoC verification. Simone is an IEEE member since 1995.

Magali Hage-Hassan was born near Lyon (France) in 1979. She received a Master of Science degree of Microelectronics and Automatics from the Institute of Engineering Sciences of Montpellier in 2003. She is currently working for Infineon in the memory library department in Sophia-Antipolis. She participated to the European research project MEDEA associate. Hage-Hassan’s interest include memory test.

Luigi Dilillo was born in Barletta (Italy) in 1974. At this moment he is doing his last year of Ph.D. in the Microelectronics Department of the Laboratory of Informatics, Robotics and Microelectronics of Montpellier (LIRMM) in France. He received his degree in Electrical Engineering in 2001, at Politecnico di Torino (Italy). His researches include MEMS and digital circuits. At this moment he is working on delay-fault testing, and memory testing.

Patrick Girard is presently Researcher at CNRS (French National Center for Scientific Research), and works in the Microelectronics Department of the LIRMM (Laboratory of Informatics, Robotics and Microelectronics of Montpellier—France). His research interests include the various aspects of digital testing, with special emphasis on DfT, logic BIST, delay fault testing and diagnosis, low power testing and memory testing. He has authored and co-authored 1 book and more than 100 papers on these fields. He has managed several European research projects and industrial research contracts. He is Editor-in-Chief of JOLPE—Journal of Low Power Electronics, and Associate Editor of JEC—Journal of Embedded Computing. He will serve as Program vice-Chair for the International Conference on Embedded And Ubiquitous Computing in 2005 and as Program Chair for the IEEE International Workshop on Electronic Design, Test & Applications in 2006. He is also topic chair of two European conferences (DATE and ETS) and is member of the program committee of several other international conferences. Patrick GIRARD obtained the Ph.D. degree in microelectronics from the University of Montpellier in 1992 and the “Habilitation à Diriger des Recherches” degree from the University of Montpellier in 2003.

Serge Pravossoudovitch was born in 1957. He is currently professor in the electrical and computer engineering department of the University of Montpellier and his research activities are performed at LIRMM (Laboratoire d’Informatique, de Robotique et de Microélectronique de Montpellier). He got the Ph.D. degree in electrical engineering in 1983 for his work on symbolic layout for IC design. Since 1984, he is working in the testing domain. He obtained the “doctorat d’état” degree in 1987 for his work on switch level automatic test pattern generation. He is presently interested in memory testing, delay fault testing, design for testability and power consumption optimization. He has authored and co-authored numerous papers on these fields, and has supervised several Ph.D. dissertations. He has also participated to several European projects (Microelectronic regulation, Esprit, Medea).

Arnaud Virazel was born in Montpellier (France) in 1974. He is presently assistant professor at the university of Montpellier, and works with the LIRMM (Laboratoire d’Informatique, de Robotique et de Microélectronique de Montpellier). He received the B.Sc. (1995) and the M.Sc. (1997) degrees in Electrical Engineering and the Ph.D. (2001) degree in Microelectronics, all from the University of Montpellier/LIRMM. A. Virazel’s interests include delay testing, memory testing and power optimization during test.

Rights and permissions

About this article

Cite this article

Borri, S., Hage-Hassan, M., Dilillo, L. et al. Analysis of Dynamic Faults in Embedded-SRAMs: Implications for Memory Test. J Electron Test 21, 169–179 (2005). https://doi.org/10.1007/s10836-005-6146-1

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/s10836-005-6146-1