Abstract

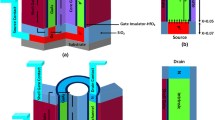

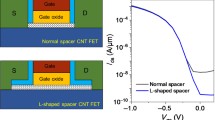

In this paper, we investigate the impacts of variation in the core gate thickness and germanium content on the performance of a Si1−xGex source/drain Si-nanotube junctionless field-effect transistor. A SiGe source/drain structure is combined with a core gate inside the nanotube to address and suppress the stringent issue of short-channel effects (SCEs). The effect of gate length, bias voltages, and Ge content on the subthreshold current, threshold voltage, and SCEs has also been studied by developing a compact analytical model including the quantum confinement effect. Our results highlight the utility of core gate and Si1−xGex source/drain to provide an additional degree of freedom to control SCEs in the nanoscale regime.

Similar content being viewed by others

References

Gnani, E., Gnudi, A., Reggiani, S., Baccarani, G.: Theory of the junctionless nanowire FET. IEEE Trans. Electron Dev. 58(9), 2903–2910 (2011)

Sahay, S., Kumar, M.J.: Controlling L-BTBT and volume depletion in nanowire JLFETs using core–shell architecture. 63(9), pp. 3790–3794 (2016)

Jazaeri, F., Barbut, L., Koukab, A., Sallese, J.-M.: Analytical model for ultra-thin body junctionless symmetric double gate MOSFETs in subthreshold regime. Solid-State Electron. 82(2), 103–110 (2013)

Lee, C.-W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., Colinge, J.-P.: Junctionless multigate field-effect transistor. Appl. Phys. Lett. 94(5), 053511–053512 (2009)

Rios, R., et al.: Comparison of junctionless and conventional trigate transistors with Lg down to 26 nm. IEEE Electron Dev. Lett. 32(9), 1170–1172 (2011)

Sahay, S., Kumar, M.J.: Realizing efficient volume depletion in SOI junctionless FETs. IEEE J. Electron Dev. Soc. 4(3), 110–115 (2016)

Yang, B., et al.: Vertical silicon-nanowire formation and gate-all-around MOSFET. IEEE Electron Dev. Lett. 29(7), 791–794 (2008)

Colinge, J.P., et al.: Nanowire transistors without junctions. Nat. Nanotechnol. 5(3), 225–229 (2010)

Hanna, A.N., Hussain, M.M.: Si/Ge hetero-structure nanotube tunnel field effect transistor. J. Appl. Phys. 117(1), 1–7 (2015)

Tekleab, D., Tran, H.H., Slight, J.W. et al.: Silicon nanotube MOSFET. U.S. Patent 0217468 (2012)

Fahad, H.M., Hussain, M.M.: High-performance silicon nanotube tunneling FET for ultralow-power logic applications. IEEE Trans. Electron Dev. 60(3), 1034–1039 (2013)

Sahay, S., Kumar, M.J.: Nanotube junctionless field effect transistor: proposal, design and investigation. IEEE Trans. Electron Dev. 64(3), 1851–1856 (2017)

Thakur, A., Dhiman, R.: SiGe/Si hetero nanotube JLFET for improved performance: proposal and investigation. Electron. Lett. 55(25), 1359–1361 (2019)

Thakur, A., Dhiman, R.: Design and performance analysis of SiGe source-drain hetero-structure nanotube junctionless FET. In: Proc. IEEE TENCON, India (2019)

Chang, T.-K.: A quasi-two-dimensional threshold voltage model for short-channel junctionless double-gate MOSFETs. IEEE Trans. Electron Dev. 59(9), 2284–2289 (2012)

Kumar, A., Bhushan, S., Tiwari, P.K.: A threshold voltage model of silicon-nanotube-based ultrathin double gate-all-around (DGAA) MOSFETs incorporating quantum confinement effects. IEEE Trans. Nanotechnol. 16(5), 868–875 (2017)

Li, C., Zhuang, Y., Di, S., Han, R.: Subthreshold behavior models for nanoscale short-channel junctionless cylindrical surrounding-gate MOSFETs. IEEE Trans. Electron Dev. 60(11), 3655–3662 (2013)

Hu, G., et al.: Analytical models for electric potential, threshold and subthreshold swing of junctionless surrounding -gate transistors. IEEE Trans. Electron Dev. 61(3), 688–695 (2014)

Singh, B., Gola, D., Singh, K., Goel, E., Kumar, S., Jit, S.: Analytical modeling of channel potential and threshold voltage of double-gate junctionless FETs with a vertical Gaussian-like doping profile. IEEE Trans. Electron Dev. 63(6), 2299–2305 (2016)

Kumar, M.J., Venkataraman, V., Nawal, S.: Impact of strain or Ge content on the threshold voltage of the strained-Si/SiGe bulk MOSFETs. IEEE Trans. Dev. Mater. Rel. 7(1), 181–187 (2007)

Nishiyama, A., et al.: SiGe source/drain structure for the suppression of the short channel effect of sub-0.1-μm P-channel MOSFETs. IEEE Trans. Electron Dev. 48(6), 1114–1120 (2001)

Shalchian, M., Jazaeri, F., Sallese, J.: Charge-based model for ultrathin junctionless DG FETs, including quantum confinement. IEEE Trans. Electron Dev. 65(9), 4009–4014 (2018)

Duarte, J.P., Kim, M.S., Choi, S.J., Choi, Y.K.: A compact model of quantum electron density at the subthreshold region for double-gate junctionless transistors. IEEE Trans. Electron Dev. 59(4), 1008–1012 (2012)

Kumar, A., Bhushan, S., Tiwari, P.K.: Drain current modeling of double gate-all-around (DGAA) MOSFETs. IET Circuit Dev. Syst. 13(4), 519–525 (2019)

Kumar, A., Bhushan, S., Tiwari, P.K.: Analytical modeling of subthreshold characteristics of ultra-thin double gate-all-around (DGAA) MOSFETs incorporating quantum confinement effects. Superlatt. Microstruct. 105, 567–578 (2017)

Choi, S.J., Moon, D., Kim, S., Duarte, J.P., Choi, Y.K.: Sensitivity of threshold voltage to nanowire width variation in junctionless transistor. IEEE Electron Dev. Lett. 32(2), 125–127 (2011)

Chanda, M., De, S., Sarkar, C.K.: Modeling of characteristic parameters for nano-scale junctionless double gate MOSFET considering quantum mechanical effect. J. Comput. Electron. 14(1), 262–269 (2015)

Acknowledgements

This work is an outcome of the research and development work undertaken in the project under the Visvesvaraya Ph.D. Scheme of Ministry of Electronics and Information Technology (MeitY), Government of India, being implemented by Digital India Corporation [Ref. No.: MeitY-PhD-3186].

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Appendices

Appendix 1

Appendix 2

Rights and permissions

About this article

Cite this article

Thakur, A., Dhiman, R. Impacts of core gate thickness and Ge content variation on the performance of Si1−xGex source/drain Si–nanotube JLFET. J Comput Electron 20, 237–247 (2021). https://doi.org/10.1007/s10825-020-01618-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-020-01618-y