Abstract

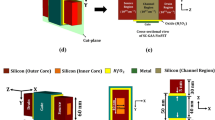

In this paper, we investigated the breakdown performance of novel nanoscale asymmetric InP high-electron-mobility transistors (HEMTs). The novel asymmetric InP HEMT features \(\Gamma \)-gate, heavily doped multilayer cap, \(n^{+}\)-type In\(_{0.52}\)Ga\(_{0.48}\)As source/drain (S/D) regions, InAs-rich composite channel, SiN passivation and double \(\delta \)-doping planes. The impact of asymmetric gate recess width on DC, RF and breakdown performance of novel asymmetric InP HEMT has been investigated using hydrodynamic carrier transport model along with other physical models such as Shockley–Read–Hall model, recombination models, high-field mobility model and density gradient model. Sentaurus TCAD simulations were carried out at room temperature for gate lengths of 50 and 20 nm in order to analyse the scalability of the new device architecture. In order to consider the quantum effects at nanoscale regime, density gradient model of eQuantum potential was used for TCAD simulations. \(L_{g}\) = 20 nm proposed HEMT achieved a peak \(g_{m}\) and \(I_\mathrm{DS}\) of 3470 mS/mm and 1300 mA/mm, respectively. The proposed HEMT has a \(f_{T}\) and \(f_\mathrm{max}\) of 749 and 1460 GHz, respectively. The \(L_{g}\) = 20 nm proposed HEMT also showed an ON-state and OFF-state breakdown voltages of 2.2 and 4.5 V, respectively, at a gate recess width of 150 nm. To the best of authors’ knowledge, this is the record combination of DC, RF and breakdown performance reported for InP HEMTs which makes them the most suitable transistors for future high-speed high-power applications.

Similar content being viewed by others

References

Ajayan, J., Nirmal, D.: A review of InP/InAlAs\(\backslash \)InGaAs based transistors for high frequency applications. Superlattices Microstruct. 86(10), 1–19 (2015)

Del Alamo, J.A.: Nanometre electronics with III-V compound semiconductors. Nature 479(7373), 317–323 (2011)

Sun, S.X., Ma, L.H., Cheng, C., Zhang, C., Zhong, Y.H., Li, Y.X., Ding, P., Jin, Z.: Numerical simulation of the impact of surface traps on the performance of InP-based high electron mobility transistors. Phys. Status Solidi A 1700322 (2017). doi:10.1002/pssa.201700322 (2017).

Ajayan, J., Nirmal, D.: 20 nm high performance enhancement mode InP HEMT with heavily doped S/D regions for future THz applications. Superlattices Microstruct. 100(15), 526–534 (2016)

Del Alamo, J.A., Antoniadis, D.A., Lin, J., Lu, W., Vard, A., Zhao, X.: Nanometer-scale III-V MOSFETs. J. Electron Devices Soc. 4(5), 2015–214 (2016)

Ajayan, J., Nirmal, D., Prajoon, P., Charles Pravin, J.: Analysis of nanometer-scale InGaAs/InAs/InGaAs composite channel MOSFETs using high-K dielectrics for high speed applications. Int. J. Electron. Commun. (AEÜ) 79, 151–157 (2017)

Ajayan, J., Nirmal, D.: 20nm T-gate composite channel enhancement-mode metamorphic HEMT on GaAs substrates for future THz applications. J. Comput. Electron. 15(4), 1291–1296 (2016)

Ajayan, J., Nirmal, D.: 20nm enhancement mode metamorphic GaAs HEMT with highly doped InGaAs source/drain regions for high frequency applications. Int. J. Electron. 104(3), 504–512 (2017)

Mei, X., Yoshida, W.: First demonstration of amplification at 1 THz using 25-nm InP high electron mobility transistor process. IEEE Electron Device Lett. 36(4), 327 (2015)

Xu, D., Xiaoping, Y.: 50-nm self-aligned high electron-mobility transistors on GaAs substrates with extremely high extrinsic transconductance and high gain. Int. J. High Speed Electron. Syst. 20(3), 393–398 (2011)

Dong, X., Yang, X.: 50-nm asymmetrically recessed metamorphic high-electron mobility transistors with reduced source-drain spacing: performance enhancement and tradeoffs. IEEE Trans. Electron Devices 59(1), 128–138 (2012)

Lin, J., Cai, X., Wu, Y., Antoniadis, D.A., del Alamo, Jesus A.: Record maximum transconductance of 3.45 mS/um for III-V FETs. IEEE Electron Device Lett. 37(4), 381–384 (2016)

Rodwell, M.J.W., et al.: Nanometer InP electron devices for VLSI and THz applications. In: Proceedings of the 72\(^{nd}\) Annual Device Research Conference (DRC), p. 215–216, June (2014)

Kim, D.-H., del Alamo, J.A.: Lateral and vertical scaling of In\(_{0.7}\)Ga\(_{0.3}\)As HEMTs for post-Si-CMOS logic applications. IEEE Trans. Electron Devices 55(10), 2546–2553 (2008)

Lin, J., Antoniadis, D.A., del Alamo, J.A.: Impact of intrinsic channel scaling on InGaAs quantum-well MOSFETs. IEEE Trans. Electron Devices 62(11), 3470–3476 (2015)

Kim, D.H., Del Alamo, J.A.: Performance evaluation of 50 nm In\(_{0.7}\)Ga\(_{0.3}\) as HEMTs for beyond CMOS logic applications. In: Proceedings of IEDM Technical Digest, p. 767 (2005)

Sun, S.X., Ji, H.F., Yao, H.J., Li, S., Jin, Z., Ding, P., Zhong, Y.H.: Physical modeling of direct current and radio frequency characteristics for InP-based InAlAs/InGaAs HEMTs. Chin. Phys. B 25(10), 108501-1-108501-4 (2016)

Kim, D.H., del Alamo, J.A.: 30-nm InAs PHEMTs with f\(_{T}\)=644 GHz and fmax=681 GHz. IEEE Electron Device Lett. 31(8), 806 (2010)

Kim, D.H., del Alamo, J.A.: 30-nm InAs pseudomorphic HEMTs on an InP substrate with a current-gain cut off frequency of 628 GHz. IEEE Electron Device Lett. 29(8), 830 (2008)

Lai, R., Mei, X.B., Deal, W.R.: Sub 50 nm InP HEMT device with fmax greater than 1 THz. In: Proceedings of IEDM Technical Digest, p. 609 (2007)

Deal, W.: THz monolithic integrated circuits using InP high electron mobility transistors. IEEE Tans. Terahertz Sci. Technol. 1(1), 25 (2011)

Kim, T.W., Kim, D.H., Del Alamo, Jesus A.: Logic characteristics of 40 nm thin-channel InAs HEMTs. In: Proceedings of IPRM, p. 496 (2010)

Deal, W.R., Leong, K.: Low noise amplification at 0.67 THz using 30 nm InP HEMTs. IEEE Microw. Wirel. Compon. Lett. 21(7), 368 (2011)

Chang, E.Y., Kuo, Chien-I: InAs thin-channel high-electron-mobility transistors with very high current-gain cutoff frequency for emerging submillimeter-wave applications. Appl. Phys. Express 6, 034001e1 (2013)

Radisic, V., Leong, K.: Power amplification at 0.65 THz using InP HEMTs. IEEE Trans. Microw. Theory Tech. 60(3), 724 (2012)

Shinohara, K., Yamashita, Y.: Extremely high speed lattice matched InGaAs/InAlAs high electron mobility transistors with 472 GHz cutoff frequency. Jpn. J. Appl. Phys. 41, L437 (2002)

Yamashita, Y., Endoh, A.: Pseudomorphic In\(_{0.52}\)Al\(_{0.48}\)As/In\(_{0.7}\)Ga\(_{0.3}\)As HEMTs with an ultra high f\(_{T}\) of 562 GHz. IEEE Electron Device Lett. 23(10), 573 (2002)

Kim, D.H., Del Alamo, J.A.: The impact of side-recess spacing on the logic performance of 50 nm In0.7Ga0.3As HEMTs. In: Proceedings of IPRM, p. 177 (2006)

Deal, W.R.: Demonstration of a 0.48 THz amplifier module using InP HEMT transistors. IEEE Microw. Wirel. Compon. Lett. 20(5), 289 (2010)

Shinohara, K., Yamashita, Y.: 547 GHz fT In0.7Ga0.3As/In0.52Al0.48As HEMTs with reduced source and drain resistance. IEEE Electron Device Lett. 25, 241 (2004)

Nishio, Y., Tange, T.: Comparison between theoretical and experimental results for energy states of two-dimensional electron gas in pseudomorphically strained InAs high-electron-mobility transistors. Jpn. J. Appl. Phys. 53, 04EF09e1 (2014)

Chen, K.J., Enoki, T.: High performance InP based enhancement mode HEMTs using non-alloyed ohmic contacts and Pt-Based buried gate technologies. IEEE Trans. Electron Devices 43(2), 252 (1996)

Harada, N., Kuroda, S.: Pt-based gate enhancement mode InAlAs/InGaAs HEMTs for large scale integration. In: Proceedings of IPRM, p. 377 (1991)

Kim, D.H., del Alamo, J.A.: 30-nm E-mode InAs PHEMTs for THz and future logic applications. In: Proceedings of IEDM Technical Digest, p. 719 (2008)

Suemitsu, T., Yokoyama, H.: High performance 0.1-mm gate enhancement-mode InAlAs/InGaAs HEMTs using two-step recessed gate technology. IEEE Trans. Electron Devices 46(6), 1074 (1999)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Ajayan, J., Ravichandran, T., Prajoon, P. et al. Investigation of breakdown performance in \(L_{g}\)= 20 nm novel asymmetric InP HEMTs for future high-speed high-power applications. J Comput Electron 17, 265–272 (2018). https://doi.org/10.1007/s10825-017-1086-4

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-017-1086-4