Abstract

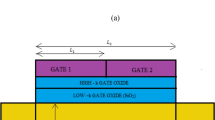

We present modeling and simulation of a cylindrical surrounding double-gate (CSDG) metal–oxide–semiconductor field-effect transistor (MOSFET) with vacuum gate dielectric instead of silicon dioxide, revealing some improvement in hot-carrier reliability. The CSDG MOSFET incorporates an extra inner control gate compared with the cylindrical surrounding gate (CSG) MOSFET, resulting in improved drain current in the channel. The radiofrequency (RF) performance of the CSDG MOSFET is obtained and compared for different dielectrics such as vacuum, silicon dioxide, and high-k material. The RF performance of the CSDG MOSFETs is evaluated on the basis of transconductance, capacitance, cutoff frequency, and drain current. Also, the surface potential and electric field are evaluated analytically at higher drain bias. It is shown that, with decreasing gate dielectric constant, the threshold voltage decreases while hot-carrier parameters such as the electron temperature are reduced at the drain side.

Similar content being viewed by others

References

Taur, Y.: An analytical solution to a double-gate MOSFET with undoped body. IEEE Electron Device Lett. 21(5), 245–247 (2000)

Han, J.W., Kim, C.J., Choi, Y.K.: Universal Potential Model in Tied and Separated Double-Gate MOSFETs with Consideration of Symmetric and Asymmetric Structure. IEEE Trans. Electron Devices 55(6), 1472–1479 (2008)

Doyle, B.S., Datta, S., Doczy, M., Hareland, S., Jin, B., Kavalieros, J., Linton, T., Murthy, A., Rios, R., Chau, R.: High Performance Fully-Depleted Tri-Gate CMOS Transistors. IEEE Electron Device Lett. 24(4), 263–265 (2003)

Colinge, J.P.: Multiple-gate SOI MOSFETs. Solid-State Electron. 48, 897–905 (2004)

Lee, H., Yu, L. E., Ryu, S. W., Han, J. W., Jeon, K., Jang, D.Y., Choi, Y. K.: Sub-5nm all-around gate FinFET for ultimate scaling. IEEE Symposium on VLSI Technology, Digest of Technical Papers 58-59 (2006)

Li, C., Zhuang, Y., Han, R.: Cylindrical surrounding-gate MOSFETs with electrically induced source/drain extension. Microelectron. Eng. 42, 341–346 (2011)

Kranti, A., Haldar, S., Gupta, R.S.: An accurate 2D analytical model for short channel thin film fully depleted cylindrical/surrounding gate (CGT/SGT) MOSFET. Microelectron. J. 32, 305–313 (2001)

Fahad, H.M., Smith, C.E., Rojas, J.P., Hussain, M.M.: Silicon Nano-tube Field Effect Transistor with Core Shell Gate Stacks for Enhanced High-Performance Operation and Area Scaling Benefits. Nano Lett. 11, 4393–4399 (2011)

Ge, L.J., Fossum, G., Gamiz, F.: Mobility Enhancement via Volume Inversion in Double-Gate MOSFETs. IEEE international SOI conference, USA. (2003)

Srivastava, V.M., Yadav, K.S., Singh, G.: Design and performance analysis of cylindrical surrounding double-gate MOSFET for RF Switch. Microelectron. J. 42, 1124–1135 (2011)

Chen, Y., Kang, W.: Experimental study and modeling of double-surrounding gate and cylindrical silicon-on-nothing MOSFETs. Microelectron. Eng. 97, 138–143 (2012)

Tekleab, D.: Device Performance of Silicon Nanotube Field Effect Transistor. IEEE Electron Device Lett. 35(5), 506–508 (2014)

Ernst, T., Cristoloveanu, S., Ouisse, T., Murase, K.: Ultimately thin double gate SOI MOSFETs. IEEE Trans. Electron Devices 50(3), 830–836 (2003)

Xia, Y., Kalihari, V., Frisbie, C.D.: Tetracene air-gap single-crystal field-effect transistors. App. Phy. Lett. 90, 162106 (2007)

Han, J.W., Ahn, J.H., Choi, Y.K.: Damage immune field effect transistors with vacuum gate dielectric. J. Vacuum Sc. Tech. B. 29, 011014 (2011)

Gautam, R., Saxena, M., Gupta, R.S., Gupta, M.: Gate All Around MOSFET with Vacuum Gate Dielectric for Improved Hot Carrier Reliability and RF Performance. IEEE Trans. Electron Devices 60, 1820–1827 (2013)

Han, J.W., Moon, D.I., Oh, J.S., Choi, Y.K., Meyyappan, M.: Vacuum gate dielectric gate-all-around nanowire for hot carrier injection and bias temperature instability free transistor. App. Phy. Lett. 104, 253506 (2014)

ATLAS: 3D Device Simulator. SILVACO International (2015)

Singh, N., Agarwal, A., Bera, L.K., Liow, T.Y., Yang, R., Rustagi, S.C., Kwong, D.L.: High-performance fully depleted silicon nanowire (diameter_5 nm) gate all-around CMOS devices. IEEE Electron Device Lett. 27, 383–386 (2006)

Kumar, J., Kedzierski, S., Laux, E.: Quantum-based simulation analysis of scaling in ultrathin body device structures. IEEE Trans. Electron Devices 52, 614–617 (2005)

Hamid, E.L., Hamdy, A., Iniguez, B., Guitart, J.R.: Analytical model of the threshold voltage and sub-threshold swing of undoped cylindrical gate-all-around based MOSFETs. IEEE Trans. Electron Devices 54, 572–579 (2007)

Ren, H., Hao, Y.: The influence of geometric structure on the hot carrier-effect immunity for deep-sub-micron grooved gate PMOSFET. Solid-State Electron. 46(5), 665–673 (2002)

Tam, S., Ko, P.K., Hu, C.: Lucky-electron model of channel hot electron injection in MOSFET’s. IEEE Trans. Electron Devices 31(9), 1116–1125 (1984)

Widiez, J., Poiroux, T., Vinet, M., Mouis, M., Deleonibus, S.: Experimental Comparison between Sub-0.1-Ultrathin SOI Single-and Double-Gate MOSFETs: Performance and Mobility. IEEE Trans. Nanotech 52, 643–648 (2006)

Iwai, H.: Roadmap for 22 nm and beyond. Microelectron. Eng. 86, 1520–1528 (2009)

Acknowledgments

The authors are grateful to CSIR, Govt. of India and University Grant Commission (UGC), Govt. of India for providing financial support to carry out this work.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Verma, J.H.K., Haldar, S., Gupta, R.S. et al. Modeling and simulation of cylindrical surrounding double-gate (CSDG) MOSFET with vacuum gate dielectric for improved hot-carrier reliability and RF performance. J Comput Electron 15, 657–665 (2016). https://doi.org/10.1007/s10825-016-0803-8

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-016-0803-8