Abstract

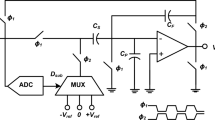

A mix-signal foreground calibration method for charge domain pipelined ADC is proposed. The calibration method can calibrate the common-mode and differential-mode charge errors caused by capacitor mismatches stage by stage based on a binary search. Common-mode and differential-mode charge errors caused by the capacitor mismatches in charge domain pipelined substage circuits can be compensated for by the proposed calibration method. Based on the proposed calibration method, a 14-bit 250-MS/s charge domain pipelined ADC is designed and realized in a 1P6M 0.18 μm CMOS process. Test results show that the 14-bit 250-MS/s ADC achieves a signal-to-noise ratio of 70.5 dBFS and a spurious free dynamic range of 88.7 dB, with 20.1 MHz input at 250-MS/s, while the ADC core consumes 235 mW of power and occupies an area of 3.2 mm2.

Similar content being viewed by others

References

Ali, A. M. A., Morgan, A., Dillon, C., et al. (2010). A 16b 250MS/s IF-sampling pipelined A/D converter with background calibration. In ISSCC 2010, Dig. Tech. Papers (pp. 292–293).

Manar, E., Li, X. P., Shigenobu, K., et al. (2015). A 90 dB SFDR 14-b 500 MS/s BiCMOS switched-current pipelined ADC. In ISSCC 2015, Dig. Tech. Papers (pp. 286–287).

Li, W. T., Li, F. L., Yang, C. Y., et al. (2015). An 85 mW 14-bit 150 MS/s pipelined ADC with a merged first and second MDAC. China Communications, 12(5), 14–22.

Ali, A. M. A., Dinc, H., Bhoraskar, P., et al. (2014). A 14-b 1 GS/s RF sampling pipelined ADC with background calibration. In ISSCC 2014, Dig. Tech. Papers (pp. 482–483).

Ali, A. M. A., Dinc, H., Bhoraskar, P., et al. (2016). A 14-bit 2.5GS/s and 5GS/s RF sampling ADC with background calibration and dither. In IEEE Symposium on VLSI Circuits. Dig. Tech. Papers (pp. 1–2).

Wu, J. F., Chou, A., Li, T. W., et al. (2016). A 4GS/s 13b pipelined ADC with capacitor and amplifier sharing in 16 nm CMOS. In ISSCC 2016, Dig. Tech. Papers (pp. 466–468).

Anthony, M., Kohler, E., Kurtze, J., et al. (2008). A process-scalable low-power charge-domain 13-bit pipeline ADC. In IEEE Symposium on VLSI Circuits. Dig.Tech. Papers (pp. 222–223)

Chen, Z. H., Yu, Z. G., Huang, S. R., et al. (2012). A novel boosted charge transfer circuit for high speed charge domain pipelined ADC. Chinese Journal of Electronics, 21(4), 627–632.

Chen, Z. H., Yu, Z. G., Huang, S. R., et al. (2012). A PVT insensitive boosted charge transfer for high speed charge-domain pipelined ADCs. IEICE Electronics Express, 9(6), 565–571.

Huang, S., Zhang, H., Chen, Z., et al. (2015). A 10-bit 250MS/s charge-domain pipelined ADC with replica controlled PVT insensitive BCT circuit. Journal of Semiconductors, 36(5), 055012–7.

Yu, Z.-G., Su, X.-B., Chen, Z.-H., Zou, J., Wei, J.-H., Zhang, H., et al. (2018). A 12-bit 250MS/s charge- domain pipelined analog-to-digital converter with feed-forward common-mode charge control. Tsinghua Science and Technology, 23(1), 598–609.

Zhang, Y., Chen, C., Yu, B., et al. (2012). A 14-bit 200-MS/s time-interleaved ADC with sample-time error calibration. Journal of Semiconductors, 33(10), 035009–9.

Zheng, X. Q., Wang, Z. J., Li, F. L., et al. (2016). A 14-bit 250 MS/s pipelined ADC with a merged first and second MDAC. IEEE Transactions on Circuits and Systems—I: Regular Papers, 63(9), 1381–1392.

Acknowledgements

This work is supported by the National Science Foundation of China (No. 61704161) and Major Science and Technology Projects in Anhui Province (Nos. 18030901006, 201904b11020007).

Author information

Authors and Affiliations

Corresponding authors

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Chen, Zh., Wu, H., Zhang, H. et al. A 14-bit 250-MS/s charge-domain pipelined ADC with mix-signal foreground calibration. Analog Integr Circ Sig Process 101, 283–295 (2019). https://doi.org/10.1007/s10470-019-01530-x

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-019-01530-x