Abstract

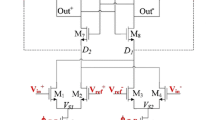

This paper presents a low voltage double-tail dynamic comparator (DTDC) for fast and power-efficient data conversion. The amplification stage of the proposed DTDC is designed using self-biasing technique, which helps to reduce external biasing requirement to bias bulk/gate of the transistors. The self-biasing technique controls threshold voltage (Vth) of the transistors either for fast switching (low-Vth) or for low power dissipation (high-Vth). The latch stage of the proposed DTDC is designed with novel dynamic CMOS inverters to improve the regeneration speed. The mathematical equations for delay and offset voltage are derived for the proposed DTDC and improvements are mentioned. The proposed DTDC is designed in CADENCE and simulated with SPECTRE using 45 nm CMOS process technology at the low power supply of 0.8 V to verify the outcomes. The simulation results reveal that the delay and power dissipation of the proposed DTDC are 166.29 pS and 2.3 µW respectively. The analysis of 1-sigma offset error is performed using Monte-Carlo simulation. Here, the mismatch and process variation are considered and the samples are generated randomly till 200 samples (runs). Additionally, the peak input voltage error due to kickback noise is 0.219 mV for a differential input voltage of 5 mV.

Similar content being viewed by others

References

Zhu, Z., Qiu, Z., Shen, Y., & Yang, Y. (2014). A 2.67 fJ/c.-s. 27.8 kS/s 0.35 V 10-bit successive approximation register analogue-to-digital converter in 65 nm complementary metal oxide semiconductor. IET Circuits, Devices and Systems, 8(6), 427–434.

Zhu, Z., Liu, M., Wang, Q., & Yang, Y. (2014). A single-channel 8-bit 660MS/s asynchronous SAR ADC with pre-settling procedure in 65 nm CMOS. Microelectronics Journal, 45(7), 880–885.

Ragab, K., Chen, L., Sanyal, A., & Sun, N. (2015). Digital background calibration for pipelined ADCs based on comparator decision time quantization. IEEE Transactions on Circuits and Systems II: Express Briefs, 62(5), 456–460.

Yang, B.-D. (2014). 250-mV supply subthreshold CMOS voltage reference using a low-voltage comparator and a charge-pump circuit. IEEE Transactions on Circuits and Systems II: Express Briefs, 61(11), 850–854.

Yamamoto, K., & Carusone, A. (2012). A 1-1-1-1 MASH delta-sigma modulator with dynamic comparator-based OTAs. IEEE Journal of Solid-State Circuits, 47(8), 1866–1883.

Kao, C.-K., Fu, K.-L., & Liu, S.-I. (2014). A 2 × 25 Gb/s clock and data recovery with background amplitude-locked loop. In IEEE Asian solid-state circuits conference (A-SSCC) (pp. 281–284).

Venkateswaran, P., Nagaria, R. K., Sanyal, S. K., & Nandi, R. (2003). Dual-input single-tunable integrators and differentiators using current-feedback amplifier. International Journal of Electronics, 90(2), 109–115.

Venes, A. G. W., & van de Plassche, R. J. (1996). An 80-MHz, 80-mW, 8-b CMOS folding A/D converter with distributed track-and-hold preprocessing. IEEE Journal of Solid-State Circuits, 31(12), 1846–1853.

Kostopoulos, G. K. (1984). Design and analysis nomograms for pulse-width and frequency modulation using the 555 timer. IEEE Circuits and Systems Magazine, 6(2), 4–11.

Ding, Z., Rhee, W., & Wang, Z. (2018). A VCO-dedicated digital LDO with multi-comparator coarse loop and 1-bit ΔΣ fine loop for robust frequency generation. In 2018 IEEE MTT-S international wireless symposium (IWS), Chengdu (pp. 1–4).

Eijselendoorn, J., & Dulk, R. C. D. (1982). Improved phase-locked loop performance with adaptive phase comparators. IEEE Transactions on Aerospace and Electronic Systems, AES-18(3), 323–332.

Schinkel, D., Mensink, E., Klumperink, E., Van Tuijl, E., & Nauta, B. (2007). A double-tail latch-type voltage sense amplifier with 18 ps setup+ hold time.” In Solid-state circuits conference, 2007. ISSCC 2007. Digest of technical papers. IEEE international, San Francisco, CA (pp. 314–605).

Babayan-Mashhadi, S., & Lotfi, R. (2014). Analysis and design of a low-voltage low-power double-tail comparator. IEEE Transactions on Very Large Scale Integration VLSI Systems, 22(2), 343–352.

Xu, D., Xu, S., & Chen, G. (2015). High-speed low-power and low-power supply voltage dynamic comparator. Electronics Letters, 51(23), 1914–1916.

Khorami, A., & Sharifkhani, M. (2016). High-speed low-power comparator for analog to digital converters. AEU-International Journal of Electronics and Communications, 7, 886–894.

Khorami, A., & Sharifkhani, M. (2016). Low-power technique for dynamic comparators. Electronics Letters, 52(7), 509–511.

Huang, S., Diao, S., & Lin, F. (2016). An energy-efficient high-speed CMOS hybrid comparator with reduced delay time in 40-nm CMOS process. Analog Integrated Circuits and Signal Processing, 1–8.

Jain, R., Dubey, A. K., Varshney, V., & Nagaria, R. K. (2017). Design of low-power high-speed double-tail dynamic CMOS comparator using novel latch structure. In 2017 4th IEEE Uttar Pradesh section international conference on electrical, computer and electronics (UPCON) (pp. 217–222), Mathura.

Dubey, A. K., & Nagaria, R. K. (2018). Optimization for offset and kickback-noise in novel CMOS double-tail dynamic comparator: A low-power, high-speed design approach using bulk-driven load. Microelectronics Journal, 78, 1–10.

Gupta, R., & Singh, C. (2017). Analysis and design of power gated low-power, high performance latch dynamic double-tail comparator. International Journal on Recent and Innovation Trends in Computing and Communication, 5(6), 786–793.

Savani, V., & Devashrayee, N. M. (2017). Analysis and design of low-voltage low-power high-speed double tail current dynamic latch comparator. Analog Integrated Circuits and Signal Processing, 93(2), 287–298.

Gandhi, P. P., & Devashrayee, N. M. (2018). A novel low offset low power CMOS dynamic comparator. Analog Integrated Circuits and Signal Processing, 96(1), 147–158.

Khorami, A., & Sharifkhani, M. (2018). A low-power technique for high-resolution dynamic comparators. International Journal of Circuit Theory and Applications, 46(10), 1777–1795.

Rabbi, F., et al. (2018). Design of a low-power ultra high speed dynamic latched comparator in 90-nm CMOS technology. In 2018 IEEE International Conference on Computer, Communication, Chemical, Material and Electronic Engineering (IC4ME2).

Savani, V., & Devashrayee, N. M. (2018). Design and analysis of low-power high-speed shared charge reset technique based dynamic latch comparator. Microelectronics Journal, 74, 116–126.

Rahman, L. F., Reaz, M. B. I., Yin, C. C., Marufuzzaman, M., & Rahman, M. A. (2014). A high-speed and low-offset dynamic latch comparator. The Scientific World Journal, 2014.

Figueiredo, P. M., & Vital, J. C. (2006). Kickback noise reduction techniques for CMOS latched comparators. IEEE Transactions on Circuits and Systems II: Express Briefs, 53(7), 541–545.

Dubey, A. K., & Nagaria, R. K. (2018). Enhanced gain low-power CMOS amplifiers: A novel design approach using bulk-driven load and introduction to GACOBA technique. Journal of Circuits, Systems and Computers (JCSC), 27(13), 1850204.

Acknowledgements

The authors are indebted to Ministry of Electronics and Information Technology (MeitY), Govt. of India, New Delhi, for providing research funds. The authors would also thank the PARAM Lab and VLSI Lab of MN National Institute of Technology Allahabad for providing us the research environment and computational infrastructure.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Dubey, A.K., Nagaria, R.K. Low-power high-speed CMOS double tail dynamic comparator using self-biased amplification stage and novel latch stage. Analog Integr Circ Sig Process 101, 307–317 (2019). https://doi.org/10.1007/s10470-019-01518-7

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-019-01518-7