Abstract

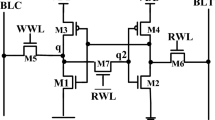

This paper presents a novel 9T static random access memory (SRAM) cell consisting of a single ended isolated read bit line with 2T read port for improving stability and a tail transistor for saving power. In the proposed design owing to the use of separate bitlines, the storing node voltage has not been affected during active mode operation. In the idle (hold) mode the static power dissipation of SRAM cell has been drastically reduced due to the formation of stack between tail transistor and internal latch. The proposed design has been verified by cadence virtuoso tool using UMC 65 nm CMOS technology. It provides a 42% and 34% improvement in write stability when compared to basic 6T and ultralow voltage (UV) 9T SRAM cells respectively. It has been observed that, the read stability is improved by 12% when compared to basic 6T SRAM cell and penalty of 10% when compared to UV 9T SRAM cell. A reduction of 22% in static power dissipation has also been observed in proposed design as compared to basic 6T SRAM cell when designed at same technology. This paper has also been proposed a mathematical modelling for validating the proposed design.

Similar content being viewed by others

References

Maroof, N., & Kong, B. (2017). 10T SRAM using half-VDD precharge and row-wise dynamically powered read port for low switching power and ultralow RBL leakage. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 25(4), 1193–1203.

Gupta, S., Gupta, K., & Pandey, N. (2017). A 32-nm Subthreshold 7T SRAM bit cell with read assist. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 25(12), 3473–3483.

Oh, T. W., et al. (2017). Power-gated 9T SRAM cell for low-energy operation. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 25(3), 1183–1187.

Senousy, R. E., Ibrahim, S., & Anis, W. (2016). Stability analysis and design methodology of near-threshold 6T SRAM cells. In 2016 28th International conference on microelectronics (ICM), Giza (pp. 225–228).

Arif, S., & Pal, S. (2015). Variation-resilient CNFET-based 8T SRAM cell for ultra-low-power application. In 2015 International conference on signal processing and communication engineering systems, Guntur (pp. 147–151).

Pal, S., & Islam, A. (2016). Variation tolerant differential 8T SRAM cell for ultralow power applications. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 35(4), 549–558.

Saeidi, R., Sharifkhani, M., & Hajsadeghi, K. (2014). A subthreshold symmetric SRAM cell with high read stability. IEEE Transactions on Circuits and Systems II: Express Briefs, 61(1), 26–30.

Tu, M., et al. (2012). A single-ended disturb-free 9T subthreshold SRAM with cross-point data-aware write word-line structure, negative bit-line, and adaptive read operation timing tracing. IEEE Journal of Solid-State Circuits, 47(6), 1469–1482.

Wang, B., et al. (2015). Design of an ultra-low voltage 9T SRAM with equalized bitline leakage and CAM-assisted energy efficiency improvement. IEEE Transactions on Circuits and Systems I: Regular Papers, 62(2), 441–448.

Teman, A., et al. (2011). A 250 mV 8 kb 40 nm ultra-low power 9T supply feedback SRAM (SF-SRAM). IEEE Journal of Solid-State Circuits, 46(11), 2713–2726.

Chang, I. J., et al. (2009). A 32 kb 10T sub-threshold SRAM array with bit-interleaving and differential read scheme in 90 nm CMOS. IEEE Journal of Solid-State Circuits, 44(2), 650–658.

Kulkarni, J., et al. (2013). Dual-VCC 8T-bitcell SRAM array in 22 nm tri-gate CMOS for energy-efficient operation across wide dynamic voltage range. In 2013 Symposium on VLSI Technology, Kyoto (pp. C126–C127).

Chen, Y., et al. (2015). A 16 nm 128 Mb SRAM in high-k metal-gate FinFET technology with write-assist circuitry for low-VMIN applications. IEEE Journal of Solid-State Circuits, 50(1), 170–177.

Karl, E., et al. (2012). A 4.6 GHz 162 Mb SRAM design in 22 nm tri-gate CMOS technology with integrated active VMIN-enhancing assist circuitry. In 2012 IEEE international solid-state circuits conference, San Francisco, CA (pp. 230–232).

Bhavnagarwala, A. J., et al. (2008). A sub-600-mV, fluctuation tolerant 65-nm CMOS SRAM array with dynamic cell biasing. IEEE Journal of Solid-State Circuits, 43(4), 946–955.

Tu, M., et al. (2010). Single-ended subthreshold SRAM with asymmetrical write/read-assist. IEEE Transactions on Circuits and Systems I: Regular Papers, 57(12), 3039–3047.

Lorenzo, R., & Chaudhury, S. (2017). A novel 9T SRAM architecture for low leakage and high performance. Analog Integrated Circuits and Signal Processing, 92(2), 315–325.

Mansore, S. R., Gamad, R. S., & Mishra, D. K. (2017). A single-ended read decoupled 9T SRAM cell for low power applications. In 2017 IEEE international symposium on nanoelectronic and information systems (iNIS), Bhopal (pp. 220–223).

Grossar, E., et al. (2006). Read stability and write-ability analysis of SRAM cells for nanometer technologies. IEEE Journal of Solid-State Circuits, 41(11), 2577–2588.

Bikki, P., & Karuppanan, P. (2017). SRAM cell leakage control techniques for ultra low power application: A Survey. Circuits and Systems, 8, 23–52.

Ruchi, & Dasgupta, S. (2018). Compact analytical model to extract write static noise margin (WSNM) for SRAM cell at 45-nm and 65-nm nodes. IEEE Transactions on Semiconductor Manufacturing, 31(1), 136–143.

Jiao, H., Qiu, Y., & Kursun, V. (2016). Variations-tolerant 9T SRAM circuit with robust and low leakage SLEEP mode. In 2016 IEEE 22nd international symposium on on-line testing and robust system design (IOLTS), Sant Feliu de Guixols (pp. 39–42).

Anitha, D., Manjunathachari, K., Sathish Kumar, P., & Prasad, G. (2017). Design of low leakage process tolerant SRAM cell. Analog Integrated Circuits and Signal Processing, 93(3), 531–538.

Prasad, G., & Anand, A. (2015). Statistical analysis of low-power SRAM cell structure. Analog Integrated Circuits and Signal Processing, 82(1), 349–358.

Neuberger, G., Wirth, G., & Reis, R. (2014). Protecting chips against hold time violations due to variability. Netherlands: Springer.

Zhu, H., & Kursun, V. (2014). A comprehensive comparison of data stability enhancement techniques with novel nanoscale SRAM cells under parameter fluctuations. IEEE Transactions on Circuits and Systems I: Regular Papers, 61(5), 1473–1484.

Acknowledgements

The authors would like to express gratitude to Meity (Ministry of Electronics and Information Technology, Govt. of India) for providing support under SMDPC2SD project and for Visvesvaraya PhD Scheme.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Mishra, J.K., Srivastava, H., Misra, P.K. et al. Analytical modelling and design of 9T SRAM cell with leakage control technique. Analog Integr Circ Sig Process 101, 31–43 (2019). https://doi.org/10.1007/s10470-019-01483-1

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-019-01483-1