Abstract

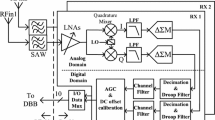

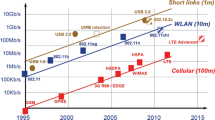

This paper presents a 3rd-order, 3-bit continuous-time (CT) \(\Updelta\Upsigma\) modulator for an LTE radio receiver. A return-to-zero (RZ) pulse, centered in the sampling period by a quadrature clock, is used in the innermost DAC to reduce the sensitivity to loop-delay variations in the modulator, and omit implementing the additional loop delay compensation usually needed in CT modulators. The performance and stability of the NRZ/NRZ/RZ feedback scheme is thoroughly analysed using a discrete-time model. The modulator has been implemented in a 65 nm CMOS process, where it occupies an area of 0.2 × 0.4 mm2. It achieves an SNR of 71 dB and an SNDR of 69 dB over a 9 MHz bandwidth with an oversampling ratio of 16, and a power consumption of 7.5 mW from a 1.2 V supply.

Similar content being viewed by others

Notes

The analysis is vastly simplified by disregarding the feedback path g 1 in the resonator (see Fig. 2(a)), which is allowed by the fact that such a path has an utterly negligible impact on h ct (1) for any realistic value of g 1.

Of course, the LO frequency varies with the frequency of the receive channel, which means that the modulator is clocked with slightly different frequencies according to the receive channel. The transition from the variable-clock domain in the modulator to the fixed-clock domain in the digital base-band can be performed with a Farrow interpolator [20, 21].

For higher absolute values of \(\epsilon\), the time-domain behavior shows an increasing discrepancy with the linear model, which predicts a lower in-band noise. This is because the signal-dependent quantizer gain, assumed to be unity in the linear analysis, drops below unity in the time-domain simulation [23]. However, by adjusting the quantizer gain in the linear model to the effective quantizer gain found in the time-domain simulation [24], the agreement between time-domain simulations and the linear analysis is recovered almost completely.

A resistor is less noisy than a MOS transistor working in the active region. In fact, if both must deliver a current IDAC with a voltage drop of Vod, the admittance G of the resistor is simply IDAC /Vod, while the transconductance gm of the MOS current source is twice as high, i.e. 2 IDAC /Vod. Assuming that the noise contributions are proportional to G and gm, respectively, with the same proportionality constant (assuming a channel noise factor γ = 1 for the MOS device), the MOS current source has twice as large noise power spectral density, compared to the resistive current source. Component-level simulations confirm this prediction with good quantitative agreement.

In the special case of identical DAC pulses for all feedback paths, the loop filter coefficients are found in a straightforward manner following the approach proposed by Pavan [46].

As already explained in Sect. 3. footnote 1, this path has no impact on h dt (1), which is the only sample compensated by a 4.

References

Cherry, J. A., Snelgrove, W. M. (2000). Continuous-delta-sigma modulators for high-speed A/D conversion. Norwell, MA, USA: Kluwer Academic Publishers.

Breems, L., Huijsing, J. (2001). Continuous-time sigma-delta modulation for A/D conversion in radio receivers. Norwell, MA, USA: Kluwer Academic Publishers.

Muñoz, F., Philips, K., Torralba, A. (2005). A 4.7 mW 89.5 dB DR CT complex \(\Updelta\Upsigma\) ADC With built-in LPF. ISSCC Digest of Technical Papers, San Francisco, CA, USA, Feb 6–10, pp. 500–613.

Ortmanns, M., Gerfers, F. (2005). Continuous-time sigma-delta A/D conversion: Fundamentals, performance limits and robust implementation. Dordrecht, The Netherlands: Springer.

Cherry, J. A., Snelgrove, W. M. (1999). Clock Jitter and quantizer metastability in continuous-time delta-sigma modulators. IEEE Transactions on Circuits and Systems II, 46(6), 661–676.

Cherry, J. A., Snelgrove, W. M. (1999). Excess loop delay in continuous-time delta-sigma modulators. IEEE Transactions on Circuits and Systems II, 46(4), 376–389.

Kauffman, J. G., Witte, P., Becker, J., Ortmanns, M. (2011). An 8.5 mW continuous-time \(\Updelta\Upsigma\) modulator with 25 MHz bandwidth using digital background DAC linearization to achieve 63.5 dB SNDR and 81 dB SFDR. IEEE Journal of Solid-State Circuits, 46(12), 2869–2881.

Mitteregger, G., Ebner, C., Mechnig, S., Blon, T., Holuigue, C., Romani, E. (2006). A 20-mW 640-MHz CMOS continuous-time \(\Upsigma\Updelta\) ADC with 20-MHz signal bandwidth, 80-dB dynamic range and 12-bit ENOB. IEEE Journal of Solid-State Circuits, 41(12), 2641–2649.

Fontaine, P., Mohieldin, A. N., Bellaouar, A. (2005). A low-noise low-voltage CT \(\Updelta\Upsigma\) modulator with digital compensation of excess loop delay. ISSCC Digest of Technical Papers, San Francisco, CA, USA Feb 6–10, pp. 498–613.

Vadipour, M., Chen, C., Yazdi, A., Nariman, M., Li, T., Kilcoyne, P., Darabi, H. (2008). A 2.1/3.2 mW delay-compensated GSM/WCDMA \(\Upsigma\Updelta\) analog–digital converter. Proceedings of the International Symposium on VLSI Circuits, June 18–20, pp. 180–181.

Ke, Y., Gao, P., Craninckx, J., der Plas, G. V., Gielen, G. (2010). A 2.8-to-8.5 mW GSM/Bluetooth/UMTS/DVB-H/WLAN fully reconfigurable CT\(\Updelta\Upsigma\) with 200 kHz to 20 MHz BW for 4G radios in 90 nm digital CMOS. Proceedings of the 2010 Symposium on VLSI Circuits, June 16-18, pp. 153–154.

Crombez, P., der Plas, G. V., Steyaert, M. S. J., Craninckx, J. (2010). A single-Bit 500 kHz–10 MHz multimode power-performance scalable 83-to-67 dB DR CT\(\Updelta\Upsigma\) for SDR in 90 nm Digital CMOS. IEEE Journal of Solid-State Circuits, 45(6), 1159–1171.

Benabes, P., Keramat, M., Kielbasa, R. (1997). A methodology for designing continuous-time sigma-delta modulators. European Design and Test Conference, EDTC, March 17–20, pp. 46–50.

Ranjbar, M., Oliaei, O. (2011). A multibit dual-feedback CT \(\Updelta\Upsigma\) modulator with lowpass signal transfer function. IEEE Transactions on Circuits and Systems I, 58(9), 2083–2095.

Keller, M., Buhmann, A., Sauerbrey, J., Ortmanns, M., Manoli, Y. (2008). A comparative study on excess-loop-delay compensation techniques for continuous-time sigma-delta modulators. IEEE Transactions on Circuits and Systems II, 55(11), 3480–3487.

Enright, D., Dedic, I., Allen, G. (2008). Continuous-time sigma-delta ADC in 1.2-V 90-nm CMOS with 61-dB peak SNDR and 74-dB dynamic range in 10-MHz bandwidth. Fujitsu Scientific and Technical Journal , 44-3, 264–273.

Pavan, S., Krishnapura, N., Pandarinathan, R., Sankar, P. (2008). A power optimized continuous-time \(\Updelta\Upsigma\) ADC for audio applications. IEEE Journal of Solid-State Circuits, 43(2), 351–360.

Ortmanns, M., Gerfers, F., Manoli, Y. (2004). Compensation of finite gain-bandwidth induced errors in continuous-time sigma-delta modulators. IEEE Transactions on Circuits and Systems I, 51(6), 1088–1099.

Witte, P., Kauffman, J. G., Becker, J., Manoli, Y., Ortmanns, M. (2012). A 72 dB-DR \(\Updelta\Upsigma\) CT modulator using digitally estimated auxiliary DAC linearization achieving 88fJ/conv in a 25 MHz BW. ISSCC Digest of Technical Papers, Feb 19–23, pp. 154–155.

Rajamani, K., Lai, Y.-S., Farrow, C. W. (2000). An efficient algorithm for sample rate conversion from CD to DAT. IEEE Signal Processing Letters., 7(10), 288–290.

Nilsson, M., Mattisson, S., Klemmer, N., Anderson, M., Arnborg, T., Caputa, P., Ek, S., Fan, L., Fredriksson, H., Garrigues, F., Geis, H., Hagberg, H., Hedestig, J., Huang, H., Kagan, Y., Karlsson, N., Kinzel, H., Mattsson, T., Mills, T., Mu, F., Mårtensson, A., Nicklasson, L., Oredsson, F., Ozdemir, U., Park, F., Pettersson, T., Påhlsson, T., Pålsson, M., Ramon, S., Sandgren, M., Sandrup, P., Stenman, A.-K., Strandberg, R., Sundström, L., Tillman, F., Tired, T., Uppathil, S., Walukas, J., Westesson, E., Zhang, X., Andreani, P. (2011). A 9-band WCDMA/EDGE transciever supporting HSPA evolution. ISSCC Digest of Technical Papers, San Francisco, CA, USA, Feb 19–23, pp. 366–367.

Schreier, R. (2000). The delta-sigma toolbox for MATLAB. http://www.mathworks.com/matlabcentral/fileexchange/.

Gao, W., Shoaei, O., Snelgrove, W. M. (1997). Excess loop delay effects in continuous-time delta-sigma modulators and the compensation solution. Proceedings of IEEE International Symposium on Circuits and Systems, ISCAS’97, Hong Kong, June 9–12, pp. 65–68.

Schreier, R., Temes, G. C. (2005). Understanding delta-sigma data converters. New York, USA: Wiley.

Andersson, M., Anderson, M., Sundström, L., Andreani, P. (2012). A 7.5 mW 9 MHz CT \(\Updelta\Upsigma\) modulator in 65 nm CMOS with 69 dB SNDR and reduced sensitivity to loop delay variations. Proceedings of IEEE A-SSCC, pp. 245–248.

Choi, T. C., Kaneshiro, R. T., Brodersen, R. W., Gray, P. R., Jett, W. B., Wilcox, M. (1983). High-frequency CMOS switched-capacitor filters for communications application. IEEE Journal of Solid-State Circuits, SC-18(6), 652–664.

Shettigar, P., Pavan, S. (2012). Design techniques for wideband single-bit continuous-time \(\Updelta\Upsigma\) modulators with FIR feedback DACs. IEEE Journal of Solid-State Circuits, 47(12), 2865–2879.

Breems, L. J., van der Zwan, E. J., Huijsing, J. H. (2000). A 1.8-mW CMOS \(\Updelta\Upsigma\) modulator with integrated mixer for A/D conversion of IF signals. IEEE Journal of Solid-State Circuits, 35(4), 468–475.

Cho, T. B., Gray, P. R. (1995). A 10 b, 20 Msample/s, 35 mW pipeline A/D converter. IEEE Journal of Solid-State Circuits, 30(3), 166–172.

Miller, M. R., Petrie, C. S. (2003). A multibit sigma-delta ADC for multimode receivers. IEEE Journal of Solid-State Circuits, 38(3), 475–482.

Matsukawa, K., Mitani, Y., Takayama, M., Obata, K., Dosho, S., Matsuzawa, A. (2010). A fifth-order continuous-time delta-sigma modulator with single-Opamp resonator. IEEE Journal of Solid-State Circuits, 45(4), 697–706.

Patón, S., Giandomenico, A. D., Hernández, L., Wiesbauer, A., Pötscher, T., Clara, M. (2004). A 70-mW 300-MHz CMOS continuous-time \(\Upsigma\Updelta\) modulator with 15-MHz bandwidth and 11 bits of resolution. IEEE Journal of Solid-State Circuits, 39(7), 1056–1063.

Yan, S., Sánchez-Sinencio, E. (2004). A continous-time \(\Upsigma\Updelta\) modulator with 88-dB dynamic range and 1.1-MHz signal bandwidth. IEEE Journal of Solid-State Circuits, 39(1), 75–86.

Li, Z., Fiez, T.S. (2007). A 14 Bit continuous-time delta sigma A/D modulator with 2.5 MHz signal bandwidth. IEEE Journal of Solid-State Circuits, 42(9), 1872–1883.

Shu, Y.-S., Tsai, J.-Y., Chen, P., Lo, T.-Y., Chiu, P.-C. (2013). A 28fJ/conv-step CT \(\Updelta\Upsigma\) modulator with 78 dB DR and 18 MHz BW in 28 nm CMOS using a highly digital multibit quantizer. ISSCC Digest of Technical Papers, Feb 9–13, pp. 268–269.

Matsukawa, K., Obata, K., Mitani, Y., Dosho, S. (2012). A 10 MHz BW 50 fJ/conv. continuous time \(\Updelta\Upsigma\) modulator with high-order single Opamp integrator using optimization-based design method. Proceedings of the 2012 Symposium on VLSI Circuits, Honolulu, Hawaii, June 13–15, pp. 160–161.

Taylor, G., Galton, I. (2013). A reconfigurable mostly-digital delta-sigma ADC with a worst-case FOM of 160 dB. IEEE Journal of Solid-State Circuits, 48(4), 983–995.

Dhanasekaran, V., Gambhir, M., Elsayed, M. M., Sánchez-Sinencio, E., Silva-Martinez, J., Mishra, C., Chen, L., Pankratz, E. J. (2011). A continuous time multi-bit \(\Updelta\Upsigma\) ADC using time domain quantizer and feedback element. IEEE Journal of Solid-State Circuits, 46(3), 639–650.

Prefasi, E., Paton, S., Hernandez, L. (2011). A 7 mW 20 MHz BW time-encoding oversampling converter implemented in a 0.08 mm2 65 nm CMOS circuit. IEEE Journal of Solid-State Circuits, 46(7), 1562–1574.

Reddy, K., Rao, S., Inti, R., Young, B., Elshazly, A., Talegaonkar, M., Hanumolu, P. K. (2012). A 16 mW 78 dB-SNDR 10 MHz-BW CT-\(\Updelta\Upsigma\) ADC using residue-cancelling VCO-based quantizer. IEEE Journal of Solid-State Circuits, 47(12), 2916–2927.

Zanbaghi, R., Hanumolu, P. K., Fiez, T. S. (2013). An 80-dB DR, 7.2-MHz bandwidth single Opamp biquad based CT \(\Updelta\Upsigma\) modulator dissipating 13.7-mW. IEEE Journal of Solid-State Circuits, 48(2), 487–501.

Jo, J.-G., Noh, J., Yoo, C. (2011). A 20-MHz bandwidth continuous-time sigma-delta modulator with Jitter immunity improved full clock period SCR (FSCR) DAC and high-speed DWA. IEEE Journal of Solid-State Circuits, 46(11), 2469–2477.

Jain, A., Venkatesan, M., Pavan, S. (2012). Analysis and design of a high speed continuous-time \(\Updelta\Upsigma\) modulator using the assisted Opamp technique. IEEE Transactions on Circuits and Systems, 47(7), 1615–1625.

Singh, V., Krishnapura, N., Pavan, S., Vigraham, B., Behera, D., Nigania, N. (2012). A 16 MHz BW 75 dB DR CT \(\Updelta\Upsigma\) ADC compensated for more than one cycle excess loop delay. IEEE Journal of Solid-State Circuits, 47(8), 1884–1895.

Gardner, F. (1986). A transformation for digital simulation of analog filters. IEEE Transactions on Communications., 1(1), 676–680.

Pavan, S. (2008). Excess loop delay compensation in continuous-time delta-sigma modulators. IEEE Transactions on Circuits and Systems II, 55(11), 1119–1123.

Acknowledgments

This work was funded by the European Union Seventh Framework Programme (FP7/2007–2013) under Grant agreement no. 248277.

Author information

Authors and Affiliations

Corresponding author

Appendix

Appendix

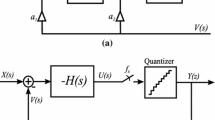

In this Appendix, the loop filter coefficients a i,ct of a 3rd-order CT DSM are derived from the loop filter coefficients a i,dt of a 3rd-order DT DSM. It is assumed that the DAC pulses (either NRZ or RZ) in the CT modulator can be delayed by up to one sampling period. The employed method is the impulse-invariant transformation [6, 45], in which the open-loop impulse response h ct (n) of the CT loop filter, sampled at the input of the quantizer, is mapped to the open-loop impulse response h dt (n) of the DT loop filter. The modulator sampling period T s is normalized to unity.Footnote 5

The a i,ct coefficients are needed to derive the general analytical expression for a 4ct , defined in (1) and used in Sects. 2 and 3.

The open-loop transfer function H dt (z) of the DT modulator is immediately found from Fig. 20, disregarding the g 1 feedback path Footnote 6, as

resulting in the time-domain open-loop impulse response of the DT loop filter equal to

For the CT modulator, the DACs are assumed to deliver rectangular pulses r α,β(t) of unit height, lasting from t/T s = α to t/T s = β (Fig. 1(e)). Thus, r α,β(t) is defined by

It is assumed that the current pulse starts in the first sampling period for all three DACs, and stops in the following sampling period at the latest, i.e.

In the Laplace domain, r α_i,β_i (t) becomes [6]

We proceed by deriving H ct (s), after which its inverse Laplace transform h ct (t) is computed and sampled at t = nT s . If β i > 1 for any of the DAC pulses, an additional parameter, γ i = min(β i , 1), is needed to handle correctly the first sample h ct (1) of the CT impulse response (i.e., for a DAC pulse with β i ≤ 1, γ i is equal to β i ; otherwise γ i = 1).

Following the same procedure as in [6], and referring to Fig. 2(b), the sampled impulse responses for DAC4, DAC3, DAC2, and DAC1 are

Obviously, h ct (n) is the sum of (9), (10), (11) and (12), which yields

valid only for the first sample, n = 1, and

valid for the remaining samples, n ≥ 2.

The CT coefficients a 1ct − a 3ct can now be found by setting h ct (n) in (14) equal to h dt (n) in (6), resulting in

while a 4ct is found by setting h ct (1) in (13) equal to h dt (1) in (6):

It is clear that the extra, fourth coefficient a 4ct is needed to match h ct (n) and h dt (n) at n = 1. Thus, the error \(\epsilon\) mentioned in Sect. 4 coincides exactly with a 4ct . In this work, α i = 0.25, and an RZ pulse for DAC3 well contained within the first sampling period (β3 = 0.75) is chosen, which makes a 4ct small enough to be omitted without compromising the modulator performance. The general analytical expression for a 4ct is found by inserting a 1ct − a 3ct from (15) into (16), which yields (1).

Rights and permissions

About this article

Cite this article

Andersson, M., Sundström, L., Anderson, M. et al. Theory and design of a CT \(\Updelta\Upsigma\) modulator with low sensitivity to loop-delay variations. Analog Integr Circ Sig Process 76, 353–366 (2013). https://doi.org/10.1007/s10470-013-0114-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-013-0114-y