Abstract

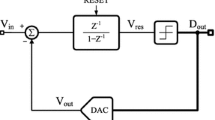

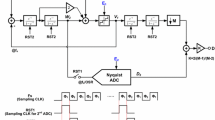

This paper describes an incremental converter based on a second order ΣΔ modulator. The scheme uses a 3-bit DAC with inherent linearity, an optimal reset of integrators, and gives rise to an effective offset cancellation with a novel technique based on single or double chopping. The circuit, fabricated in a mixed 0.18-0.6 μm CMOS technology, obtains 1.5-μV residual offset with 2VPP fully differential range. The measured resolution is 19 bit obtained with 512 clock periods.

Similar content being viewed by others

References

Robert, J., & Deval, P. (1988). A second-order high-resolution incremental A/D converter with offset and charge injection compensation. IEEE Journal of Solid-State Circuits, 23, 736741.

Markus, J., Silva, J., & Temes, G. C. (2004). Theory and applications of incremental ΣΔ converters. IEEE Transactions on Circuits and Systems-I, 51(4), 678–690.

Welz, J., & Galton, I. (2002). Necessary and sufficient conditions for mismatch shaping in a general class of multibit DACs. IEEE Transactions on Circuits and Systems-II, 49(12), 748–759.

Agnes, A., & Maloberti, F. (2004). High-order incremental converters with digital calibration. IEEE Proceedings of European Conference on Circuit Theory and Design, 51, 678–690.

Belloni, M., Della Fiore, C., Maloberti, F., Garcia-Andrade, M. (2007). On the design of incremental ΣΔ converters. In IEEE proceedings of northeast workshop on circuits and systems (pp. 1376–1379). Montreal: NEWCAS 2007.

Enz, C. C., & Temes, G. C. (1996). Circuit techniques for reducing the effects of op-amp imperfections: autozeroing, correlated double sampling, and chopper stabilization. Proceedings of IEEE, 84, 1584–1614.

Quiquempoix, V., Deval, P., Barreto, A., Bellini, G., Markus, G. J., Silva, J., et al. (2006). A low-power 22-bit incremental ADC. IEEE Journal of Solid-State Circuits, 41, 1562–1571.

Acknowledgments

The authors wish to thank Aldo Peña Perez of the Integrated Microsystems Laboratory, University of Pavia, for his help and National Semiconductors for chip fabrication. This study is partially funded by FIRB, Italian National Program, Project RBAP06L4S5.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Agnes, A., Bonizzoni, E. & Maloberti, F. High-resolution multi-bit second-order incremental converter with 1.5-μV residual offset and 94-dB SFDR. Analog Integr Circ Sig Process 72, 531–539 (2012). https://doi.org/10.1007/s10470-011-9752-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-011-9752-0