Abstract

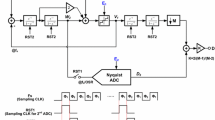

Alessandro.DAmato@ti.comThis paper describes a second-order 3-bit incremental converter, which employs a novel Smart-DEM algorithm to compensate for the mismatch among unity elements of the multi-level digital-to-analog converter. The design, which is fabricated in a mixed 0.18–0.5 \(\upmu\)m CMOS technology, achieves 16.7-bit resolution over a 5-kHz bandwidth by using 256 clock periods per sample. A single-step chopping technique leads to a residual offset of 9.7 \(\upmu\)V. The measured power consumption is 280 \(\upmu\)W and the achieved figure of merit is 174.95 dB.

Similar content being viewed by others

References

Wu, R., Chae, Y., Huijsing, J. H., & Makinwa, K. A. A. (2012). A 20-b ± 40 mV range read-out IC with 50-nV offset and 0.04 % gain error for bridge transducers. IEEE Journal of Solid-State Circuits, 47(9), 2152–2163.

Garcia, J., Rodriguez, S., & Rusu, A. (2013). A low-power CT incremental 3rd order \(\rm \Sigma \Delta\) ADC for biosensor applications. IEEE Transactions on Circuits and Systems - I, 60(1), 25–36.

Markus, J., Silva, J., & Temes, G. C. (2004). Theory and applications of incremental \(\Delta \Sigma\) converters. IEEE Transactions on Circuits and Systems I, 51(4), 678–690.

Robert, J., & Deval, P. (1988). A second-order high-resolution incremental A/D converter with offset and charge injection compensation. IEEE Journal of Solid-State Circuits, 23(3), 736–741.

Lyden, C., Ryan, J., Ugarte, C. A., Kornblum, J., & Yung, F. M. (1995). A single shot sigma delta analog to digital converter for multiplexed applications. In Proceedings of IEEE Custom Integrated Circuits Conference (CICC) (pp. 203–206).

Caldwell, T. C., & Johns, D. A. (2010). Incremental data converters at low oversampling ratios. IEEE Transactions on Circuits and Systems - I, 57(7), 1525–1537.

Agah, A., Vleugels, K., Griffin, P. B., Ronaghi, M., Plummer, J. D., & Wooley, B. A. (2010). A high-resolution low-power incremental \(\rm \Sigma \Delta\) ADC with extended range for biosensor arrays. IEEE Journal of Solid-State Circuits, 45(6), 1099–1110.

Quiquempoix, V., Deval, P., Barreto, A., Bellini, G., Markus, J., Silva, J., et al. (2005). A low-power 22-bit incremental ADC. IEEE Journal of Solid-State Circuits, 41(7), 1562–1571.

Baird, R. T., & Fiez, T. S. (1995). Linearity enhancement of multibit A/D and D/A converters using data weighted averaging. IEEE Transactions on Circuits and Systems I, 42, 753–762.

Agnes, A., Bonizzoni, E., & Maloberti, F. (2012). High-resolution multi-bit second-order incremental converter with 1.5-\(\upmu\)V residual offset and 94-dB SFDR. Analog Integrated Circuits and Signal Processing, Springer, 72, 531–539.

Liu, Y., Bonizzoni, E., D'Amato, A., & Maloberti, F. (2013). A 105-dB SNDR, 10 kSps multi-level second-order incremental converter with Smart-DEM consuming 280\(\upmu\)W and 3.3-V supply. In Proceedings of IEEE European Solid-State Circuits Conference (ESSCIRC) (pp. 371–374).

Liu, Y., Bonizzoni, E., & Maloberti, F. (2013). High-order multi-bit incremental converter with Smart-DEM algorithm. In Proceedings of IEEE International Symposium on Circuits and Systems (ISCAS) (pp. 157–160).

van de Plassche, R. J. (1978). A sigma-delta modulator as an A/D converter. IEEE Transactions on Circuits System, CAS–25(7), 510–514.

Lyden, C., Ryan, J., Ugarte, C. A., Kornblum, J., & Yung, F.-M. (1995). A single shot sigma delta analog to digital converter for multiplexed applications. In Proceedings of IEEE Custom Integrated Circuits Conference (CICC) (pp. 203–206).

Rombouts, P., De Wilde, W., & Weyten, L. (2001). A 13.5-b 1.2-V micropower extended counting A/D converter. IEEE Journal of Solid-State Circuits, 36(2), 176–183.

Chen, C.-H., Zhang, Y., Jung, Y., He, T., Ceballos, J. L., & Temes, G. C. (2013). Two-step incremental analogue-to-digital converter. Electronics Letters, 49(4), 250–251.

Chae, Y., Souri, K., & Makinwa, K. A. A. (2013). A 6.3\(\upmu\)W 20b incremental zoom-ADC with 6ppm INL and 1\(\upmu\)V offset. In IEEE International Solid-State Circuits Conference Digest of Technical Papers ( pp. 276–277).

Chen, C., Tan, Z., & Pertijs, M. A. P. (2013). A 1V 14b Self-timed zero-crossing-based incremental \(\rm \Sigma \Delta\) ADC. In IEEE International Solid-State Circuits Conference Digest of Technical Papers (pp. 274–275).

Silva, J., Moon, U., Steensgaard, J., & Temes, G. C. (2001). Wideband low-distortion delta-sigma ADC topology. IET Electronics Letters, 37(12), 737–738.

Assaad, R. S., & Silva-Martinez, J. (2009). The recycling folded cascode: A general enhancement of the folded cascode amplifier. IEEE Journal of Solid-State Circuits, 44(9), 2535–2542.

Schreier, R., & Temes, G. C. (2005). Understanding delta-sigma data converters. New York: Wiley.

Chen, C.-H., Zhang, Y., He, T., Chiang, P. Y., & Temes, G. C. (2014). A 11 \(\upmu\)W 250 Hz BW two-step incremental ADC with 100 dB DR and 91 dB SNDR for integrated sensor interfaces. In Proceedings of IEEE Custom Integrated Circuits Conference (CICC) (pp. 1–4).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Liu, Y., Bonizzoni, E., D’Amato, A. et al. A high-resolution low-power and multi-bit incremental converter with smart-DEM. Analog Integr Circ Sig Process 82, 663–674 (2015). https://doi.org/10.1007/s10470-015-0492-4

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-015-0492-4