Abstract

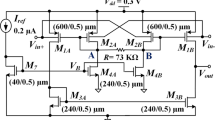

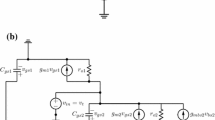

A tutorial of CMOS active resistor circuits will be presented in this paper. The main advantages of the proposed implementations are the improved linearity, the small area consumption and the improved frequency response. In order to improve their linearity, improved performances linearization techniques will be proposed, with additional care for compensating the errors introduced by second-order effects. Design techniques for minimizing the silicon area consumption will be further presented and FGMOS (Floating Gate MOS) transistors will be used for this purpose. The frequency response of the circuits is very good as a result of biasing all MOS transistors in the saturation region and of a current-mode operation of an important part of their blocks. Additionally, small changing in each design allows to obtain negative controllable equivalent resistance circuits. The circuits are implemented in CMOS technology, SPICE simulations confirming the theoretical estimated results, showing small values of the linearity error (under 0.15% for the best design) for an extended input range and for a supply voltage equal with ±3 V. The proposed circuits respond to low-voltage low-power requirements, their design being adapted to the continuous degradation of the model quality associated with the evolution toward latest nanotechnologies.

Similar content being viewed by others

References

Wang, Z. (1990). Current-controlled linear MOS earthed and floating resistors and application. In IEEE Proceedings on Circuits, Devices and Systems, ( pp. 479–481).

Sellami, L. (1997). Linear bilateral CMOS resistor for neural-type circuits. In Proceedings of the 40th Midwest Symposium on Circuits and Systems, (pp. 1330–1333).

Singh, S. P., Hansom, J. V., & Vlach, J. (1989). A new floating resistor for CMOS technology, IEEE Transactions on Circuits and Systems, (pp. 1217–1220).

Sakurai, S. & Ismail, M. (1993). A CMOS square-law programmable floating resistor, IEEE International Symposium on Circuits and Systems, (pp. 1184–1187).

Papazoglou, C. A. & Karybakas, C. A. (1999). Electronically tunable floating CMOS resistor independent of the MOS parameters and temperature, Proceedings of Electronics, Circuits and Systems, The 6th IEEE International Conference on ICECS, (pp. 311–314).

Ozalevli, E. & Hasler, P. (2005). Design of a CMOS floating-gate resistor for highly linear amplifier and multiplier applications, Custom Integrated Circuits Conference, 2005. Proceedings of the IEEE 2005, (pp. 735–738).

Kaewdang, K., Surakampontom, W., & Fujii, N. (2004). A design of CMOS tunable current amplifiers, Communications and Information Technology, 2004. ISCIT 2004. IEEE International Symposium, (pp. 519–522).

Bahmani, F., & Sanchez-Sinencio, E. (2004). A highly linear pseudo-differential transconductance, Solid-State Circuits Conference, 2004. ESSCIRC 2004. Proceeding of the 30th European, (pp. 111–114).

Popa, C. (2006). Improved linearity active resistor with controllable negative resistance, International Conference on IC Design and Technology, Padova, Italy, (pp. 1–4).

Popa, C. (2006). A new multisign resistance FGMOS active resistor with improved linearity, International Conference on Signals and Electronic Systems, ICSES 2006, Lods: Polonia.

Popa, C., & Manolescu, A. M. (2007). CMOS differential structure with improved linearity and increased frequency response, 30th Edition Annual Semiconductors Conference (CAS 2007), Sinaia, Romania, (pp. 517–520).

Popa, C. (2006). A new FGMOS active resistor with improved linearity and increased frequency response, IEEE Conference on Microelectronics, Electronics and Electronic Technologies, Opatija, Croatia, (pp. 84–87).

Popa, C. (2004). Low-area CMOS active resistor independent on the bulk effect, IEEE-TTTC International Conference on Automation, Quality & Testing, Robotics AQTR 2004 (THETA 14), Cluj-Napoca, Romania, (pp. 285–290).

Popa, C., Mitrea, O., Manolescu, A. M., & Glesner, M. (2002). Low-power CMOS active resistor independent on the threshold voltage, The 9th IEEE International Conference on Electronics, Circuits and Systems, ICECS Dubrovnik, Croatia, (pp. 57–60).

Tajalli, A., et al. (2008). Implementing ultra-high-value floating tunable CMOS resistors. Electronics Letters, 44, 349–350.

Seevinck, E., & Wassenaar, R. (1987) A versatile CMOS linear transconductor/square-law circuit, IEEE Journal of Solid State Circuits, vol. SC-22, June 1987, (pp. 366–377).

Wilson, G., & Chart, P. K. (1993). Floating CMOS resistor, Electronic Letters, 306–307.

Singh, S. P., Hanson J. V. & Vlach, J. A. (1989). New CMOS floating resistor for CMOS technology, IEEE Trans., CAS, 36, (pp. 1217–1220).

Sakurai, S., & Ismail, M. A. (1992). CMOS square-law programmable floating resistor independent of the threshold voltage, IEEE Trans., CAS-II-39, (pp. 565–574).

Elwan, H. O., Mahmoud, S. A., & Soliman, A. M. (1996). CMOS voltage-controlled floating resistor. International Journal of Electronics, 81, 571–576.

Mahmoud, S. A., Elwan, H. O., & Soliman, A. M. (1997). Generation of CMOS voltage-controlled floating resistors. Microelectronics Journal, 28, 627–640.

Kaewdang, K., Kumwachara, K., & Surakampontorn, W. (2005). Electronically tunable floating CMOS resistor using OTA, Communications and Information Technology, 2005. ISCIT 2005. IEEE International Symposium, Vol 1, (pp. 729–732).

Mahmoud, S. A. (2004). A low voltage CMOS floating resistor, electrical, electronic and computer engineering, 2004. ICEEC ‘04. 2004 International Conference, (pp. 453–456).

Vavelidis, K., & Tsividis, Y. (1993). R-MOSFET structure based on current division. Electronics Letters, 29, 732–733.

Vavelidis, K., Tsividis, Y. P., Op’t Eynde, F., & Papananos, Y. (1997). Six-terminal MOSFET’s: Modelling and applications in highly linear, electronically tunable resistors. IEEE Journal of Solid-State Circuits, 32, 4–12.

Muniz-Montero, C., Gonzalez-Carvajal, R., Diaz-Sanchez, A., & Rocha, J. M. (2007). Low frequency, current mode programmable KHN filters using large-valued active resistors, Circuits and Systems, 2007. ISCAS 2007. IEEE International Symposium, (pp. 3868–3871).

Sanchez-Rodriguez, T., Lujan-Martinez, C., Carvajal, R., Ramirez-Angulo, J., & Lopez-Martin, A. (2008). CMOS Linear programmable transconductor suitable for adjustable Gm-C filters. Electronics Letters, 44(8), 505–506.

Acknowledgments

The authors thank the Romanian Higher Education Research National Council for financial (Research Projects ID_916 and ID_1045).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Manolescu, A., Popa, C. Low-voltage low-power improved linearity CMOS active resistor circuits. Analog Integr Circ Sig Process 62, 373–387 (2010). https://doi.org/10.1007/s10470-009-9351-5

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-009-9351-5