Abstract

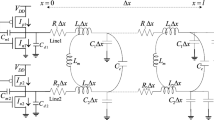

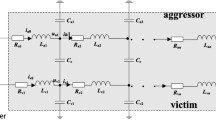

This work proposes a novel and accurate crosstalk noise estimation method in the presence of multiple RC lines for use in design automation tools. Using the realistic exponential waveform and a reduced transfer function, the proposed model presents a complete multiline noise model by representing active and passive aggressors simultaneously on the victim line. In the model, active aggressors are easily represented by current sources and passive aggressors are accurately modeled as equivalent capacitances to victim. Each current source representing an active aggressor carries the same accuracy as the 2-π representation. Equivalent capacitances for passive aggressors, on the other hand, consider resistive shielding effect and the realistic exponential aggressor waveform. This approach allows one to obtain a general noise model that considers the effect of many active and passive aggressors and general formulas derived can easily be applied to real cases. Noise peak and width expressions are derived and results are in good agreement with HSPICE results. Results show that average error for noise peak is 4.3% and for the width is 6.9% while allowing for very fast analysis.

Similar content being viewed by others

References

Vittal, A., & Marek-Sadowska, M. (1997). Crosstalk reduction for VLSI. IEEE Transactions on Computer-Aided Design, 16, 1817–1824.

Kahng, A. B., Muddu, S., & Vidhani, D. (1999). Noise and delay uncertainty studies for coupled RC interconnections. In IEEE Int. ASIC/SOC Conf., pp. 3–8.

Nakagawa, S., Sylvester, D. M., McBride, J., & Oh, S.-Y. (1998). On-chip crosstalk noise model for deep submicrometer ULSI interconnect. H. P. Journal, 49, 39–45.

Cong, J., Pan, D. Z., & Srinavas, P. V. (2001). Improved crosstalk modeling for noise constrained interconnect optimization. In Proceedings of ASP/DAC, pp. 373–378.

Becer, M. R., Blaauw, D., Zolotov, V., Panda, R., & Hajj, I. N. (2002). Analysis of noise avoidance techniques in DSM interconnects using a complete crosstalk noise model. In Design, Automation and Test in Europe Conference, pp. 456–464.

Sato, T., Cao, Y., Agarwal, K., Sylvester, D., & Hu, C. (2003). Bidirectional closed-form transformation between on-chip coupling noise waveforms and interconnect delay change curves. IEEE Transactions on Computer-Aided Design, 22(5), 560–572. doi:10.1109/TCAD.2003.810750.

Agarwal, K., Cao, Y., Sato, T., Sylvester, D., & Hu, C. (2002). Efficient generation of delay change curves for noise-aware static timing analysis. In Proc. of Asia and South Pac. Design Automation Conf., pp. 77–84.

Kuhlmann, M., Sapatnekar, S. S., & Parhi, K. K. (1999). Efficient crosstalk estimation. In International Conference on Computer Design (ICCD ‘99), pp. 266–272.

Levy, R., Blaauw, D., Braca, G., Dasgupta, A., Grinshpon, A., Oh, C., Orshav, B., Sirichotiyakul, S., & Zolotov, V. (Nov, 2002). Clarinet: A noise analysis tool for deep submicron design. In Proc. Int. Conf. Computer-Aided Design, pp. 587–594.

Qian, J., Pullela, S., & Pillage, L. T. (1994). Modeling the effective capa- citance for the RC interconnect of CMOS gates. IEEE Transactions on Computer-Aided Design, 13, 1526–1535. doi:10.1109/43.331409.

Pillage, L. T., & Rohrer, R. A. (1990). Asymptotic waveform evaluation for timing analysis. IEEE Transactions on Computer-Aided Design, 9(4), 352–366. doi:10.1109/43.45867.

Acar, E., Odabasioglu, A., Celik, M., & Pileggi, L. (1999). S2p: A stable 2- pole RC delay and coupling noise metric IC interconnects. Proceedings 9th Great Lakes Symposium on VLSI, pp. 60–63.

Sabet, P. B., & Ilponse, F. (2001). a model for crosstalk evaluation in deep submicron processes. ISQED, 2001. pp. 139–144, Sd.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Sayıl, S., Borra, U.K. A multiline model for time-efficient estimation of crosstalk. Analog Integr Circ Sig Process 59, 65–75 (2009). https://doi.org/10.1007/s10470-008-9237-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-008-9237-y