Abstract

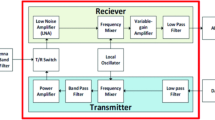

Digital down converter (DDC) is one of the crucial components in digital radio receiver. The working function of DDC is to convert the frequency translation from Intermediate Frequency (IF) band to baseband signal. This paper briefs a hardware efficient DDC architecture which is made of COordinate Rotation Digital Computer (CORDIC) processor act as a digital oscillator followed by multi-stage Cascaded Integrator Comb (CIC) performs as a high rate decimation filter and then Multi-channel Systolic Finite Impulse Response (MSFIR) decimation filter allows perfect output. All of these components of the proposed DDC architecture have been designed in Xilinx ISE 14.7 simulator using optimization techniques and targeted to the Xilinx Kintex-7 Field Programmable Gate Array (FPGA) device. Implementation of DDC on FPGA provides high flexibility, moderate cost and customizability. The result analysis of the proposed DDC model is superior to the similar design with regard to area, operating speed and power consumption. The implemented DDC design is used to transform input bandwidth from about 70 MHz to 137 kHz, matching in Software Defined Radio (SDR) system requirements.

Similar content being viewed by others

References

Agarwal A, Boppana L, Kodali R (2014) A fractional sample rate conversion filters for a software radio receiver on FPGA. IEEE Xplore. https://doi.org/10.1109/TENCON.2014.7022456

Altera Corporation (2017) AN639: Inferring stratix V DSP blocks for FIR filtering applications

Chandra A, Chattopadhyay S (2016) Design of hardware efficient FIR filter: a review of the state-of-the-art approaches. Eng Sci Technol Int J 19(1):212–226. https://doi.org/10.1016/j.jestch.2015.06.006

Das S, Maity R, Maity NP (2018) VLSI-based pipeline architecture for reversible image watermarking by difference expansion with high-level synthesis approach, circuit. Circuit Syst Signal Process 37(4):1575–1593

Datta D, Mitra P, Dutta HS (2019) Implementation of universal modulator using CORDIC architecture in FPGA. In: Mandal J, Mukhopadhyay S, Dutta P, Dasgupta K (eds) Computational intelligence, communications, and business analytics. CICBA 2018. Communications in computer and information science, vol 1030, chapter 34. Springer, Singapore, pp 434–441. https://doi.org/10.1007/978-981-13-8578-0_34

Dhar AS, Lakshmi B (2010) CORDIC architectures: a survey. VLSI Des. https://doi.org/10.1155/2010/794891

Fei-yu L, Wei-ming Q, Yan-yu W, Tai-lian L, Jin F, Jian-chuan Z (2009) Efficient WCDMA digital down converter design using system generator. In: IEEE international conference on space science and communication, 2009, pp 89–92

Ghani U, Wasim M, Khan US, Saleem MM, Hassan A, Rashid N, Tiwana M, Hamza A, Kashif A (2018) Efficient FIR filter implementations for multichannel BCIs using Xilinx system generator. BioMed Res Int. https://doi.org/10.1155/2018/9861350

Hatai I, Chakrabarti I (2011) A new high-performance digital FM modulator and demodulator for software-defined radio and its FPGA implementation. Int J Reconfig Comput. https://doi.org/10.1155/2011/342532

Hogenauer EB (1981) An economical class of digital filters for decimation and interpolation. IEEE Trans Acoust Speech Signal Process 29(2):155–162

Jing Q, Li Y, Tong J (2019) Performance analysis of multi-rate signal processing digital filters on FPGA. EURASIP J Wirel Commun Netw. https://doi.org/10.1186/s13638-019-1349-9

Liu C, Wang Y (2015) A 128-channel, 710 M samples/second, and less than 10 ps RMS resolution time-to-digital converter implemented in a Kintex-7 FPGA. IEEE Trans Nucl Sci. https://doi.org/10.1109/tns.2015.2421319

Liu X, Yan X, Wang Z, Deng Q (2017) Design and FPGA implementation of a reconfigurable digital down converter for wideband applications. IEEE Trans VLSI Syst 25(12):3548–3552

Loehning M, Hentschel T, Fettweis G (2000) Digital down conversion in software radio terminals. In: 10th European signal processing conference, vol. 3, 2000, Finland

Meher P, Chandrasekaran S, Amira A (2007) FPGA Realization of FIR filters by efficient and flexible systolization using distributed arithmetic. IEEE Trans Signal Process 56(7):3009–3017. https://doi.org/10.1109/TSP.2007.914926

Obradović V, Okiljević P, Kozić N, Ivković D (2016) Practical implementation of digital down conversion for wideband direction finder on FPGA. Sci Tech Rev 66(4):40–46

Park YS (2015) A low-cost FPGA implementation of multi-channel FIR filter with variable bandwidth. IEICE Electron Express. https://doi.org/10.1587/elex.12.20150702

Park SY, Meher PK (2014) Efficient FPGA and ASIC realizations of a DA-based reconfigurable FIR digital filter. IEEE Trans Circuits Syst II 61(7):511–515

Volder JE (1959) The CORDIC trigonometric computing technique. IRE Trans Electron Comput 8:330–334

Wolf W (2004) FPGA-based system design. Prentice-Hall, Englewood Cliffs

Zhang Q, Su X (2012) The design of digital down converter based on FPGA. In: 8th Internatinal conference on wireless communications, networking and mobile computing, IEEE Xplore, Shanghai, China. https://doi.org/10.1109/WiCOM.2012.6478707

Zhang C, Zhang L (2016) Intermediate frequency digital receiver based on multi-FPGA system. J Electr Comput Eng. https://doi.org/10.1155/2016/6123832

Acknowledgements

The authors would like to thank Brainware Group of Institutions and Kalyani Government Engineering College for providing the ISE design suite 14.7 and Xilinx FPGA device.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Datta, D., Mitra, P. & Dutta, H.S. FPGA implementation of high performance digital down converter for software defined radio. Microsyst Technol 28, 533–542 (2022). https://doi.org/10.1007/s00542-019-04579-w

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00542-019-04579-w